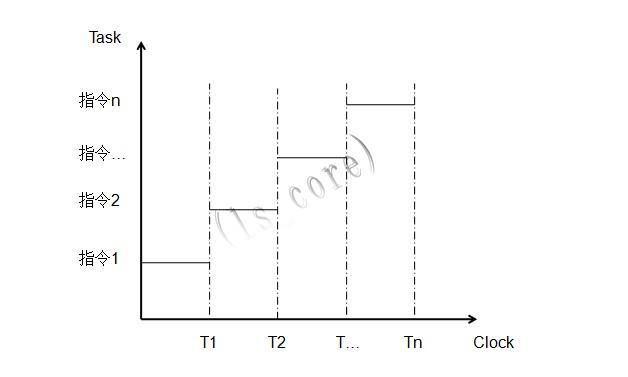

把MSP430G2553的系統(tǒng)時鐘作為系統(tǒng)學習的一篇講解可見他的重要性,那為什么要把時鐘放到第一位呢?學過FPGA的朋友都能體會得到,如果把CPU的所有工作任務作為縱坐標(y軸),那么時鐘就是他的橫坐標(x軸)了,如下圖1 時鐘概念所示。

圖 1 時鐘概念

也就是說時鐘就是一個微機(小到8位的51單片機大到32位的S3C2440等)在時域上的一個衡量標準。如果學過FPGA的朋友都很清楚,微機是以對輸入的時鐘源的脈沖計數(shù)的方式來確定時域參數(shù)的。所以,MSP430單片機也一樣,拿到他之后首先從時鐘入手,一定要養(yǎng)成這種系統(tǒng)學習的好方法,否則再學一百款單片機也是感覺再學新的,做不到舉一反三,事半功倍的效果。如果能夠把握這其中的通理,你會有所有的單片機都一樣樣的感覺,當然學起來也就游刃有余了。廢話不多說了,進入正題。

一 、硬件

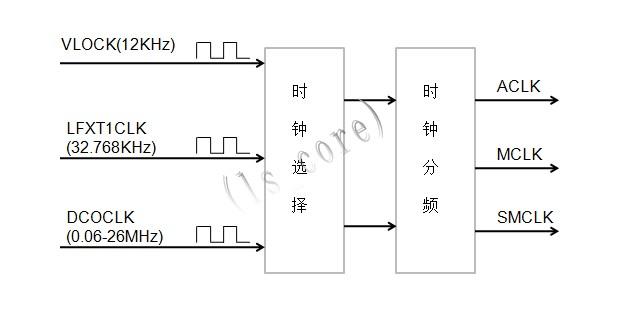

Msp420g2553的系統(tǒng)時鐘是由VLOCK、LFXT1CLK和DCOCLK組成,如下圖2 系統(tǒng)時鐘組成所示:

圖2 系統(tǒng)時鐘組成

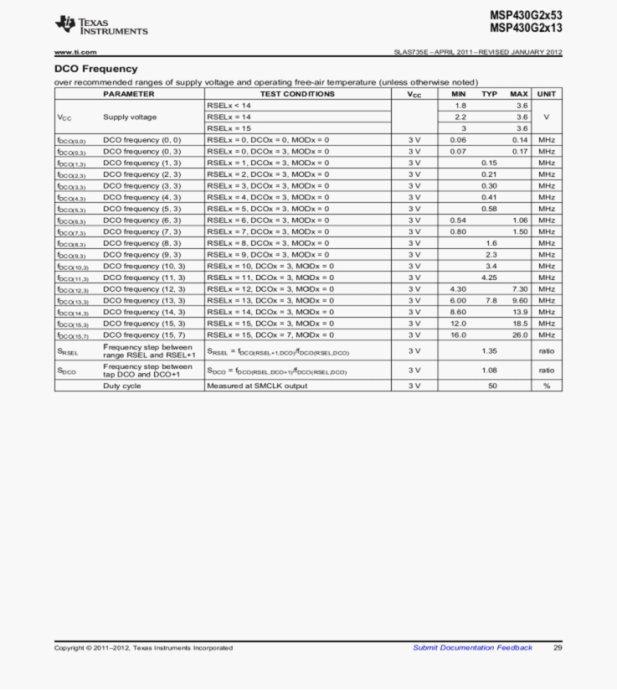

即2553的系統(tǒng)時鐘源有三個分別是片內(nèi)超低功耗12KHz的內(nèi)部振蕩器;由外部時鐘源提供的LFXT1CLK時鐘源,也即LanuchPad開發(fā)板上未焊接的時鐘電路,在這里我們可以焊接一個32.768KHz的低頻時鐘晶體由2553的XIN引腳輸入;片內(nèi)可數(shù)字控制的振蕩器DCOCLK,在軟件的調(diào)節(jié)下該時鐘的輸出范圍為0.6MHz到26MHz。在這三個時鐘源的獨立工作或是在三個時鐘源相互協(xié)調(diào)配合(是可以通過軟件配置的)下為2553系統(tǒng)提供了系統(tǒng)時鐘ACLK、MCLK和SMCLK。

ACLK為輔助時鐘,由軟件選擇來自VLOCK、LFXT1CLK之一經(jīng)過1,2,4,8分頻之后得到,為外圍模塊提供時鐘源。

MCLK為主時鐘,由軟件選擇來自VLOCK、LFXT1CLK和DCOCLK之一經(jīng)過1,2,4,8分頻之后得到,為CPU和系統(tǒng)提供時鐘。

SMCLK為子系統(tǒng)時鐘,由軟件選擇來自VLOCK、LFXT1CLK和DCOCLK之一經(jīng)過1,2,4,8分頻之后得到,為外圍各個模塊提供時鐘。