ӛ��ijλ�W�������f�^���W���κ�һ���Ƭ�C������Ҫ�W�������ĕr犡��Ĵ_��ˣ��r�����˵���Ҫ���ڲ�֪��ϵ�y�r犵���r�����X��ʲô�¶������Ժ����ġ�

֮ǰ�W�^51�����ĕr犺ܺ�������һ���ⲿ������Ȼ��W��430��G2553�����ĕr犾����c�韩�ˣ��r�Դ��(�ɂ��ⲿ������һ���Ȳ������ĵ��l��ʎ����һ���Ȳ��{�����l������ʎ��)���Ȳ�߀���i�l�h�����ҳ����ĕr�߀�ܱ����l��ԭ����TI�����������횵��и��N�l�ʁ�M���OӋ��Ҫ���������l��Խ�ͣ�����Խ����

�F�ڵ���430��F5529����G2553������Ҳ����Ҫ���õĕr����P�ļĴ�������3������…߀�Ђ�PMM(�Դ����ģ�K)������…

������PMM�Ǹ�����أ�߀���Ǿ�Ԓ��TI�����ġ�PMM���H����ˌ��Դ���O�ܺͱO�y(�@�傀�ְ�����̫��ă���…����������������)��߀���Ñ��ṩ�˸��ĺ���늉�(VCORE)��;������֪��������һ��ϵ�y���϶�Ҫ��늵���5529�Ќ����Դ(DVCC)늉�����1.8V-3.6V��DVCC���͉���늉��{����(LDO)���a����һ�����κ���늉������T��CPU����߉���������1.4V(0-12MHZ),1.6V(0-16MHZ),1.8V(0-20MHZ)��1.9V(0-25MHZ)�Ă����e����ϵ�y��Ҫ�ĕr��l�ʲ��ߕr���҂��������õ͵ĕr����������õ͵�VCORE���@���ڕr犷���Ͱѹ��Ľ������������Ȼ��������HAL_PMM.c/h����SetVCore(uint8_t level) ���p�p���ɵؾͿ����O��VCORE����

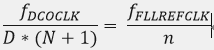

��������������ĕr����������W�^����߉�·���������l��ԓ����Ϥ���DZ��l�����i�l�h(FLL)������ʲô��߀�н������ᵽ���i��h(PLL)����ʲô�����������ֵĶ���һЩİ�������~���i�l�h�����˼�x������ʹ�ɂ���̖���l�����_��ij�N�Pϵ�����@�ɂ���̖��һ��������ݔ��r犵�����̖(�����f�ˣ����l�������F��)����һ��������ݔ���r犵�����̖���F���ٿ����ęn�o���Ĺ�ʽ��

��D*(N + 1)Խ��ĕr����fDCOCLKҲ��Խ���ˣ��Ķ�Ҳ���_���˱��l�����������i��h��ԭ��Ҳ����ƿ����уɂ���̖����λ�i������������l��Ҳ������������@�ɂ���̖ͬ����ݔ���ݔ���r犵�����̖�����Ҷ��������ķ��l��������ô�i�l������i�࣬�Д����b�l���������b�������ټ��Ϸ���(�f�������Σ�������Ҷ��IJ���…)��

1.

2.

3.

4.

5.

6.