10 ANALOG - TO - DIGTAL CONVERTERS WITH SERIAL CONTROL

引腳圖:

TLC 1549 可有六種工作時序 ,主要是考慮硬件SPI 接口的速度,因為硬件實現的SPI必須按字節讀寫,而1549是10位AD轉換器,所以要讀取轉換結果必須按兩字節既16位操作,故出現了那么多工作模式。當采用軟件模擬SPI時序時,就不必考慮區分這6種模式了。

采用GPIO產生控制時序通常采用10時鐘周期模式,

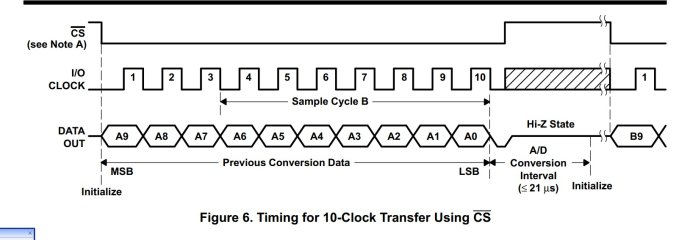

10 時鐘轉換 使用CS

10時鐘不適用 CS

由上圖所示、當CS 下降沿和第一個周期的下降沿讀取高兩位,其余8個周期用于讀取低8位。從第3個周期下降沿到第10個周期下降沿為片內采樣周期,然后從第10個周期下降沿開始后的21us 為轉換周期,片選信號CS 通常采用轉換期間無效模式,既在轉換過程中把 拉高CS (Figure 6).這是考慮到芯片的功耗問題,因為使能芯片比禁止芯片功耗要多出許多,這一點可直接從1549的datasheet中看出。

從控制時序圖中可以看出,一個完整AD 轉換周期包括讀取、采樣和量化(轉化)三個過程周期,而且讀取周期和采樣周期部分是重疊的,另外1549轉換的一個重要特點是讀取的數據是上次啟動AD轉換的結果,這就帶來一個問題,1549上電后第一次轉換如何處理?

顯然芯片上電復位后,輸出寄存器內容并非某次AD轉換結果,可能是一個隨機數或某個常數,若直接進行轉換,首次讀出的數據當然是錯誤的,不過可以采用初始化的方法確保首次讀出的數據為第一次啟動AD轉換的結果,具體方法是,在上電后首次執行一個初始化函數ADCClnit(),在函數中輸出10個周期脈沖,在第10個脈沖的下降沿,AD轉換被啟動,然后等待21us ,最后才進入正常的AD轉換程序,以后的讀取的數據就可以確定是AD轉換的真實值了。

在實際數據采集過程中,

description

The TL1549,TLC1591,and TLC1549M are 10-bit,switched-capacitor,successive-approximation(連續近似的)analog-to-digital converters.these devices have two digital inputs and 3-state output [chip select (cs低電平有效) ,input-output clock (I/O clock),and data output (DATA OUT)] that provide a three-wire interface to the serial port of a host processor.

The sample-and-hold function is automatic . The converter incorported in these devices features differentil high-impedance reference inputs that facilitate ratiometric conversion,scaling(比例),and isolation(絕緣) of analog ciruitry from logic and supply noise.a switched-capacitor (轉換電容器) design allows low-error converson over th full operating free-air temperature range.

The TLC1549C is characterized for operation from 0度 to 70度 。The TLC15491 is characterized for operation from -40 度 to 85度. The TLC 1549M is characterized for operation over the full military temperature range of -55度 to 125度。

detailed description

with chip select (cs) inactive (high),I/O clock is initially disabled and DATA OUT is in the high-impedance state. When the serial interface takes cs active (low ),the cnversion sequence begins with the enabling of I/O clock and the removal of DATA OUT from the high-impedance state.the serial interface then provides the I/O clock sequence to I/O clock and receives the previous conversion result fro DATA OUT .I/O clock receives an input sequence that is between 10 and 16 clock long from the host serial interface .the first ten I/O clocks provide the control timing for sampling the analog input.

there are six basic serial interface timign modes that can be used with the TLC1549. These modes are determined by the speed of I/O clock and the operation of cs shown in Table .these modes are(1) a fast mode with a 10 clock transfer and cs inactive (high ) between transfers,(2)a fast mode with a 10-clock transfer and cs active (low) continuously,(3) a fast mode with an 11-to 16 clock transfer and cs inactive (high) between transfes ,(4) a fast mode with a 16-bit transfer and cs active (low) continuously,(5) a slow mode with an 11 - to 16 -clock transfer and cs inactive (high)between transfers,and(6)a slow mode with a 16 -clock transfer and cs active(low)continuously.

The MSB of the previous conversion appears on DATA OUT on the falling edge of cs in mode 1,mode 3,and mode 5,withi 21 us from the falling edge of the tenth I/O clock in mode 2 and mode 4,and following the sixteenth clock falling eddge in mode 6.the remaining nine bits are shifted out on the next nine falling edges of I/O clock .Ten bits of data are transmitted to the host serial intrface through DATA OUT.The number of serial clock pulses used also depends on the mode of operation,but a minimum of ten clock pulses is required for conversion o begin.on the tenth clock falling edge,the internal logic takes DATA OUT low to ensure that the remaining bit values are zero if the I/O clock transfer is more than ten clocks long.