|

為了解決在 FPGA 上實現波形可移植性的問題,本文首先提出了一種基于 FPGA 的波形可移植性設計方法。在 FPGA 上實現了抽象層平臺的結構化,進而改進了標準的消息格式。最后,本文討論了連接模型對硬件抽象層的影響,平臺的資源消耗及工作效率,并進行抽象層比較多對一的連接模型與一對一的連接模型,得出的結論是,一對一連接模式更合適,FPGA 上的抽象層平臺完全解決了波形可移植性這個問題,包括大大降低成本的軟件定義開發無線電系統,提高軟件無線電系統的可重構性。

軟件無線電的概念是由 Joe Mitola 于1992年提出的,目的是提供一個支持多信道、多標準的可重構通信平臺。軟件無線電的主要思想是構建一個開放、標準化、模塊化的通用硬件平臺,通過加載不同的波形實現不同的通信模式和功能。波形的可移植性可以降低系統開發成本,有效地提高平臺的可重構性,因此波形的可移植性一直是軟件無線電系統開發者追求的目標。 隨著高速數字信號處理技術的發展,FPGA 在軟件無線電系統中得到了廣泛的應用。 文獻[1]中提出的軟件通信體系結構(SCA) ,使用CORBA 中間件有效地解決了通用處理器(GPP)上的波形可移植性問題,但 CORBA 是一種適用于 GPP 的技術,目前在 FPGA 上的應用較少。 目前,FPGA 的波形可移植性問題已成為國內外研究的熱點。 為了解決軟件無線電波形在 FPGA 上的可移植性問題,提出了軟件無線電波形可移植性的軟件體系結構,以滿足軟件無線電波形可移植性的要求。該結構的核心思想是在波形和硬件平臺之間建立一個抽象層平臺。 Pal 為波形提供了一個標準的、即時的執行期函式庫,屏蔽了硬件的差異,從而實現了波形的可移植性。 2. 背景和相關工作

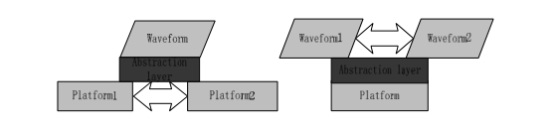

波形可移植性可以定義為將同一波形從一個平臺移植到另一個平臺的能力,而平臺的可重構性對應于 SDR 平臺承載不同波形的能力,如圖1所示。 從圖1可以很容易地得出這樣的結論: 如果在平臺和波形之間可以實現 PAL 制,從而消除了平臺和波形之間的耦合,不僅可以實現波形的可移植性,而且可以實現平臺的可重構性。 Pal 為波形提供了標準的執行期函式庫,執行期函式庫指的是周圍的執行環境,包括三個方面: 1)調用和控制組件; 2)提供本地服務和3)標準的通信環境。圖1. a)可移植性概念圖; b)可重構性概念圖 基于這一思想,硬件抽象層層連接(HAL-C)的概念在參考文獻[2]中被提出。 定義了波形和平臺之間的通信接口原型,標準化了波形和平臺之間的通信環境,但是由于上述通信環境只是波形執行期函式庫的一部分,因此,硬件抽象層層的連接只是部分解決了波形在 FPGA 上的可移植性問題。 2005年5月下旬,JPO 發布了專用硬件處理器組件可移植性擴展(Extension for component portability for Specialized Hardware Processors,SHP)-Change Proposal 289(CP289)[3] ,并提出了容器的概念。波形可移植性可以通過實現一個提供即時運行時的容器來實現在 FPGA 上實現波形環境。 這個想法很好,但是如何設計容器結構和如何提供一個標準的執行期函式庫仍然是一個問題,CP289不能解決這個問題。 目前相關的研究集中在如何實現硬件抽象層層連接上,Eric 為 DSP 提出了一種 PAL 結構,但這種結構并不適合 FPGA。 3.1. 結構 Fpga 的 PAL 制式結構如圖2所示。 Pal 制式由互連模塊、消息解析模塊、消息打包模塊、設備 IO 驅動程序的消息接收模塊、設備 IO 驅動程序的消息發送模塊和本地服務模塊組成。 每個 FPGA 芯片都有一個平臺抽象。 圖2. 平臺抽象層結構 設備 IO 驅動程序的消息接收模塊從物理信道接收消息,不同的物理信道對應于設備 IO 驅動程序的不同消息接收模塊。 設備 IO 驅動程序的消息發送模塊向物理信道發送消息,不同的物理信道對應設備 IO 驅動程序的不同消息發送模塊。 消息解析模塊解析從設備 IO 驅動程序接收的消息,并將解析后的消息提交到互連模塊。 消息封裝模塊封裝從互連模塊接收的消息,并將已封裝的消息提交到設備 IO 驅動程序的消息發送模塊。 互連模塊控制和維護可能在同一芯片或不同芯片上的不同組件之間的通信,分發由消息解析模塊提交的數據消息,并根據消息解析模塊提交的控制消息調用正確的組件接口來控制組件。 本地服務模塊提供重置服務、時鐘服務和本地存儲服務。 組件與互連模塊之間的接口采用標準的開放核心協議(OCP)接口,組件可以統一使用 PAL 提供的通信環境和本地服務,PAL 也可以統一調用和控制組件。基于所有這些,組件和平臺之間的耦合被解耦,因此成為組件具有輕便性。 由于波形由多個元件組成,所以波形具有可移植性。 3.2. 消息格式 為了實現不同 FPGA 芯片之間的互連和互通,采用統一的報文格式是需要的。 參考文獻[9]中定義了用于在 SHP 之間傳輸消息的標準消息格式,如圖3所示 圖三.標準訊息格式 消息 IU 位用于共享內存的數據接收器和數據源,不適用于不共享內存的處理器。 邏輯目的地(LD)用于將消息路由到目的地數據接收器。每個目標數據接收器都與一個邏輯目的地相關聯。 長度用于表示整個信息。 有效負載是消息的有效負載。 標準消息格式存在兩個不足。 首先,標準消息格式不區分不同的消息類型。 不僅需要不同組件之間的數據報文通信,而且還需要控制報文通信。 此外,請求消息和響應消息必須加以區分。其次,標準消息格式的通信地址設計降低了組件的重用能力。 如果僅僅使用邏輯目的地來區分 FPGA 芯片上不同組件的不同數據接收接口,同一 FPGA 芯片上所有組件的所有數據接收接口的邏輯目的地必須是不同的,但是組件開發人員只能確保所開發組件的數據接收接口的邏輯目的地是不同的,而不能保證所開發組件的數據接收接口的邏輯目的地與其他開發人員所開發組件的數據接口的邏輯目的地是不同的。 因此,當重用組件時,一個數據接收器接口的邏輯目的地可能與其他接口相同,組件重用失敗。 僅使用邏輯目的地指示通信地址將降低組件的重用能力。 為了彌補標準消息格式的不足,本文設計了新的請求消息格式和響應消息格式的標準消息格式,如圖4所示。 在請求消息中,目標地址用于指示目標處理器的地址。 Source Address 用于指示源處理器的地址。 目標 LD 用于指示目標組件的地址。 Message Type 用于指示消息是請求消息或響應消息。 響應標志用于指示消息是否需要響應消息。 源 LD 用于指示源組件的地址。 命令用于指示組件數據接口或組件控制接口的地址。 “參數列表”用于指示命令的參數列表。 在響應消息中,“回復狀態”用于指示是否發生任何異常。 響應消息中的其他字段與請求消息中的字段相同。 在新的請求消息格式和響應消息格式中,通信地址由處理器地址、組件地址和接口地址表示。 與圖3所示的舊的通信地址格式相比,新的通信地址格式具有兩大優勢。 首先,屬于一個組件的接口的尋址獨立于屬于其他組件的接口的尋址,從而提高了組件的重用能力。 其次,原有的通信地址在消息路由方面導致了設備驅動程序開發與 PAL 制開發的耦合,而新的分段式通信地址使耦合度降低。 設備驅動程序開發人員只需密切關注組件的地址,而 PAL 制式開發人員只需密切關注組件的地址和接口地址,因此降低了開發的復雜性。 圖4.請求 / 響應消息格式 3.3. 連接模式

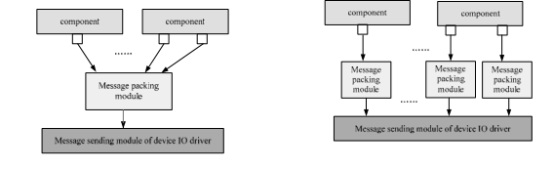

組件接口與消息封裝模塊之間的連接模型是 PAL 設計中的一個重要問題,它直接影響到 PAL 的資源消耗和工作效率。 有兩種不同的連接模型。 一種是多對一連接模型,即所有需要與其他處理器上的其他組件進行通信的接口都連接到同一個消息封裝模塊,如圖5所示。 另一種是一對一的連接模型,不同的接口對應不同的消息封裝模塊,如圖5所示。 圖5. a)多對一連接模式 b)一對一連接模式 與一對一連接模式相比,多對一連接模式存在兩個不足。 首先,多對一連接模型需要兩級緩沖區,因此存儲資源消耗較大,處理時延較長;。 在多對一連接模型中,組件接口和消息封裝模塊之間需要一個緩沖區,以便在多個接口同時需要發送消息時對消息進行緩沖,而消息封裝模塊也需要一個緩沖區對消息進行緩沖,因此需要兩級緩沖區。一對一連接模型只需要一級緩沖區,因為該模型不需要組件接口和消息封裝模塊之間的緩沖區消息。 其次,由于許多組件接口使用相同的消息打包模塊,消息打包模塊需要建立一個通信地址表來記錄每個接口的地址。 每次在打包消息時,消息打包模塊都需要查找地址表以獲得正確的接口地址,所以處理延遲會增加。 此外,表查找在 FPGA 上的實現非常復雜。一對一連接模型不需要地址表。 與多對一連接模型相比,一對一連接模型也存在不足。 主要缺點是一對一連接模型需要很多消息打包模塊,而多對一連接模型只需要一個。 許多消息打包模塊會增加邏輯資源的消耗,但是一對一連接模型中每個消息打包模塊的邏輯資源消耗很小,因為消息打包工作很容易。 綜合考慮兩種不同的連接模型的優點和缺點,一對一的連接模型更為合適。 4. 結論 本文結合現場可編程門陣列(FPGA)的特點和實際應用的需要,首先設計了 PAL 的結構,然后根據標準消息格式的不足,設計了一種新的消息格式來彌補這一不足,最后分析了兩種不同的連接模型,得出一對一的連接模型更為合適的結論。 在 FPGA 上實現 PAL 制,完全解決了上述問題。針對軟件無線電系統在波形可移植性方面存在的問題,提出了一種軟件無線電系統可移植性的解決方案。 另外,PAL 制的結構也適合 DSP,只是實現方式有所不同。

|