標題: 數字電路八路智力競賽搶答器課程設計(NE555+74LSXX芯片) [打印本頁]

作者: abc129 時間: 2018-11-23 01:48

標題: 數字電路八路智力競賽搶答器課程設計(NE555+74LSXX芯片)

課程設計任務書

題 目: 八路智力競賽搶答器設計

初始條件:

- 教 材:《電子線路設計·實驗·測試》

- 元器件:74LS48三片,72LS192兩片,74LS279、74LS148、74LS00、74LS11、555各一片,數碼管三個,發光二極管一個,開關、電阻、電容若干,面包板,導線若干

- 仿 真:Proteus仿真軟件

要求完成的主要任務: (包括課程設計工作量及其技術要求,以及說明書撰寫等具體要求)

基本功能:

1.設計一個智力競賽搶答器,可同時供8名選手或8個代表隊參加比賽,他們的編號分別是0、1、2、3、4、5、6、7,各用一個搶答按鈕,按鈕的編號與選手的編號相對應,分別是S0、S1、S2、S3、S4、S5、S6、S7。

2.給節目主持人設置一個控制開關,用來控制系統的清零(編號顯示數碼管滅燈)和搶答的開始。

3.搶答器具有數據鎖存和顯示的功能。搶答開始后,若有選手按動搶答按鈕,編號立即鎖存,并在LED數碼管上顯示出選手的編號,同時揚聲器給出音響提示。此外,要封鎖輸入電路,禁止其他選手搶答。優先搶答選手的編號一直保持到主持人將系統清零為止。

擴展功能:

1.搶答器具有定時搶答的功能,且一次搶答的時間可以由主持人設定。當節目支持人按下“開始”按鈕后,要求定時器立即倒計時,并在顯示器上顯示,同時揚聲器發出短暫的聲響,聲響持續時間0.5s左右。

2.參賽選手在設定的時間內搶答,搶答有效,定時器停止工作,顯示器上顯示選手的編號和搶答時刻的時間,并保持到主持人將系統清零為止。

3.如果定時搶答的時間已到,卻沒有選手搶答,則本次搶答無效,系統短暫報警,并封鎖輸入電路,禁止選手超時后搶答,時間顯示器上顯示00.

課程設計的內容要求用A4紙打印,且頁數不得少于20頁。

時間安排:

第20周理論設計、實驗室安裝調試

地點安排:

鑒主15樓通信實驗室一

指導教師簽名: 年 月 日

系主任(或責任教師)簽名: 年 月 日

摘要

在各種智力競賽場合,搶答器是必不可少的最公正的用具。

本次所設計的智力競賽搶答器可同時供8名選手或8個代表隊參加比賽。電路由主體電路和擴展電路兩部分組成,分別由集成編碼器、計數器、鎖存器、定時器和必要的門電路等組成,其中主體電路的作用是完成主持人的控制系統清零與搶答開始功能以及完成參賽者的搶答并顯示其編號的功能,擴展電路由控制電路,主要包括秒脈沖發生電路和定時電路,并且在設計中加入了報警電路,以提示選手和觀眾。

經Proteus仿真軟件驗證搶答器原理圖無誤,可實現設計所要求功能。根據原理圖,在面包板上連接構成實物。

目錄

八路智力競賽搶答器1

1 八路智力競賽搶答器的設計2

1.1 搶答器的功能要求 2

1.2 整體設計思路 2

1.3單元電路的設計 4

1.4 搶答器整體電路 14

2 電路仿真16

3 八路智力搶答器實物制作17

3.1 面包板的使用 17

3.2 電路板制作 19

4 元器件清單20

5 小結21

6 參考文獻22

附錄 八路智力競賽搶答器總圖1

本科生課程設計成績評定表1

指導教師簽字:1

年 月 日1

八路智力競賽搶答器

在各種智力競賽場合,搶答器是必不可少的最公正的用具。在我們各種競賽中我們也經常能看到有搶答的環節,某些舉辦方采用讓選手通過舉答題板的方法判斷選手的答題權,這在某種程度上會因為主持人的主觀誤斷造成比賽的不公平性,而搶答器的應用就能避免這種弊端。隨著科技的飛速發展,能夠實現搶答器功能的方式有多種,可以采用模擬電路、數字電路或模擬與數字電路相結合的方式以及利用微電腦芯片作為核心部件進行邏輯控制及信號產生的單片機技術和C語言編程而設計的多路智力競賽搶答器。本設計將采用數字電路實現一八路智力競賽搶答器。

1 八路智力競賽搶答器的設計

1.1 搶答器的功能要求

基本功能:設計一個智力競賽搶答器,可同時供8名選手或8個代表隊參加比賽,他們的編號分別是0、1、2、3、4、5、6、7,各用一個搶答按鈕,按鈕的編號與選手的編號相對應,分別是S0、S1、S2、S3、S4、S5、S6、S7。給節目主持人設置一個控制開關,用來控制系統的清零(編號顯示數碼管滅燈)和搶答的開始。搶答器具有數據鎖存和顯示的功能。搶答開始后,若有選手按動搶答按鈕,編號立即鎖存,并在LED數碼管上顯示出選手的編號。此外,要封鎖輸入電路,禁止其他選手搶答。優先搶答選手的編號一直保持到主持人將系統清零為止。

擴展功能:搶答器具有定時搶答的功能,且一次搶答的時間可以由主持人設定。當節目主持人按下“開始”按鈕后,要求定時器立即倒計時,并在顯示器上顯示,同時揚聲器發出短暫的聲響,聲響持續時間0.5s左右。參賽選手在設定的時間內搶答,搶答有效,定時器停止工作,顯示器上顯示選手的編號和搶答時刻的時間,并保持到主持人將系統清零為止。如果定時搶答的時間已到,卻沒有選手搶答,則本次搶答無效,系統短暫報警,并封鎖輸入電路,禁止選手超時后搶答,時間顯示器上顯示00.

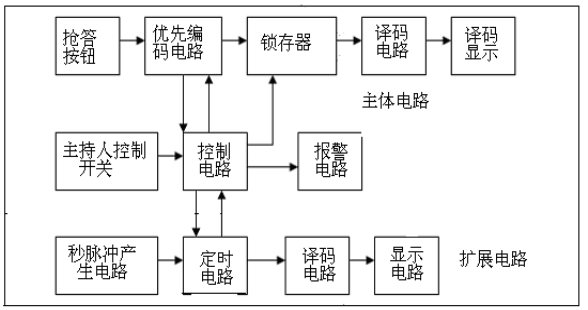

1.2 整體設計思路

根據對功能要求的簡要分析,將定時搶答器電路分為主題電路和擴展電路兩部分。主體電路完成基本的搶答功能,即開始搶答后,當選手按動搶答器按鈕時,能顯示選手的編號,同時能封鎖輸入電路,禁止其他選手搶答。擴展電路完成定時搶答及報警功能。

比賽開始時,接通電源,節目主持人將開關置于“清零”位置,搶答器處于禁止工作狀態,編號顯示器滅燈,定時顯示器上顯示設定時間。當節目主持人宣布“搶答開始”,同時將控制開關撥到“開始”位置,搶答器處于工作狀態,定時器開始倒計時。若定時時間到,卻沒有選手搶答時,系統報警,并封鎖輸入電路,禁止選手超時后搶答。若選手在定時時間內按動搶答按鈕時,搶答器要完成以下四項工作:1.優先編碼器電路立即分辨出搶答者的編號,并由鎖存器進行鎖存,然后由譯碼顯示電路顯示編號; 2.揚聲器發出短暫聲響,提醒節目主持人注意; 3.控制電路要對輸入編碼電路進行封鎖,避免其他選手再次進行搶答; 4.控制電路要使定時器停止工作,時間顯示器上顯示剩余的搶答時間,并保持到主持人將系統清零為止。當選手將問題回答完畢時,主持人操作控制開關,使系統回復到禁止工作狀態,以便進行下一輪搶答。

根據對功能要求的理解,設計了如下兩種方案。

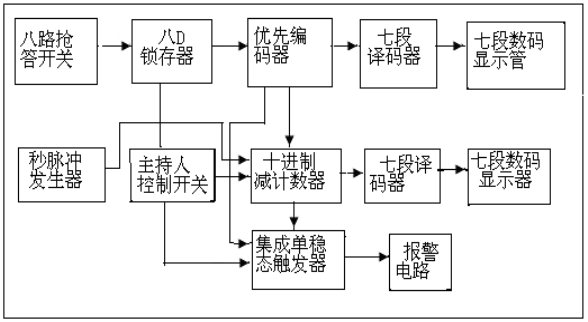

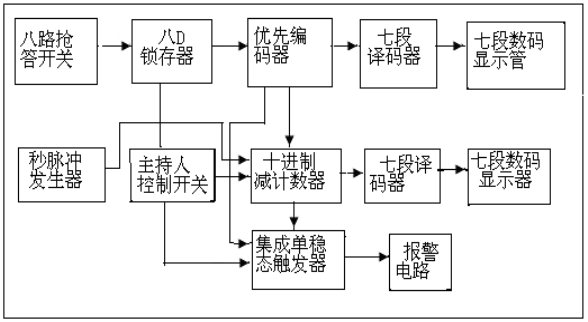

方案一系統框圖如圖1所示。

圖1 八路智力搶答器方案一設計框圖

方案一所示搶答器工作過程:該方案是將搶答按鈕先直接與鎖存器而不是優先編碼器相連,將最先搶答的選手的編號鎖定,再依次經過優先編碼器、譯碼器和七段顯示器,最后顯示的是搶答選手的編號,經過優先編碼器后的信號到單穩態觸發器,單穩態觸發器又與報警電路直接連接,所以顯示編號的同時可以發出報警信號。另外由主持人控制開關和其他部分電路通過門電路實現對搶答電路、定時電路和報警部分電路的控制。

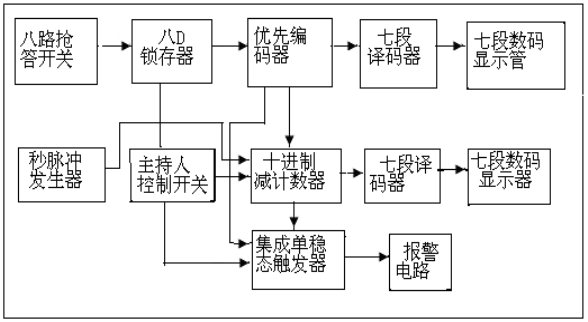

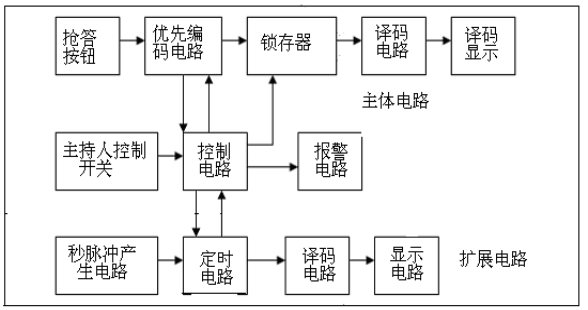

方案二系統框圖如圖2所示。

圖2 八路智力搶答器方案二設計框圖

方案二所示搶答器的工作過程:主持人按動開始搶答的開關后,最先搶答的選手的電平信號先經過優先編碼器,再依次經過數據鎖存器,此時已經限制了其他選手的搶答,信號再經過譯碼器和七段數碼顯示器,將最先搶答的該選手的編號顯示出來,并同時產生報警信號,到此完成的是搶答功能;如果沒有人搶答, 30秒減計數器減到00時也會發出報警信號,此是完成計時功能。

相比之下,第二種方案更好些。它的優點表現在以下幾個方面:這種方案原理比較簡單。主持人對整體電路的控制只需幾個門電路就可完成,不必用特別的芯片來組成控制電路;更容易實現報警提示功能,在有選手搶答后或者計時開始和結束時。既減少了布線使整個電路更直觀簡單,又降低了產生錯誤的可能性。

1.3單元電路的設計

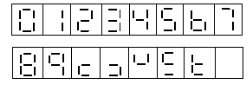

1.3.1搶答電路設計

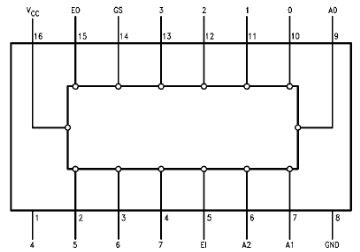

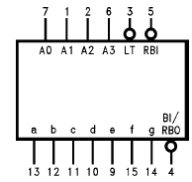

搶答電路的功能有兩個:一是能分辨出選手按按鈕的先后,并鎖存優先搶答者的編號,供譯碼顯示電路用;二是要使其他選手的按鈕操作無效。因此,選用優先編碼器74LS148和RS鎖存器74LS279以及譯碼顯示電路完成上述功能,其引腳圖及真值表如下圖所示。

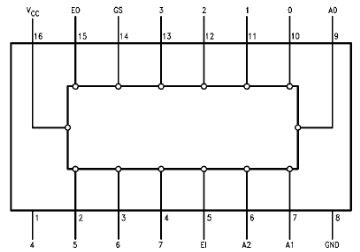

圖3 74LS148引腳圖

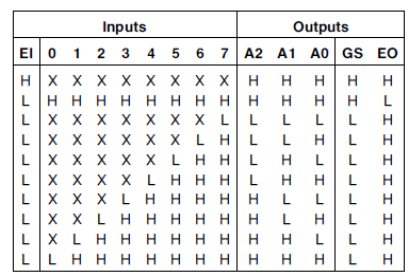

表1 74LS148真值表

74LS148是一八線-三線優先編碼器,該編碼器由8個信號輸入端,3個二進制輸出端,輸入輸出均為低電平有效。EI為輸入使能端,低電平有效,當EI為低電平時,編碼器處于工作狀態;EO為輸出使能端,只有在EI=0,且所有輸入都為1時,輸出為0;GS表征編碼器的工作狀態,當且僅當EI為低電平,且輸入至少有一各為有效電平時,GS才有效。

因此,可根據EI、EO、GS功能擴展端的特點,對電路進行相應控制。編碼器在搶答電路中功能是判斷搶答者的編號。

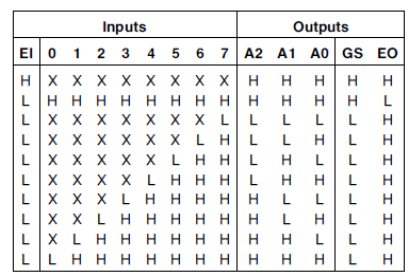

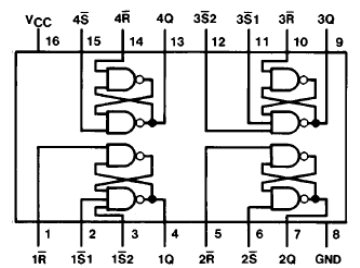

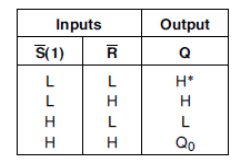

圖4 74LS279引腳圖

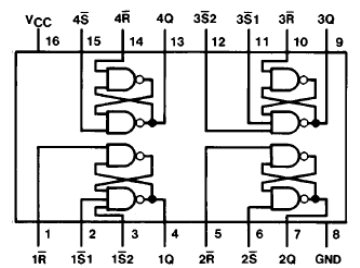

74LS279是由4個RS鎖存器組成,且均為與非門構成的RS鎖存器。其中,1S和3S有兩個輸入端,S1和S2均為相與的關系。本設計中,將S2均接高電平,僅利用S1控制輸出。其引腳圖如圖四所示,下表為SR鎖存器的功能真值表,值得注意的是S和R不能同時為高電平,否則輸出不確定。

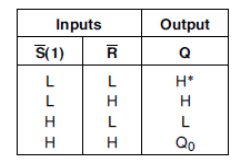

表2 74LS279真值表

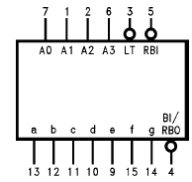

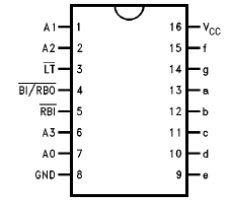

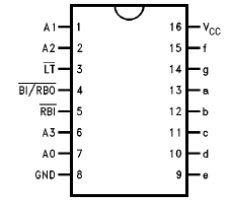

74LS48為七段顯示譯碼器。該集成譯碼器設有多個輔助控制端,以增強器件的功能。BI/RBO為滅燈輸入,當BI=0時,所有字形熄滅。LT為試燈輸入,當LT=0且RBO=1時,顯示字形為8,常用于檢測自身的好壞。RBI為動態滅燈輸入,當LT=1,RBI=0且輸入均為0時,輸出均為低電平,數碼管“滅零”。其引腳圖和邏輯圖分別如圖5圖6所示,真值表如表3所示。

圖5 74LS48的引腳圖 圖6 74LS48的邏輯圖

表3 74LS48真值表

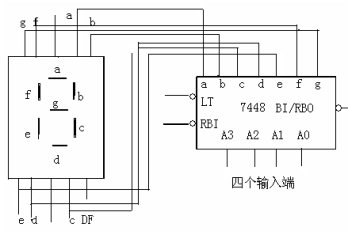

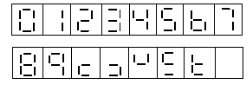

由真值表可以看出譯碼器74LS48輸出高電平有效,用以驅動共陰極數碼管。七段顯示譯碼器一般與七段數碼顯示器相連,共同構成四輸入端的數碼顯示電路,如圖7所示。共陰極數碼顯示器的功能表如表4所示。

圖7 7448組成的四個輸入端的數碼顯示組合電路

圖8 7448產生的顯示數字

表4 共陰極數碼顯示器的功能表

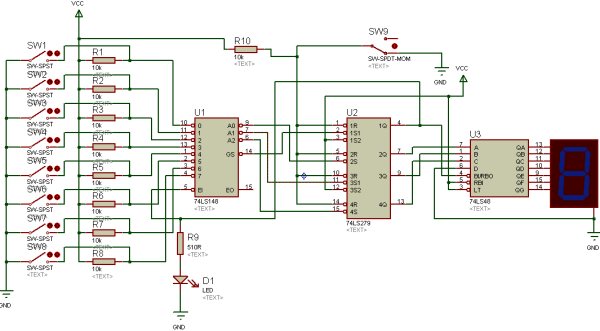

根據各芯片功能及搶答器的功能要求,搶答器電路如下所示

圖9 搶答器電路

工作原理:SW1-8為八位選手的搶答開關,SW9單刀雙擲開關設為主持人控制開關。當主持人控制開關置于清零狀態時,RS觸發器的R端為低電平,輸出端全部為低電平。于是74LS48的BI為高,顯示器滅燈;74LS148的選通輸入端ST為高電平,74LS148處于工作狀態,此時鎖存電路不工作。當SW9置于開始狀態,優先編碼電路和鎖存電路同時處于工作狀態。74LS279的1R、1S均為高電平,由真值表可知,輸出1Q為低電平,從而使74LS148輸入使能端為低電平有效,即搶答器處于等待工作狀態。若有選手(假設為3號選手)按動搶答開關(即閉合SW4),此時優先編碼器74LS148輸入端I3接低電平有效,則輸出A2A1A0為100,A2A1A0分別接至4S、3S、2S,根據RS鎖存器真值表,2Q3Q4Q輸出分別為110,從而74LS48的輸入端DCBA為0011,經74LS48譯碼,顯示器上顯示“3”。與此同時,當74LS148輸入端有一個為低電平時,GS為低電平有效,即標志譯碼器處于工作狀態,從而使1S為0,此時1Q輸出為高電平,致使EI為高電平,74LS148處于禁止工作狀態,其他選手搶答按鈕的輸入信號不會被接受。這就保證了搶答者優先性以及搶答電路的準確性。搶答結束后,主持人開關置于清零狀態,數碼管變灰,一切恢復初始狀態,以便進入下一輪搶答環節。

1.3.2 定時電路設計

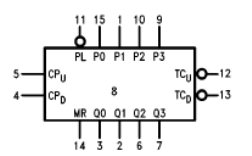

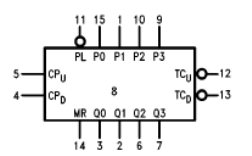

設計要求搶答器具有定時功能,且節目主持人根據搶答題的難易程度,可設定一次搶答的時間(設為30s)。設計中選用十進制同步加/減計數器74LS192進行設計,74LS192是具有置數和清零功能,其引腳圖和邏輯圖如圖10所示,真值表如表5所示。

圖10 74LS192引腳圖和邏輯圖

P0、P1、P2、P3——置數并行數據輸入;

Q0、Q1、Q2、Q3——計數數據輸出;

CR————————清零端;

LD————————置數端;

CPu ———————加法計數CP輸入;

CPd ———————減法計數CP輸入;

CO————————進位輸出端;

BO————————借位輸出端。

表5 74LS192真值表

根據設計要求,需要兩片74LS192構成100進制減計數器。由功能真值表可知,只需將個位74LS192的借位輸出端BO與十位74LS192的CPd即可實現100進制減計數。值得注意的是,要使其實現減計數,CPu端口必須接高電平。

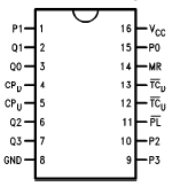

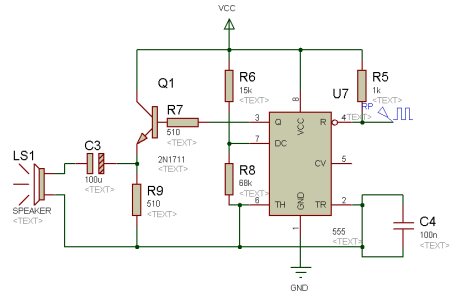

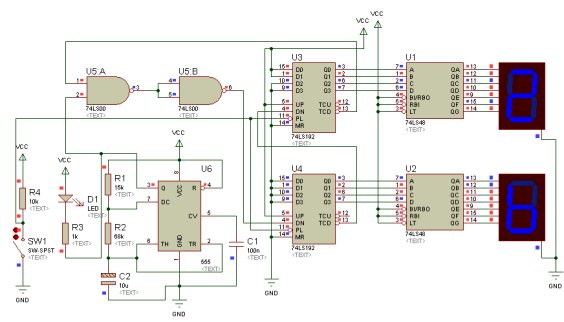

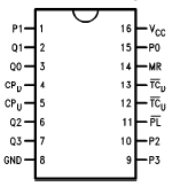

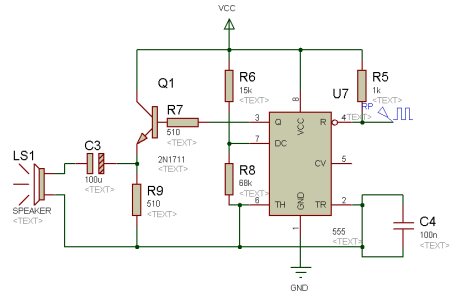

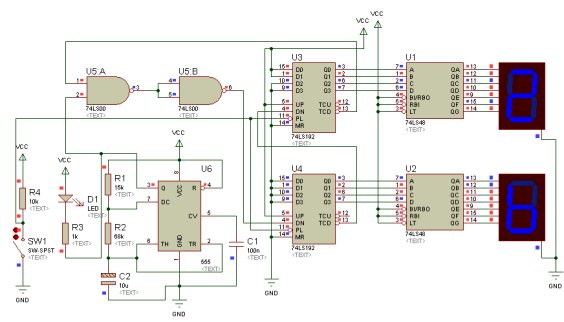

計數器的時鐘脈沖由秒脈沖電路提供。秒脈沖電路由555構成的多諧振蕩器構成,如圖11所示。多諧振蕩器無需外加輸入信號就能在接通電源自行產生矩形波輸出。

圖11 多諧振蕩器

因為周期為一秒,所以頻率是1赫茲。圖中電容的充放電時間分別是:

t1=RB×C×ln2≈0.7RB×C t2=(RA+RB)×C×ln2≈0.7(RA+RB)C

所以555的3端輸出的頻率為: f=1/(t1+t2)≈1.43/[(2RA+RB)C]

我們采用的電阻和電容值分別是:RA=15KΩ,R2=68KΩ,C1=10uf,滿足上式,即得到的是秒脈沖。

由以上集成芯片設計的定時電路如圖12所示。

圖12 定時電路

工作原理:首先主持人根據題的難易程度改變74LS192的輸入端D3D2D1D0的電平來確定搶答時間(假定為30秒),555構成秒脈沖產生電路為計時電路提供脈沖。搶答開始前主持人閉合開關,74LS192的置數端PL為低電平有效,處于置數狀態,數碼管顯示定時時間。搶答開始,主持人打開開關,計數器處于計數狀態,555產生的秒脈沖與十位74LS192借位輸出端(其初始狀態為高電平)相與。計數器遞減計數至00,十位74LS192借位輸出端為低電平,計數器停止工作,產生報警。計時期間有人搶答,減計數器停止計時,顯示器上顯示此刻時間。

1.3.3報警電路設計

由555定時器和三極管構成的報警電路如圖13所示。圖中555定時器用來構成多諧振蕩器,其震蕩頻率和秒脈沖產生電路中頻率的計算方法相同。3端的輸出信號經過三級管驅動揚聲器,發出報警信號。當4端的輸入信號是高電平時,振蕩器工作,有報警信號,4端輸入低電平時,振蕩器不工作,沒有報警信號。也就是說需要報警時只需控制輸入端即可。

圖13報警電路

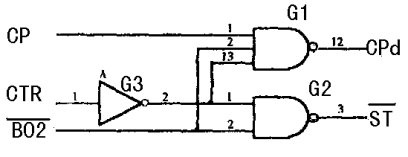

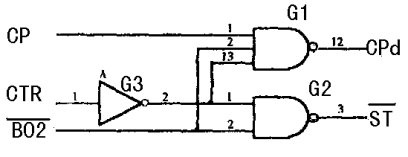

1.3.4 時序控制電路

時序控制電路是搶答器設計的關鍵,需要完成以下三項功能:

a.主持人將控制開關撥到“開始”位置時,揚聲器發聲,搶答電路和定時電路進入正常搶答工作狀態。

b.當競賽選手按動搶答鍵時,揚聲器發聲,同時搶答電路和定時電路停止工作。

c.當設定的搶答時間到,無人搶答時揚聲器發聲,同時搶答電路和定時電路停止工作。

本設計中采用門電路對控制開關、搶答電路、定時電路、報警電路進行連接,以實現上述三項功能要求(如圖14所示)。

圖14 時序控制電路

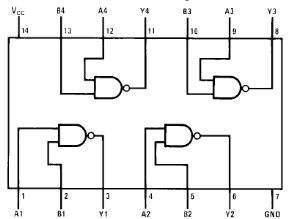

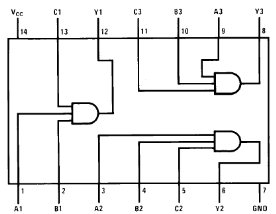

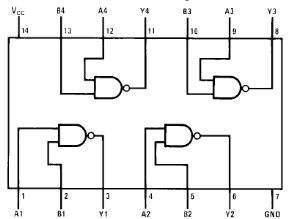

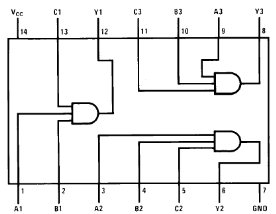

其中,兩輸入與非門采用74LS00,引腳圖如圖15所示。三輸入與門采用74LS11,引腳圖如圖16所示。電路中利用與非門兩輸入端相連實現非門的邏輯功能。

圖15 74LS00引腳圖

圖16 74LS11引腳圖

工作原理:門G1的作用是控制時鐘信號CP的放行與禁止,門G2的作用是控制74LS148的輸入使能端。主持人控制開關從“清零”位置撥到“開始”位置時,74LS279的輸出1Q=0,經G3反相,A=1,則從555輸出端來的時鐘信號CP能夠加到74LS192的CPd始終輸入端,定時電路進行遞減計時。同時,在定時時間未到時,74LS192的借位輸出端BO2為低電平,門G2的輸出ST為高電平,使74LS148處于正常工作狀態,從而實現功能a的要求。當選手在定時時間內按動搶答按鈕時,1Q=1,經G3反相,A=0,封鎖CP信號,定時器處于保持工作狀態;同時,門G2的輸出ST為低74LS148處于禁止工作狀態,從而實現功能b的要求。當定時時間到時,來自74LS192的BO2為高,ST為高,74LS148處于禁止工作狀態,禁止選手進行搶答。同時,門G1處于關門狀態,封鎖CP信號,使定時電路保持00狀態不變,從而實現功能c的要求。

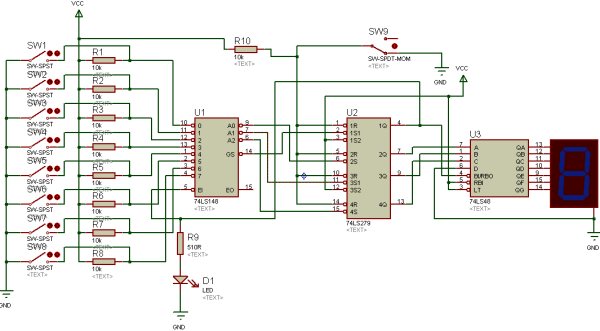

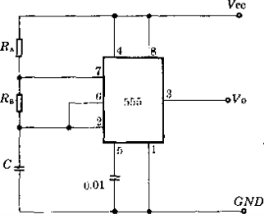

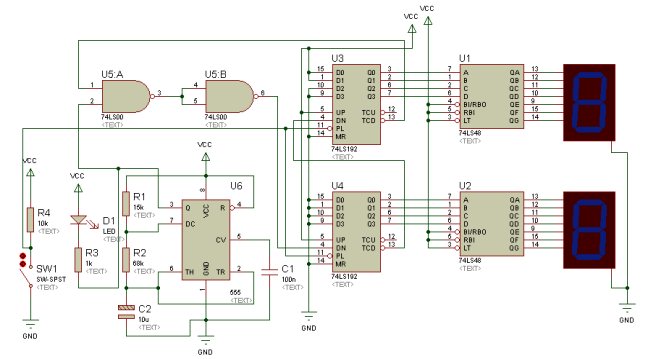

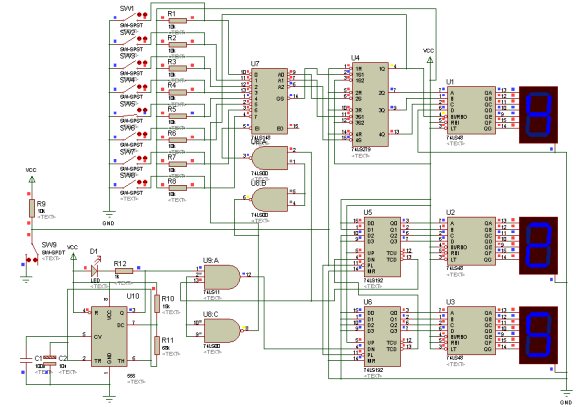

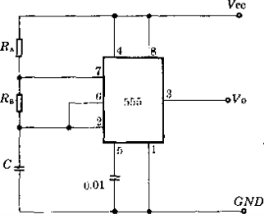

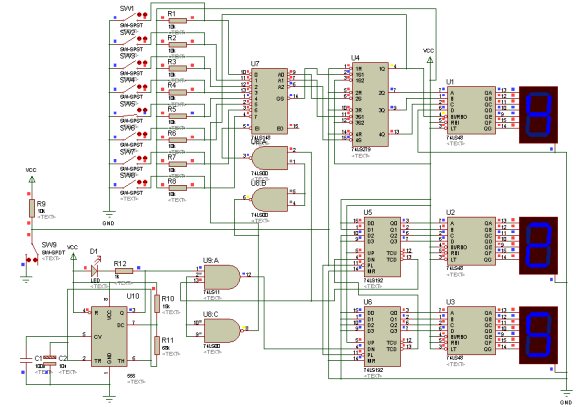

1.4 搶答器整體電路

通過控制電路將搶答、定時電路進行連接后,構成了搶答器電路的整體設計,總電路圖如圖17所示:

圖17 總電路圖

下面介紹八路智力競賽搶答器的使用原理。

首先是各個選手分別對應的按鈕編號是S0、S1、S2、S3、S4、S5、S6、S7,搶答后顯示器上顯示的分別是0、1、2、3、4、5、6、7。

然后是主持人對整個電路系統清零,將開關置于“清零”的位置,輸出低電平,分為兩路:一路與鎖存器的1R2R3R4R端相連,使輸出端1Q2Q3Q4Q為低電平,1Q所輸出的低電平經與門反饋給74LS148的EI端子,編碼器不工作,因此搶答部分顯示器滅燈無顯示,實現了清零;另一路低電平輸出到計數器74LS192的LD端,而CR端也是低電平,所以使得對應顯示器輸出預置的數據。

接下來主持人根據題目的難易程度設置搶答時間,此設定可以通過調節輸入兩片74LS192的四個輸入端D、C、B、A的高低電平來進行(例如要設定時間為30秒,就將十位的74192的D、C、B、A分別置位為0、0、1、1,而將各位的74LS192的D、C、B、A都置于0)。當主持人宣讀完題目說“開始”并將開關置于“開始”位置后,輸出為高電平,此高電平有兩路方向:一路輸出到74LS192的LD端,使其處于高電平而開始減計數;還有一路輸出到鎖存器的R端。

當任意一個選手搶答時,例如3號搶答時,74LS148三號端子輸入低電平有效,此時GS為低電平有效,表征編碼器在正常工作。編碼輸出A2A1A0為100,與其對應的4S3S2S為100,經74LS279鎖存,4Q3Q2Q輸出為011,經譯碼顯示編號為3。與此同時,1Q所輸出的高電平反饋回編碼器的是能輸入端,使其停止工作。此時,其他選手若再按動按鈕也無對應輸出,這就保證了搶答者優先性以及搶答電路的準確性。另一路,74LS148的GS端輸出電平由高變低,與秒脈沖發生器產生的秒脈沖相與后輸出為0,使得無脈沖抵達計數器74LS192的Down端。計數器停止工作,保持原來顯示不變,即實現了暫停減計數使其記錄搶答時間的功能。

若沒有選手按動按鈕,則74LS279輸出全為高電平,74LS148也輸出高電平,1Q端輸出低電平至74LS48的滅燈輸入RI/RBO端,使得信號經74LS48到顯示器上時無顯示;若到定時部分計數器倒計時到00還無選手按動按鈕的話,十位74LS192的借位輸出端輸出高電平反饋回個位Down端,停止計數。

綜上所述,所設計的電路基本可以實現要求中的功能。

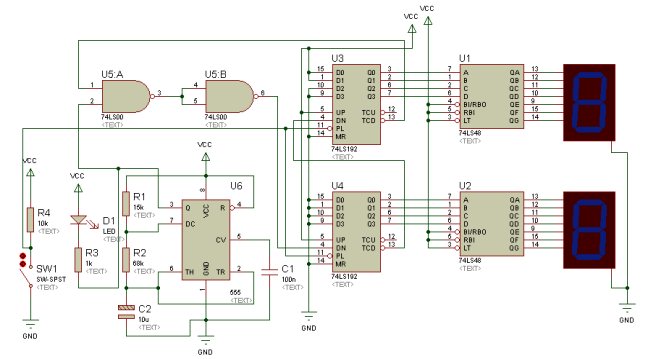

2 電路仿真

電路仿真采用Protues仿真軟件進行的。Protues軟件可提供的仿真元器件資源:仿真數字和模擬、交流和直流等數千種元器件;可提供的仿真儀表資源 :示波器、邏輯分析儀信號發生器、交直流電壓表電流表等。它不僅具有其它EDA工具軟件的仿真功能,還能仿真單片機及外圍器件。因此,選用該軟件對搶答器各單元電路及整體電路進行仿真。

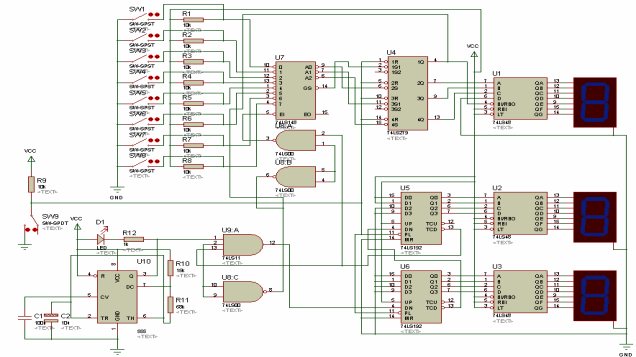

圖18 搶答電路仿真

計時電路仿真

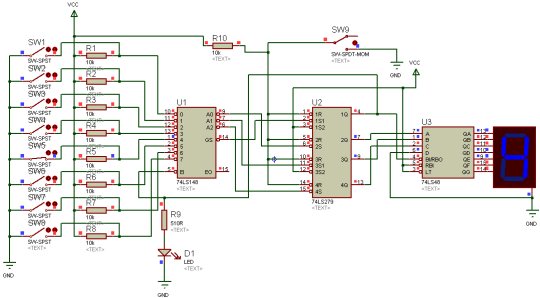

圖19 計時電路仿真

整體電路仿真

圖20 整體電路仿真

通過對各單元電路及總電路的仿真,驗證了設計電路的正確性。

3 八路智力搶答器實物制作

由于本設計使用芯片數量較多,管腳連線復雜,為避免在焊接過程中出現疏漏和錯誤,故在搶答器的制作時選擇用面包板完成。

3.1 面包板的使用

面包板是專為電子電路的無焊接實驗設計制造的。由于各種電子元器件可根據需要隨意插入或拔出,免去了焊接,節省了電路的組裝時間,而且元件可以重復使用,所以非常適合電子電路的組裝、調試和訓練。

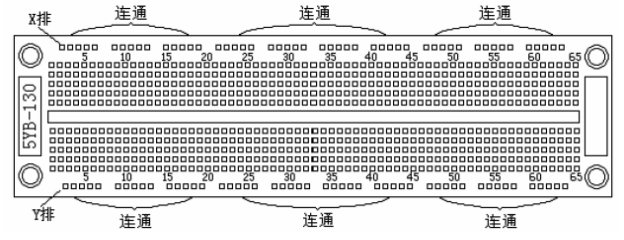

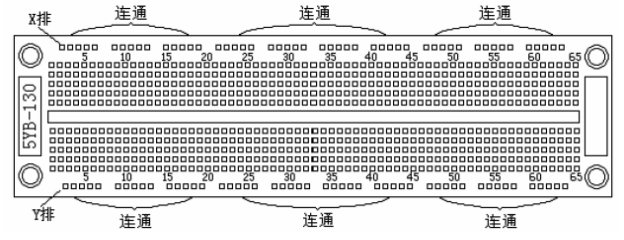

面包板圖21所示。插座板中央有一凹槽,凹槽兩邊各由65列小孔,每一列的五個小孔在電氣上相互連通。集成電路的引腳就分別插在凹槽兩邊的小孔上。插座上、下邊各一排(即X和Y排)在電氣上是分段相連的55個小孔,分別作為電源與地線插孔用。對于SYB-130插座板,X和Y排的1-15孔、16-35孔、36-50孔在電氣上是連通的。

圖21 面包板結構圖面包板插孔所在的行列分別以數碼和文字標注,以便查對。

A.安裝分立元件時,應便于看到其極性和標志,將元件引腳理直后,在需要的地方折彎。為了防止裸露的引線短路,必須使用帶套管的導線,一般不剪斷元件引腳,以便于重復使用。一般不要插入引腳直徑〉0.8mm的元器件,以免破壞插座內部接觸片的彈性。

B.對多次使用過的集成電路的引腳,必須修理整齊,引腳不能彎曲,所有的引腳應稍向外偏,這樣能使引角與插孔可靠接觸。要根據電路圖確定元器件在面包板上的排列方式,目的是走線方便。為了能夠正確布線并便于查線,所有集成電路的插入方向要保持一致,不能為了臨時走線方便或縮短導線長度而把集成電路倒插。

C.根據信號流程的順序,采用邊安裝邊調試的方法。元器件安裝之后,先連接電源線和地線。為了查線方便,連線盡量采用不同顏色。例如:正電源一般采用紅色絕緣皮導線,負電源用藍色,地線用黑線,信號線用黃色,也可根據條件選用其它顏色。

D.面包板宜使用直徑為0.6mm左右的單股導線。根據導線的距離以及插孔的長度剪斷導線,要求線頭剪成45o斜口,線頭剝離長度約為6mm左右,要求全部插入底板以保證接觸良好。裸線不宜露在外面,防止與其它導線斷路。

E.連線要求緊貼在面包板上,以免碰撞彈出面包板,造成接觸不良。必須使連線在集成電路周圍通過,不允許跨接在集成電路上,也不得使導線互相重疊在一起,盡量做到橫平豎直,這樣有利于查線,更換元器件及連線。

F.最好在各電源的輸入端和地之間并聯一個容量為幾十微法的電容,這樣可以減少瞬變過程中電流的影響。為了更好地抑制電源中的高頻分量,應該在該電容兩端再并聯一個高頻去耦電容,一般取0.01 ~ 0.047Uf的獨石電容。

G.在步線過程中,要求把各元器件在面包板上的相應位置以及所用的引腳號標在電路圖上,以保證調試和查找故障的順利進行。

H.所有的地線必須連接在一起,形成一個公共參考點。

3.2 電路板制作

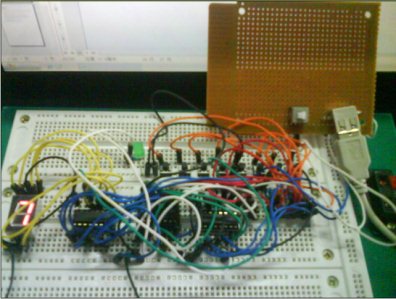

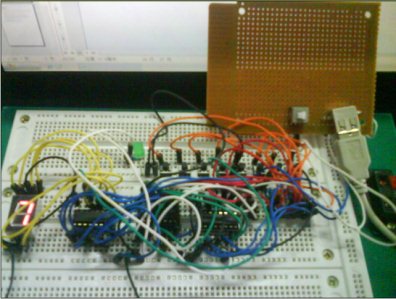

由于客觀條件限制,實物制作僅選擇了主體電路進行制作調試,即搶答電路部分。

首先,按照面包板的使用規則,將74LS148、74LS249及74LS48依次插在凹槽兩側。再將其余元器件(電阻、開關等)插入面包板。然后,按照搶答電路原理圖所示接線。接線過程中,應注意面包板內部結構,有效使用其相通插孔,減少接線數量。制作過程中,由于主持人所用的控制開關插入面包板無法有效使用,因此,將其單獨焊接在電路板上。此外,制作時采用了USB供電的辦法以提供電路所需電源。實物如圖22所示。

圖22 搶答電路實物圖

4 元器件清單

下表為八路智力競賽搶答器整體圖所生成的元器件清單。各芯片的引腳圖、邏輯功能、真值表等均在前有相應介紹。

表6 元器件清單

Resistors

---------

9 R1-R9 10k

1 R10 15k

1 R11 68k

1 R12 1k

Capacitors

----------

1 C1 100n

1 C2 10u

Integrated Circuits

-------------------

3 U1-U3 74LS48

1 U4 74LS279

2 U5,U6 74LS192

1 U7 74LS148

1 U8 74LS00

1 U9 74LS11

1 U10 555

Diodes

------

1 D1 LED

Miscellaneous

-------------

8 SW1-SW8 SW-SPST

1 SW9 SW-SPDT

5 小結

通過本次課程設計,不僅有效鞏固了本學期所學數電的相關知識,加強了對重要知識點的記憶和理解,還學會如何運用Protues仿真進行仿真,以及如何使用面包板進行實物制作,受益匪淺,現總結如下。

搶答器的設計在本學期數電實驗中操練過,因此對其并不陌生。但它的功能要求相對于數電實驗中的搶答器要更深一步,不僅添加了定時電路、報警電路,其時序控制電路也要比原先復雜。對于單元電路的設計,均較順利的完成。而本設計的難點在于時序控制電路的設計,如何在第一位搶答者搶答題目后讓編碼器停止工作;如何使計時電路在搶答后停止倒計時;如何讓定時電路和搶答電路同時清零。設計過程中,根據以往搶答器設計思路,及查閱相關資料,可運用74LS279的輸出1Q完成上述控制任務。從這一點,折射出自己在平時的學習中較死板,缺乏變通思考的能力。

在電路仿真的過程中,由于Protues操作相對較簡單,因此在仿真過程中較為順利。只有在總電路圖的仿真時,由于粗心大意,誤將兩個與非門連接成的非門輸入輸出接反,導致未出現相應仿真結果,經認真排查電路,發現問題所在,更正,最終完成仿真任務,從而驗證了電路圖的正確性。

在實物制作過程中,由于第一次接觸面包板,對面包板的結構及相關注意事項不十分了解,經查閱相關資料,對其有了一個大致的了解。但在整體布局及相通插孔的有效利用等方面,還需進一步加強。由于芯片較多,接線較為復雜,因此,只完成了搶答電路的制作。在連線過程中,較為細心仔細,無大的失誤,也使后續的錯誤排查提供了方便。對于電源,在制作中,運用了USB為電路提供電源。

通過本次實踐操作,也讓我深刻明白:只有將課本上的理論知識,結合實踐不斷練習,不斷總結提煉,反復思考實踐中的經驗教訓,才能夠真正消化為自己的知識。

附錄 八路智力競賽搶答器總圖

| 歡迎光臨 (http://www.zg4o1577.cn/bbs/) |

Powered by Discuz! X3.1 |

主站蜘蛛池模板:

国产一区二区影院

|

欧美视频一区

|

五月花丁香婷婷

|

成人av免费

|

日本一区二区三区四区

|

国产精品欧美一区二区三区

|

成人欧美一区二区三区

|

欧美国产日韩在线观看成人

|

国产精品久久久久久久久久久久久久

|

欧美日韩一区二区三区不卡视频

|

亚洲国产精品久久久

|

91久久精

|

无人区国产成人久久三区

|

精品视频在线一区

|

国产精品不卡

|

成人av片在线观看

|

91 视频网站

|

特一级毛片

|

国产精品久久久久久一区二区三区

|

亚洲视频中文字幕

|

午夜一区二区三区视频

|

日韩精品一区二区三区中文在线

|

国产偷录叫床高潮录音

|

国产一区二区三区日韩

|

日韩一区在线观看视频

|

久久手机视频

|

91精品国产777在线观看

|

亚洲毛片

|

亚洲视频区

|

伊人伊成久久人综合网站

|

超碰精品在线观看

|

亚洲第一福利网

|

日韩精品一区二区三区视频播放

|

欧美视频免费在线

|

国产污视频在线

|

五月激情久久

|

国产精品久久久久一区二区

|

wwww.xxxx免费

|

久久99精品久久久久婷婷

|

久久99精品久久久久婷婷

|

国产a区

|