第一章 諸論1.1設計背景時鐘是人們必不可少的生活用品。從古代的滴漏更鼓到近代的機械鐘,從電子表到目前的數字時鐘,為了準確的測量和記錄時間,人們一直在努力改進計時工具。鐘表的數字化,大力推動了計時的精確性和可靠性。在單片機構成的裝置中,數字時鐘是必不可少的部件。它的用途十分廣泛,只要有計時的存在,便要用到數字時鐘的原理及結構;同時在日期中,它以其小巧,價格低廉,走時精度高,使用方便,功能多,便于集成化而受廣大消費的喜愛。

隨著人類科技文明的發展,人們對于時鐘的要求在不斷地提高。時鐘已不僅僅被看成一種用來顯示時間的工具,在很多實際應用中它還需要能夠實現更多其它的功能。高精度、多功能、小體積、低功耗,是現代時鐘發展的趨勢。在這種趨勢下,時鐘的數字化、多功能化已經成為現代時鐘生產研究的主導設計方向。

本次設計的數字時鐘與傳統的時鐘相比,具有高精度、多功能、小體積、低功耗的優勢,其時間采用數字顯示。該設計控制器使用單片機AT89C51作為中央處理的核心,六位數碼管作為時間數字的顯示屏,實現了顯示時間、調整時間、鬧鐘定時等功能,達到了設計的要求和目的。

1.2 數字溫度計設計方案論證1.2.1 方案一基于FPGA的多功能數字時鐘的設計方法:DCM(數字時鐘管理器)。DCM使用完全數字反饋系統確保多個時鐘同步,使用完全數字延線技術可以精確控制時鐘的頻率和相位。用戶可以編程控制時鐘任意倍率和分頻及任意相位移動,使用非常方便可靠。

缺點:設計較為復雜,成本高,無法實現溫度測量功能。

1.2.2 方案二基于VHDL的多功能數字時鐘的設計利用VHDL硬件描述語言設計的多功能數字時鐘的思路,在MAX+PLUSⅡK開發環境中編譯和仿真了所設計的程序,并在可編程邏輯器上下載驗證。

缺點:結構簡單,實現功能不全面。

1.2.3 方案三基于AT89C51單片機的多功能數字時鐘系統具有高精度、多功能、小體積、低功耗等特點。系統的設計是在模塊化的基礎上設計系統的。基于智能化和模塊化的前提下設計數字時鐘的,通過對設計目標的分析,分立出各個模塊,然后根據各個模塊的功能,選擇適當的芯片進行設計的。對智能化、模塊化設計具有較強的推廣應用價值。

綜上所述,我們可以看到,設計方案三綜合性能良好、造價低廉、且簡單易行。所以我選用第三種設計方案。

1.3 方案三的總體設計框圖 數字時鐘的電路設計總體方框圖如圖1.1所示,使用AT89C51單片機作為控制核心,用七段數碼管來實現時間數字顯示。

圖1.1 總體設計方框圖

第二章 主要元器件介紹2.1 AT89C51的性能介紹AT89C51是一種帶4K字節閃爍可編程可擦除只讀存儲器(FPEROM—Falsh Programmable and Erasable Read Only Memory)的低電壓,高性能CMOS8位微處理器,俗稱單片機。該器件采用ATMEL高密度非易失存儲器制造技術制造,與工業標準的MCS-51指令集和輸出管腳相兼容。由于將多功能8位CPU和閃爍存儲器組合在單個芯片中,ATMEL的AT89C51是一種高效微控制器,為很多嵌入式控制系統提供了一種靈活性高且價廉的方案。

2.1.1 AT89C51的主要特性•與MCS-51 兼容

•4K字節可編程閃爍存儲器

•壽命:1000寫/擦循環

•數據保留時間:10年

•全靜態工作:0Hz-24MHz

•三級程序存儲器鎖定

•128×8位內部RAM

•32可編程I/O線

•兩個16位定時器/計數器

•5個中斷源

•可編程串行通道

•低功耗的閑置和掉電模式

•片內振蕩器和時鐘電路

2.1.2 AT89C51的管腳說明圖2.1.2 AT89C51管腳圖

1.AT89C51的管腳圖如圖2.1.2所示,其說明如下:

- VCC:供電電壓。

- GND:接地。

- P0口:P0口為一個8位漏級開路雙向I/O口,每腳可吸收8TTL門電流。當P1口的管腳第一次寫1時,被定義為高阻輸入。P0能夠用于外部程序數據存儲器,它可以被定義為數據/地址的第八位。在FIASH編程時,P0 口作為原碼輸入口,當FIASH進行校驗時,P0輸出原碼,此時P0外部必須被拉高。

- P1口:P1口是一個內部提供上拉電阻的8位雙向I/O口,P1口緩沖器能接收輸出4TTL門電流。P1口管腳寫入1后,被內部上拉為高,可用作輸入,P1口被外部下拉為低電平時,將輸出電流,這是由于內部上拉的緣故。在FLASH編程和校驗時,P1口作為第八位地址接收。

- P2口:P2口為一個內部上拉電阻的8位雙向I/O口,P2口緩沖器可接 收、輸出4個TTL門電流,當P2口被寫“1”時,其管腳被內部上拉電阻拉高,且作為輸入。并因此作為輸入時,P2口的管腳被外部拉低,將輸出電流。這是由于內部上拉的緣故。當P2口用于外部程序存儲器或16位地址外部數據存儲器進行存取時,P2口輸出地址的高八位。在給出地址“1”時,它利用內部上拉優勢,當對外部八位地址數據存儲器進行讀寫時,P2口輸出其特殊功能寄存器的內容。P2口在FLASH編程和校驗時接收高八位地址信號和控制信號。

- P3口: P3口管腳是8個帶有內部上拉電阻的雙向I/O口,可接收輸出 4個TTL門電流。當P3口寫入“1”后,它們被內部上拉為高電平,并用作輸入。作為輸入,由于外部下拉為低電平,P3口將輸出電流(ILL)這是由于上拉的緣故。

3口也可作為AT89C51的一些特殊功能口,如下所示:

- P3.0 RXD(串行輸入口);

- P3.1 TXD(串行輸出口);

- P3.2 /INT0(外部中斷0);

- P3.3 /INT1(外部中斷1);

- P3.4 T0(記時器0外部輸入);

- P3.5 T1(記時器1外部輸入);

- P3.6 /WR(外部數據存儲器寫選通);

- P3.7 /RD(外部數據存儲器讀選通);

- P3口同時為閃爍編程和編程校驗接收一些控制信號。

- RST:復位輸入。當振蕩器復位器件時,要保持RST腳兩個機器周期的高 電平時間。

- ALE/PROG:當訪問外部存儲器時,地址鎖存允許的輸出電平用于鎖存地址 的地位字節。在FLASH編程期間,此引腳用于輸入編程脈沖。在平時,ALE端以不變的頻率周期輸出正脈沖信號,此頻率為振蕩器頻率的1/6。因此它可用作對外部輸出的脈沖或用于定時目的。然而要注意的是:每當用作外部數據存儲器時,將跳過一個ALE脈沖。如想禁止ALE的輸出可在SFR8EH地址上置0。此時, ALE只有在執行MOVX,MOVC指令是ALE才起作用。另外,該引腳被略微拉高。如果微處理器在外部執行狀態ALE禁止,置位無效。

- /PSEN:外部程序存儲器的選通信號。在由外部程序存儲器取值期間,每 個機器周期兩次/PSEN有效。但在訪問外部數據存儲器時,這兩次有效的/PSEN信號將不出現。

- /EA/VPP:當/EA保持低電平時,則在此期間外部程序存儲器(0000H-FFFFH),不管是否有內部程序存儲器。注意加密方式1時,/EA將內部鎖定為RESET;當/EA端保持高電平時,此間內部程序存儲器。在FLASH編程期間,此引腳也用于施加12V編程電源(VPP)。

- XTAL1:反向振蕩放大器的輸入及內部時鐘工作電路的輸入。

- XTAL2:來自反向振蕩器的輸出。

2.1.3 振蕩器特性XTAL1和XTAL2分別為反向放大器的輸入和輸出。該反向放大器可以配置為片內振蕩器。石晶振蕩和陶瓷振蕩均可采用。如采用外部時鐘源驅動器件,XTAL2應不接。有余輸入至內部時鐘信號要通過一個二分頻觸發器,因此對外部時鐘信號的脈寬無任何要求,但必須保證脈沖的高低電平要求的寬度。

2.1.4 芯片擦除整個PEROM陣列和三個鎖定位的電擦除可通過正確的控制信號組合,并保持ALE管腳處于低電平10ms 來完成。在芯片擦操作中,代碼陣列全被寫“1”且在任何非空存儲字節被重復編程以前,該操作必須被執行。

此外,AT89C51設有穩態邏輯,可以在低到零頻率的條件下靜態邏輯,支持兩種軟件可選的掉電模式。在閑置模式下,CPU停止工作。但RAM,定時器,計數器,串口和中斷系統仍在工作。在掉電模式下,保存RAM的內容并且凍結振蕩器,禁止所用其他芯片功能,直到下一個硬件復位為止。

2.2 74LS373芯片2.2.1 74LS373的基本情況74LS373是常用的地址鎖存器芯片,它實質是一個是帶三態緩沖輸出的8D觸發器,在單片機系統中為了擴展外部存儲器,通常需要一塊74LS373芯片。

74LS373為三態輸出的八 D 透明鎖存器,共有 54/74S373 和 54/74LS373 兩種線路 結構型式,其主要電器特性的典型值如表2.2.1所示:

表2.2.1(注:不同廠家具體值有差別):

1.74LS373的特點:

·三態總線驅動輸出

·置數全并行存取

·緩沖控制輸入

·使能輸入有改善抗擾度的滯后作用

2.2.2 74LS373的內部結構和性能參數74LS373的輸出端 O0~O7 可直接與總線相連,當三態允許控制端 OE 為低電平時,O0~O7 為正常邏輯狀態,可用來驅動負載或總 線。當 OE為高電平時,O0~O7 呈高阻態,即不驅動總線,也不為總線的負載,但 鎖存器內部的邏輯操作不受影響。 當鎖存允許端 LE 為高電平時,O隨數據 D 而變。當 LE 為低電平時,O 被鎖存在 已建立的數據電平。 當 LE 端施密特觸發器的輸入滯后作用,使交流和直流噪聲抗擾度被改善 400mV。

引出端符號:

D0~D7 數據輸入端

OE 三態允許控制端(低電平有效)

LE 鎖存允許端

O0~O7 輸出端

1.外部引腿圖:

圖 2.2.2-1

2.邏輯圖

圖 2.2.2-2

3.真值表

表 2.2.2-3 真值表

H:高電平;

L:低電平;

×:不定;

Z:高阻態;

QO:建立穩態輸入條件前Q 的電平.

2.3七段數碼管的引腳圖及使用在LED顯示電路中,我使用共陰極的七段數碼管作為LED顯示電路的主要元器件。

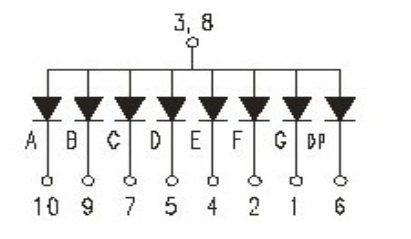

2.3.1七段數碼管的引腳圖圖2.3.1-1所示的是七段數碼管的引腳圖,其中共陽極數碼管引腳圖和共陰極的是一樣的。

圖2.3.1-1 七段數碼管的引腳圖

圖2.3.1-2 七段數碼管的引腳圖

LED數碼管根據LED的接法不同分為:共陰極和共陽極。不同類型的數碼管,除了它們的硬件電路有差異外,編程方法也是不同的。圖2.3.1-2是共陰極和共陽極數碼管的內部電路,它們的發光原理是一樣的,只是它們的電源極性不同而已。

將多只LED的陰極連在一起即為共陰式,而將多只LED的陽極連在一起即為共陽式。以共陰式為例,如把陰極接地,在相應段的陽極接上正電源,該段即會發光。當然,LED的電流通常較小,一般均需在回路中接上限流電阻。假如我們將"b"和"c"段接上正電源,其它端接地或懸空,那么"b"和"c"段發光,此時,數碼管顯示將顯示數字“1”。而將"a"、"b"、"d"、"e"和"g"段都接上正電源,其它引腳懸空,此時數碼管將顯示“2”。其它字符的顯示原理類同。

2.3.2 數碼管使用條件1.數碼管使用條件如下:

(1) 段及小數點上加限流電阻;

(2) 使用電壓:

a.段:根據發光顏色決定;

b.小數點:根據發光顏色決定;

(3) 使用電流:

a.靜態:總電流 80mA(每段 10mA);

b.動態:平均電流 4-5mA 峰值電流 100mA

第三章 硬件設計系統整體硬件電路由中央處理單元電路(AT89C51)、振蕩電路(Crystal)、復位電路(電解電容)、顯示電路(七段數碼管)、按鍵掃描電路(按鈕)、鬧鐘電路(揚聲器)這六個部分組成。各部分之間相互協作,構成一個統一的有機整體,實現多功能數字時鐘的功能。各部分的硬件電路設計如下:

3.1振蕩電路和復位電路1.使用晶振CRYSTAL和瓷片電容構成振蕩電路。

圖3.1-1振蕩電路

2.使用電解電容、按鈕和電阻構復位電路,單片機根據掃描到的相應端口的電平判斷是否滿足程序跳轉條件,從而實現數字時鐘的復位功能。

圖3.1-2 復位電路

3.2 鬧鐘電路圖3.2 鬧鐘電路

使用揚聲器作為鬧鐘電路的主要元器件,通過接口從AT89C51單片機接受信號,實現鬧鐘功能。

3.3按鍵電路圖3.3 按鍵電路

通過使用九個按鍵分別實現實際時間和鬧鐘時間的設置,AT89C51單片機根據掃描到的相應端口的電平判斷是否滿足程序跳轉條件,從而實現實際時間和鬧鐘時間的設置。

3.4 顯示電路圖3.4 顯示電路

通過使用7SEG-MPX6-CC、電阻和74LS373芯片構成LED顯示電路,經接口從AT89C51單片機接受信號,實現數字時間顯示功能。

第四章 軟件設計按照設計方案的要求,在硬件電路的基礎上,使用匯編語言進行軟件設計,為增加程序可讀性,可分為以下五個功能模塊:

- 主程序,主程序流程圖如圖4.1所示;

- 按鍵掃描子程序, 按鍵掃描子程序流程圖如圖4.2所示;

- 鬧鐘子程序,鬧鐘子程序流程圖如圖4.3所示;

- 中斷服務子程序, 中斷服務子程序流程圖如圖4.4所示;

- 時間顯示子程序, 時間顯示子程序流程圖如圖4.5.1和圖4.5.2所示。

4.1 主程序流程圖主程序是先開始,然后初始化并啟動定時器,在定時器啟動后進行按鍵掃描檢測,檢測完后使用中斷服務實現計數,最后就是顯示時間。主程序流程圖如圖4.1所示。

圖4.1 主程序流程圖

4.2 按鍵掃描子程序流程圖按鍵掃描子程序分為兩部分:當前時間設置和鬧鐘時間設置。按鍵掃描子程序流程圖如圖4.2所示。

圖4.2按鍵掃描子程序流程圖

4.2.1 當前時間設置按鈕掃描當前時間設置按鍵掃描的過程如下:

(1) 首先檢測時間設置按鍵,如果按下,就檢測時針按鍵;如果沒有,就返回開始。

(2) 如果時針按鍵按下,時針就加1;如果沒有,就檢測分針按鍵。

(3) 如果分針按鍵按下,分針就加1;如果沒有,就檢測時針按鍵。

(4) 如果時針按鍵按下,時針就加1;如果沒有,就把時間顯示出來。

4.2.2 鬧鐘時間設置按鍵掃描鬧鐘時間設置按鍵掃描的過程如下:

(1) 首先檢測查看鬧鐘按鍵,如果按下,就顯示鬧鐘時間;如果沒有,就檢測鬧鐘設置按鍵。

(2)如果鬧鐘設置按鍵按下,就檢測鬧鐘時針設置按鍵;如果沒有,就返回開始。

(3) 如果鬧鐘時針設置按下,鬧鐘時針就加1;如果沒有,就檢測鬧鐘分針設置按鍵。

(4) 如果鬧鐘分針設置按鍵按下,鬧鐘分針就加1;如果沒有,就檢測鬧鐘完成設置按鍵。

(5) 如果鬧鐘完成設置按鍵按下,鬧鐘設置完成并顯示當前時間;如果沒有,就返回開始。

4.3 鬧鐘子程序流程圖鬧鐘子程序的功能包括顯示鬧鐘時間、設置鬧鐘時間和鬧鐘停止這三個功能,其流程圖如圖4.3所示。

圖4.3鬧鐘子程序流程圖

4.4 中斷服務子程序流程圖1.定時器中斷時的工作過程是:

- 先將累加器A和寄存器PSW入棧;

- 然后檢測1秒是否到,如果到,秒單元加1;如果沒到,就檢測1分鐘。

- 如果1分鐘到,則秒單元清零,分單元加1;如果沒到,就檢測1小時。

- 如果1小時到,則分單元清零,時單元加1;如果沒到,就檢測1天。

- 如果1天到,則時單元清零,天單元加1;如果沒到,就顯示時間。

圖4.4 中斷服務子程序流程圖

4.5 顯示子程序流程圖顯示子程序分為兩個部分:當時間顯示和鬧鐘時間顯示,他們的流程圖如圖4.5.1和圖4.5.2所示。

4.5.1 當前時間顯示流程圖當前時間顯示子程序可實現當前時間的時、分、針顯示,其流程圖如下:

圖4.5.1當前時間顯示流程圖

4.5.2 鬧鐘時間顯示流程圖鬧鐘時間顯示子程序可實現鬧鐘時間的時、分顯示,其流程圖如下:

圖4.5.2鬧鐘時間顯示流程圖

第五章 仿真軟件5.1 PROTEUS仿真軟件介紹Proteus軟件是英國Labcenter electronics公司出版的EDA工具軟件。它不僅具有其它EDA工具軟件的仿真功能,還能仿真單片機及外圍器件,是目前最好的仿真單片機及外圍器件的工具。Proteus是世界上著名的EDA工具(仿真軟件),從原理圖布圖、代碼調試到單片機與外圍電路協同仿真,一鍵切換到PCB設計,真正實現了從概念到產品的完整設計,是目前世界上唯一將電路仿真軟件、PCB設計軟件和虛擬模型仿真軟件三合一的設計平臺。在編譯方面,它也支持IAR、Keil和MPLAB等多種編譯器。

Proteus軟件是一款功能強大的電路設計分析軟件。在利用其進行單片機的軟件仿真時,僅僅是使用了其部分功能(如使用其中的ISIS智能原理圖輸入系統來繪制電路原理圖)。因此這里主要介紹該部分的相關知識。

5.2 Proteus ISIS智能原理圖輸入系統1.Proteus ISIS 是Proteus軟件的核心,具有以下特性:

(1)出版高質量的原理圖:ISIS提供給用戶圖形外觀,包括線寬、填充類型、字符庫等的全部控制,使用戶生成精美的原理圖。通過個性化設置,可以生成印刷質量的BMP圖紙,可以方便地供WORD、POWERPOINT等多種文檔使用;

(2)良好的用戶界面:用戶只需要單擊元件的引腳或者先前布好的線,就能實現布線。而且擺放、移動和刪除操作能都直接用鼠標實現,無需去單擊菜單或圖標;

(3)自動走線:只要單擊想要連接的兩個引腳,就能簡單地實現走線。自動走線也能在元件移動時操作,自動解決相應連線。節點能夠自動布置和移除,使連接導線簡單快捷,大大縮短繪圖時間,又避免一些可能的錯誤;

(4)層次設計:ISIS支持層次圖設計,特殊的元件能夠定義為通過電路圖表示的模塊,能夠任意設定層次。模塊可畫成標準元件,在使用中可放置和刪除端口的子模塊電路;

(5)總線支持:使用總線器件和總線布線使電路設計簡明清晰;

(6)豐富的器件庫:超過27000種元器件,可方便地創建新元件。 ISIS的元件庫包含8000多個元件,有標準符號、三極管、二極管、CMOS、微處理器、存儲器元件、模擬IC和運算放大器等;

(7)智能的器件搜索:通過模糊搜索可以快速定位所需要的器件。

2.Proteus ISIS 可運行于Windows 98/2000/XP/Windows 7環境,對計算機的配置要求不是很高。在運行Proteus ISIS的執行程序后,先出現一個啟動畫面,隨機進入Proteus ISIS的編輯環境,如圖5.2所示。

圖5.2 Proteus ISIS的編輯環境

5.3 Proteus ISIS的界面和功能介紹如圖5.3所示,Proteus ISIS的工作界面是一種標準的Windows界面。包括:標題欄、主菜單、標準工具欄、繪圖工具欄、狀態欄、對象選擇按鈕、預覽對象方位控制按鈕、仿真進程控制按鈕、預覽窗口、對象選擇器窗口、圖形編輯窗口。

圖5.3 Proteus 窗口界面圖

(1)原理圖編輯窗口

- 用于繪制電路原理圖的,藍色方框內為可編輯區,元件要放到它里面。注意,這個窗口是沒有滾動條的,可以通過預覽窗口來改變原理圖的可視范圍。

(2)預覽窗口

- 它有兩個功能:一、當從元件列表選擇一個元件時,顯示該元件的預覽圖;二、當你的鼠標箭頭落在原理圖編輯窗口時,顯示整張原理圖的縮略圖,并會顯示一個綠色的方框,綠色的方框里面的內容就是當前原理圖窗口中顯示的內容。因此,可用鼠標在它上面點擊來改變綠色的方框的位置,從而改變原理圖的可視范圍。

(3)模型選擇工具欄

① 主要模型(Main Modes)

●1 用于編輯元件參數 (默認選擇的);

●2 選擇元件(components);

●3 放置連接點;

●4 放置標簽(用總線時會用到);

●5 放置文本;

●6 用于繪制總線;

●7 用于放置子電路 。

② 配件模型(Gadgets Modes))選擇工具欄

●1 終端接口(terminals) ,有 VCC、地、輸出、輸入等接口;

●2 器件引腳:用于繪制各種引腳;

●3 仿真圖表(graph) :用于各種分析,如 Noise Analysis;

●4 錄音機;

●5 信號發生器(generators);

●6 電壓探針:使用仿真圖表時要用到;

●7 電流探針:使用仿真圖表時要用到;

●8 虛擬儀表:有示波器等。

③ 2D 圖形

(2D Graphics)

●1 畫各種直線;

●2 畫各種方框;

●3 畫各種圓;

●4 畫各種圓弧;

●5 畫各種多邊形;

●6 畫各種文本;

●7 畫符號;

●8 畫原點等。

用于挑選元件(components)終端接口(terminals)信號發生器(generators)仿真圖表(graph)等。舉例,當你選擇“元件(components)”單擊“P”按鈕會打開挑選元件對話框,選擇了一個元件后該元件會在元件列表中顯示,以后要用到該元件時,只需在元件列表中選擇即可。

(5)方向工具欄

旋轉:

旋轉角度只能是 90 的整數倍。成水平翻轉和垂直翻轉。

使用方法:先右鍵單擊元件,再點擊(左擊)相應的旋轉圖標。

(6)仿真工具欄

仿真控制按鈕

●1 運行;

●2 單步運行;

●3 暫停;

●4 停止。

第六章 仿真調試使用Proteus軟件進行仿真調試

6.1 仿真原理圖根據設計方案,將各部分電路進行組合,可得仿真原理圖如6.1所示:

圖6.1 仿真原理圖

6.2 系統調試1.雙擊單片機出現如圖6.2-1所示的畫面,在Program File一欄中選擇仿真項目的源程序代碼文件,點擊OK。

圖6.2-1 加載源程序圖

2.點擊菜單中的“Source”—“Build All”,得到如圖6.2-2所示的“Build Log” 。

圖6.2-2 檢查日志圖

6. 3 仿真單擊Play按鈕,進入仿真狀態,得到仿真結果如圖6.3-1和圖6.3-2所示:

圖6.3-1 仿真結果一

圖6.3-2 仿真結果二

結束語經過幾周的努力,我終于完成了這一份數字時鐘的設計。本次數字時鐘電路采用AT89C51單片機作為控制核心,使用按鈕設計控制電路,結合LED顯示屏、74LS373和電阻來實現了時、分、秒的顯示,采用揚聲器實現鬧鐘功能。雖然達到了設計要求,但是還存在有待改善和提高的地方。

通過這份設計,我發現自己在編寫軟件程序方面的不足,也提高了我設計硬件電路和編寫軟件程序的能力。同時,通過這份畢業設計,讓我明白:實踐和理論有很大的聯系,又高于理論。要把課本上所學的知識跟實際聯系起來,才能把理論變成實際。本次電路的設計既鞏固了我從課本上所學的知識,也使我把理論與實際結合起來,增強了學習的興趣,考驗了我們借助圖書館、互聯網搜索、查閱相關資料的綜合能力。

在學習過程中,要理論聯系實際、學以致用,把所學的理論知識用到實際當中,通過實踐把所學的理論知識進行鞏固。以上,就是我在這次畢業設計中的收獲,這為我以后從事電子電路設計、研制電子產品領域的工作提供了寶貴的經驗。

參考文獻

[1] 李朝青. 單片機原理及接口技術(簡明修訂版). 杭州; 北京航空航天大學出版社,1998

[2] 李廣弟. 單片機基礎[M]. 北京; 北京航空航天大學出版社,1994

[3] 閻石. 數字電子技術基礎(第三版). 北京; 高等教育出版社,1989

[4] 梁炳東. 單片機原理與應用(第一版).北京;人民郵電出版社,2009.

[5] 高衛東,辛友順,韓彥征. 51單片機原理與實踐[M]. 北京; 北京航空航天大學出版社,2008

致 謝

這份關于數字時鐘制作的畢業設計是在xxx老師的熱情關懷和悉心指導下完成的。從設計的選題,相關資料的查尋,到論文的撰寫這一整個過程中,xxx老師以其廣博的知識、豐富的經驗 、清晰的思路,為我細心指導和幫助。他嚴謹的治學態度,精益求精的工作作風和孜孜不倦的求學精神令我受益匪淺,在此,我對鄭譽煌老師表示衷心的感謝!

在完成這份畢業設計的過程中,我也得到了許多同學的建議和幫助,在此一并致以真誠的謝意,感謝所有幫助過我的老師和同學們!

最后,感謝在百忙中抽出時間對本畢業設計(論文)進行評審并提出寶貴意見的老師們,謝謝!

附錄1 元器件清單

表附錄1 元器件清單