應用筆記的內容截圖:

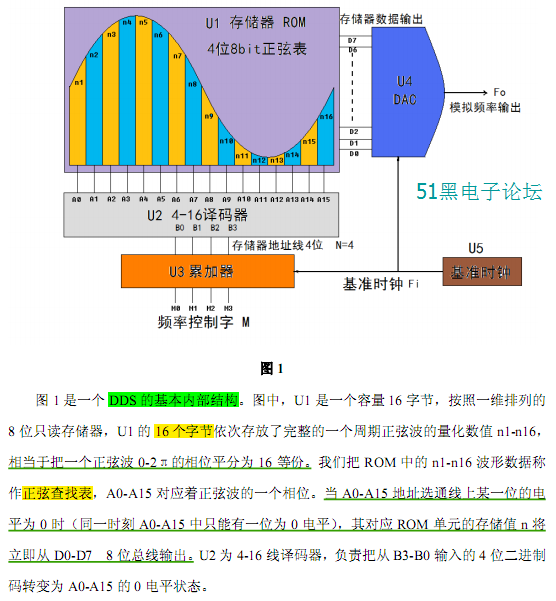

U4 是一個高速數模轉換器(DAC) ,他負責把 D0-D7 輸入的數字信號變成對應的模擬信號,在基準時鐘的驅動下,每個基準時鐘周期轉換一次。例如最大值 n4 對應模擬輸出5V,中間值n8輸出2.5V,最小值n12 對應輸出0V。

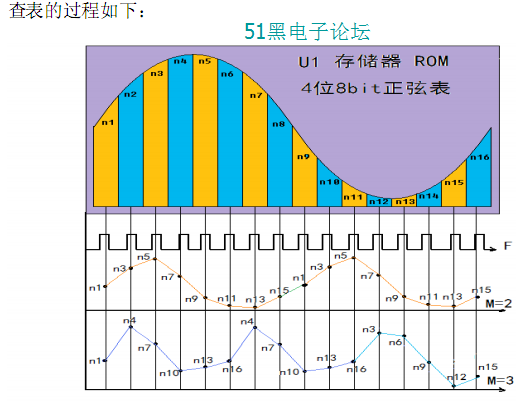

ROM地址總線B0-B3, ROM地址選通線A0-A15 以及ROM數據輸出總線D0-D7 的電平狀態(邏輯關系)如下表:

U3 為相位累加器,它是DDS的結構中最關鍵的算法單元。相位累加器有一個時鐘輸入端,一組頻率控制字輸入總線M3-M0,一組相位地址輸出總線B3-B0。

相位累加器U3 由N位加法器與N位累加寄存器級聯構成。每來一個時鐘脈沖F0,加法器將頻率控制字 M 與累加寄存器輸出的累加相位數據相加,把相加后的結果送至累加寄存器的數據輸入端。累加寄存器將加法器在上一個時鐘脈沖作用后所產生的新相位數據反饋到加法器的輸入端,以使加法器在下一個時鐘脈沖的作用下繼續與頻率控制字相加。此過程的偽代碼表述如下:

If(clock)

B=B+M;

這樣,相位累加器在時鐘作用下,不斷對頻率控制字進行線性相位累加。由此可以看

出,相位累加器在每一個時鐘脈沖輸入時,把頻率控制字累加一次,相位累加器輸出的

數據就是合成信號的相位,相位累加器的溢出頻率就是DDS輸出的信號頻率。用相位累

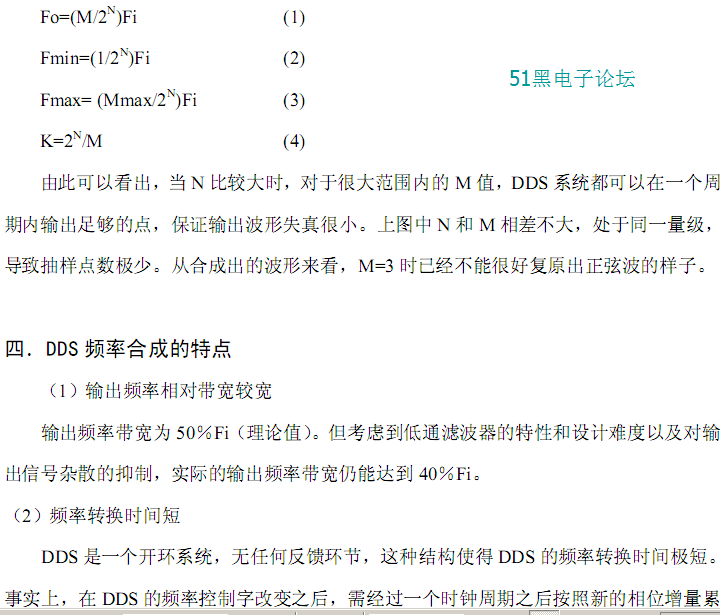

三.DDS 相關計算

由上面的計算規律,我們可以總結出以下幾個公式,各符號的定義為:Fi:基準頻率;Fo:DDS輸出頻率;M:頻率控制字;N:相位累加器位數;K:DDS每個輸出周期的抽樣點數;Fmin:DDS最小輸出頻率(頻率分辨率);Fmax:DDS最大輸出頻率。

完整的pdf格式文檔51黑下載地址(共18頁):

AD9851_應用筆記.pdf

(3.16 MB, 下載次數: 46)

AD9851_應用筆記.pdf

(3.16 MB, 下載次數: 46)

2017-11-12 22:41 上傳

點擊文件名下載附件

ad9851

|