前言隨著電子技術和計算機技術的飛速發展,電子線路的設計工作也日益顯得重要。經過人工設計、制作實驗板、調試再修改的多次循環才定型的傳統產品設計方法必然被計算機輔助設計所取代,因為這種費時費力又費資源的設計調試方法既增加了產品開發的成本,又受到實驗工作場地及儀器設備的限制。為了克服上述困難,加拿大Interactive Image Technologies公司推出的基于Windows 95/98/NT操作系統的EDA軟件。他可以將不同類型的電路組合成混合電路進行仿真。此外,從另一角度來看,隨著計算機技術和集成電路技術的發展,現代電子與電工設計,已經步入了電子設計自動化(EDA)的時代,采用虛擬仿真的手段對電子產品進行前期工作的調試,已成為一種發展的必然趨勢。通過對實際電子線路的仿真分析,從而提高對電路的分析、設計和創新能力。

數字集成電路本身在不斷地進行更新換代。它由早期的電子管、晶體管、小中規模集成電路、發展到超大規模集成電路(VLSIC,幾萬門以上)以及許多具有特定功能的專用集成電路。但是,隨著微電子技術的發展,設計與制造集成電路的任務已不完全由半導體廠商來獨立承擔。系統設計師們更愿意自己設計專用集成電路(ASIC)芯片,而且希望ASIC的設計周期盡可能短,最好是在實驗室里就能設計出合適的ASIC芯片,并且立即投入實際應用之中,因而出現了現場可編程邏輯器件(FPLD),其中應用最廣泛的當屬現場可編程門陣列(FPGA)和復雜可編程邏輯器件(CPLD)。

FPGA(現場可編程門陣列)與 CPLD(復雜可編程邏輯器件)都是可編程邏輯器件,它們是在PAL,GAL等邏輯器件的基礎之上發展起來的。同以往的PAL,GAL等相比較,FPGA/CPLD的規模比較大,它可以替代幾十甚至幾千塊通用IC芯片。這樣的FPGA/CPLD實際上就是一個子系統部件。

本次EDA課程設計就是利用VerilogHDL來設計設計一個自動售貨機,機器設有2個投幣孔,可以接受一元和五角的硬幣,每瓶飲料2.5元,可用2個按鍵來代替。還設有2個輸出,要求有找零和提示信號,分別輸出飲料和找零,編寫一個測試平臺,并通過仿真對該模型進行測試。

一、設計程序Verilog程序源代碼:

- module sell(yi_yuan,wu_jiao, get,half_out,sell_out,reset,clk);

- parameter idle=0, half=1, one=2,two=3,three=4;

- input yi_yuan,wu_jiao,reset,clk;

- output get,half_out,sell_out;

- reg get,half_out,sell_out;

- reg[2:0] s;

- always @(posedge clk)

- begin

- if(reset)

- begin

- sell_out=0; get=0; half_out=0; s=idle;

- end

- else

- case(s)

- idle: begin

- sell_out=0; get=0; half_out=0;

- if(wu_jiao) s=half;

- else if(yi_yuan)s=one;

- end

- half: begin

- if(wu_jiao) s=one;

- else if(yi_yuan)

- s=two;

- end

- one: begin

- if(wu_jiao) s=two;

- else if(yi_yuan)s=three;

- end

- two: begin

- if(wu_jiao) s=three;

- else if(yi_yuan)

- begin

- sell_out=1;get=1; s=idle;

- end

- end

- three: begin

- if(wu_jiao)

- begin

- sell_out=1; get=1; s=idle;

- end

- else if(yi_yuan)

- begin

- …………

- …………

- …………限于本文篇幅 余下代碼請從51黑下載附件…………

`timescale 1ns/1ns

module sell_top;

reg yi_yuan,wu_jiao,reset,CLK;

wire get,half_out,sell_out;

always #50 CLK=~CLK;

initial

begin

CLK =0; reset=1;

#100 reset=0;

yi_yuan=0;

wu_jiao=0;

end

always@(posedge CLK)

begin

wu_jiao={$random}%2;#50 wu_jiao=0;

end

always@(posedge CLK)

begin

if(!wu_jiao)yi_yuan=1;#50 yi_yuan=0;

end

sell m(.yi_yuan(yi_yuan),.wu_jiao(wu_jiao), .get(get),

.half_out(half_out),.sell_out(sell_out),.reset(reset),.clk(CLK));

endmodule

二、程序仿真仿真程序圖 仿真波形及分析

仿真波形及分析

分析前仿真波形,每個時鐘周期為100ns,如圖:在100ns系統復位,到550ns時,輸入5個wu_jiao信號,get和sell_out信號出現告電平,持續100ns,表示賣出和取飲料信號。第三組開始輸入信號:在1050ns且為上升沿時,1個yi_yuan高電平,后接著倆wu_jiao高電平,又一個yi_yuan高電平,half_out/get和sell_out信號出現告電平持續100ns,表示分別有賣出、找零和取飲料信號。在1850ns時第5組測試數據開始,同時為時鐘上升沿,分別有三個wu_jiao和一個yi_yuan高電平,滿足輸出,get、sell_out同時為高,持續100ns,表示分別賣出和取飲料信號。

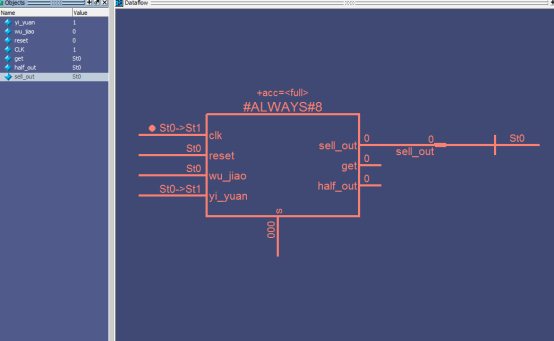

系統的頂層原理圖如下:

1.本次仿真實驗通過對自動售貨機狀態轉換圖的分析得出其工作原理,并根據工作原理編寫出Verilog HDL源程序;

2.通過仿真驗證,該設計能較好的實現自動售貨機的基本功能;

3.根據仿真結果,仿真輸出與理論值相比有一定的延時,這是系統誤差,難以消除。

三、程序說明電路變量分析根據設計要求,共有七個變量。

clk:時鐘輸入;

reset:系統復位信號;

wu_jiao:代表投入五角硬幣;

yi_yuan:代表投入一元硬幣;

half_out:售貨機找回一枚五角硬幣信號;

sell_out:機器售出一瓶飲料;

get:提示投幣者取走飲料。

四、知識點說明1、從仿真的角度來說,HDL語言面對的是編譯器(如Modelsim等),相當于軟件思路。 這時:

wire對應于連續賦值,如assign

reg對應于過程賦值,如always,initial

從綜合的角度來說,HDL語言面對的是綜合器(如DC等),要從電路的角度來考慮。 這時:

1、wire型的變量綜合出來一般是一根導線; 2、reg變量在always塊中有兩種情況:

(1)、always后的敏感表中是(a or b or c)形式的,也就是不帶時鐘邊沿的,綜合出來還是組合邏輯

(2)、always后的敏感表中是(posedge clk)形式的,也就是帶邊沿的,綜合出來一般是時序邏輯,會包含觸發器(Flip-Flop)

2、verilog中always@(posedge clk)無競爭冒險,因為這是時序電路,a和c值的更新是在時鐘沿到來時才會被采樣的,你所看見的一個時鐘周期,就是周期的概念,是延遲一周期后才賦值的,比如在0時刻,你給b,a一個初值1,1,而之前b,a值為0,0,則此時a為0的那個值賦給c,b為0值賦給a,在運行完這之后,由于有新值a=1,a值變化,a為1,即此時a=1,b=1,c=0,在下個周期時,c才等于1的。

3、#加數字表示延遲

4、Verilog中Timescale的用法

(1)`timescale 1ns / 1ps,含義為:時延單位為1ns,時延精度為1ps。

(2)在編譯過程中,`timescale會影響其后面所有模塊中的時延值,直至遇到另一個`timescale指令或`resetall指令。

(3) 當一個設計中的多個模塊帶有自身的`timescale編譯指令時,模擬器將定位在所有模塊的最小時延精度上,并且所有時延都相應地換算為最小時延精度。

5、$random(seed)是verilog中最簡單的產生隨機數的系統函數,給$random傳入了參數seed。

6、reg [2:0]s:定義一個三位的計數器

7、parameter 作用于聲明的那個文件;`define 從編譯器讀到這條指令開始到編譯結束都有效,或者遇到`undef命令使之失效。狀態機的定義可以用parameter 定義,但是不推薦使用`define 宏定義的方式,因為'define 宏定義在編譯時自動替換整個設計中所定義的宏,而parameter 僅僅定義模塊內部的參數,定義的參數不會與模塊外的其他狀態機混淆。

五、實驗結論及總結 通過此次仿真實驗—基于狀態機的自動售貨機的設計,我掌握了Quartus II軟件的基本使用方法以及Verilog HDL語言的語法特點,可以初步編寫一些邏輯功能較為簡單的源程序。同時,通過此次實驗,我掌握了設計工作的完整流程,為以后的課程設計積累了寶貴的經驗。最后,實驗過程中難免遇到一些問題,我們要冷靜分析,找出原因。總之,通過此次實驗,我學到了許多有益的知識。