Tek出的關于時鐘恢復的學習資料,相當不錯,深入淺出,值得學習

目錄

時鐘恢復概述4-5

為什么使用時鐘恢復4

時鐘和數據恢復是如何工作的4

壓控振蕩器(VCO)5

鑒相器5

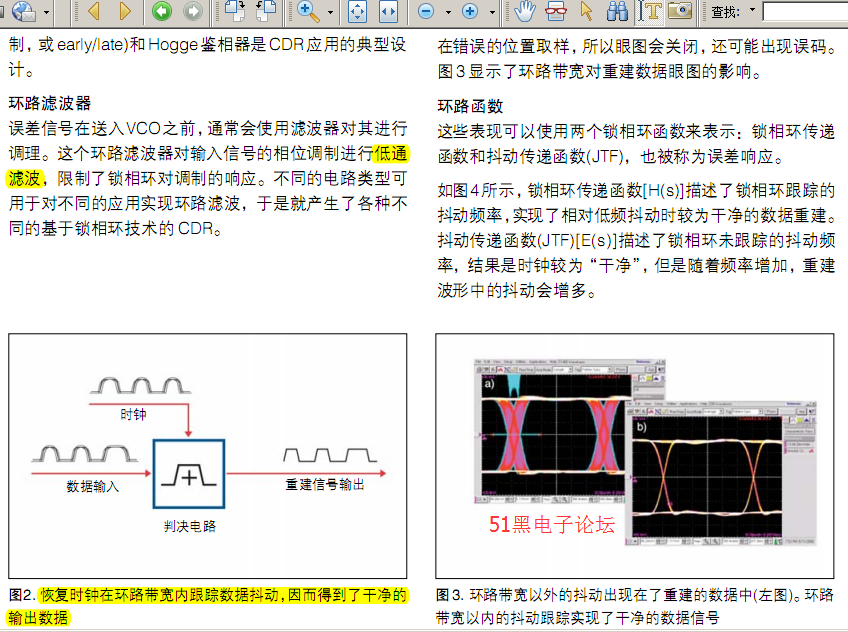

環路濾波器5

環路函數和抖動5-7

抖動跟蹤5

環路函數5

測量反應7

環路類型和階數8

峰化的影響

高速串行標準中時鐘恢復的規范10-11

在高速串行測量中時鐘恢復的用途12-14

碼型的影響和非正常鎖定15

碼型的影響15

非正常鎖定15

時鐘恢復和擴頻時鐘16-1

擴頻時鐘概述16

擴頻時鐘和時鐘恢復18

壓力測試時鐘恢復20-22

抖動容限和誤差響應21

有界不相關抖動測試和時鐘恢復21

采樣測量值和延時23

實時示波器直接測量傳輸延時24

結論25

時鐘恢復概述

今天設計和制造高速串行電路,無論時鐘恢復功能是嵌在檢測儀器的功能中,或是被測件接收端的組件,它都是一個非常重要的組成部分。在這個基礎讀物中,我們要看看在高速串行設計中的時鐘恢復,強調它在保證測量準確性和有效性中的重要性。

為什么使用時鐘恢復當高速串行數據率以兩倍甚至三倍的增長時,時鐘的影響巨大。當設計一個分布式時鐘的系統時,66MHz就已經很難了。如果在數吉的數據率下,幾乎不可能在能夠承受的成本內保證時鐘和數據的時序相關性。上吉的數據率下,之前兆級信號中幾乎可以忽略的電路特性,如抖動,會成為設計正常工作、滿足標準規定的最低誤碼率(BER)、保證數字系統可靠操作的障礙。

使用嵌入式時鐘,時鐘信號會和數據流一起傳輸。從數據中直接提取時鐘,傳輸線特性會以相同的方式影響時鐘和數據, 可以正確地重建數據。 當有抖動的影響時, 這一點特別重要。抖動對時鐘和數據的影響是相同的,所以恢復時鐘的抖動和數據同步, 能保證時鐘和數據同相,從而在重建數據時去掉抖動的影響。

在, 嵌入式時鐘的方式在很多高速串行設計中得到使用。嵌入式時鐘有以下兩個顯著優勢:較少的板上時鐘信號路徑和線纜,幫助降低布線的復雜度。

相比分布時鐘系統,較低的時鐘精度要求,可以使用較低成本的時鐘器件。

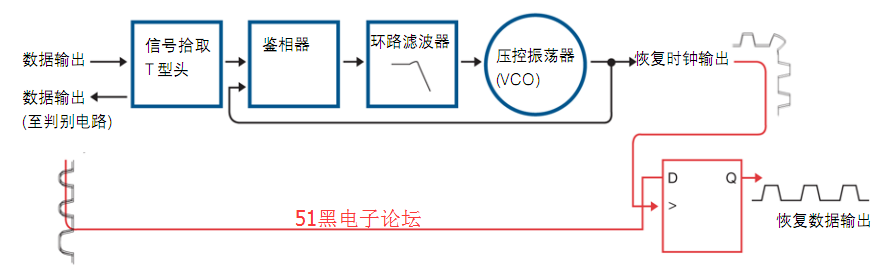

時鐘和數據恢復是如何工作的時鐘和數據恢復(CDR)電路從數據流中得到與之同步的時鐘。然后這個時鐘觸發數據流流過“判決”器件,通常是D觸發器,從而得到恢復的數據信號。

成功的時鐘恢復有賴于能夠發現數據的跳變,同步并鎖定數據率, 而且保持鎖定狀態。 非歸零(NRZ)編碼方式被廣泛用于高速串行構架中,其時鐘必須一直保持鎖定,即使長時間無跳變位也需如此。為了達成這個目標,有可能使用不同的時鐘恢復構架,包括基于硬件的相位內插器(PLs), 通信中的延遲鎖定環(DLLs),以及基于軟件的CDR技術。使用最廣泛的是基于鎖相環(PLLs)的硬件方法。當今高速串行標準提出了一種基于“黃金鎖相環”的時鐘恢復電路模型。圖1圖解了一個基于鎖相環的CDR電路。

完整的pdf格式文檔51黑下載地址(共28頁):

時鐘恢復-高速串行設計測試和測量中的關鍵點.zip

(1012.57 KB, 下載次數: 10)

時鐘恢復-高速串行設計測試和測量中的關鍵點.zip

(1012.57 KB, 下載次數: 10)

2017-10-18 22:47 上傳

點擊文件名下載附件

|