背景:Win10--64位----Quartus II 13.0sp1(64-bit)--Modelsim SE-64 10.1c

本文結(jié)合一個簡單的例程--數(shù)據(jù)選擇器,教大家初步使用Quartus II和Modelsim SE,并進行聯(lián)合調(diào)試,同時也是對自己學習的一個總結(jié)! 0、默認讀者已經(jīng)安裝好Quartus II 13.0sp1(64-bit)和Modelsim SE-64 10.1c;

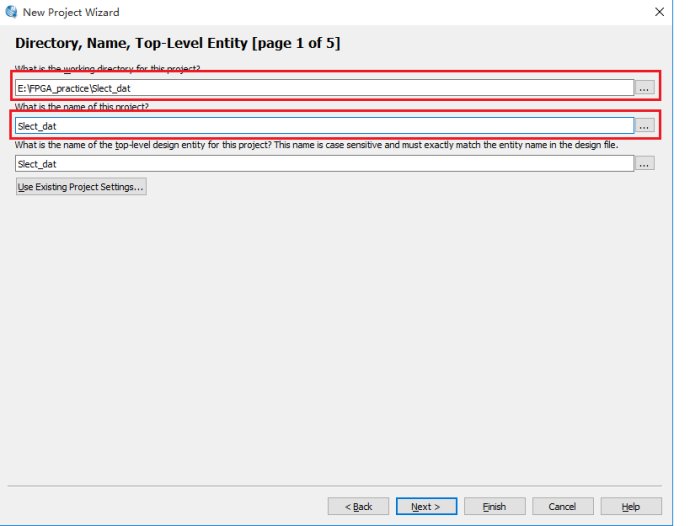

1、建立一個工程:File-->New ProjectWizard 首先彈出Intorduction界面,單擊Next進入下一個界面,設(shè)置工程名和存儲路徑,設(shè)置如下: (工程名和存儲路徑可以隨意設(shè)置,但是建議將工程文件放在一個文件夾內(nèi),如:E:\FPGA_practice\Slect_dat)

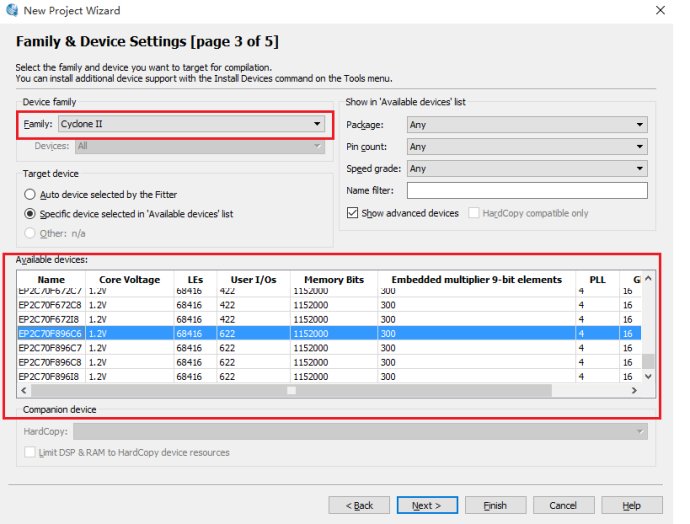

繼續(xù)點擊Next,設(shè)置保持默認,直到彈出Family&DeviceSettings界面,選擇自己的開發(fā)板器件型號,如圖:

(為后面進行板級調(diào)試做準備)

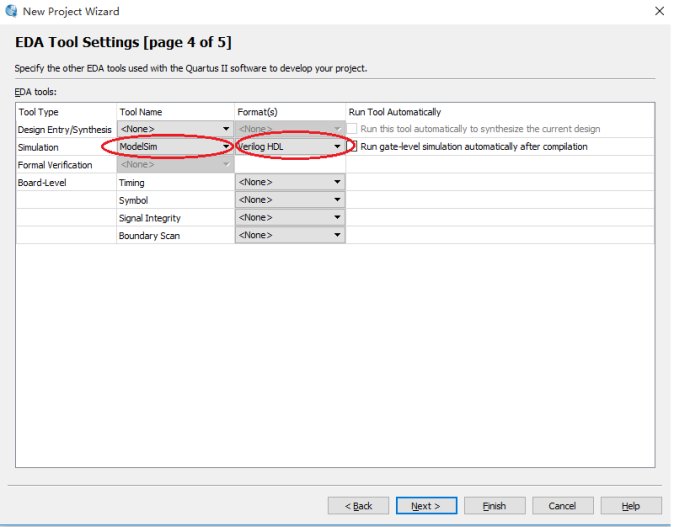

繼續(xù)點擊Next,彈出EDA Tool Setting界面,選擇仿真環(huán)境,設(shè)置如下:

設(shè)置完成后,點擊Finish。

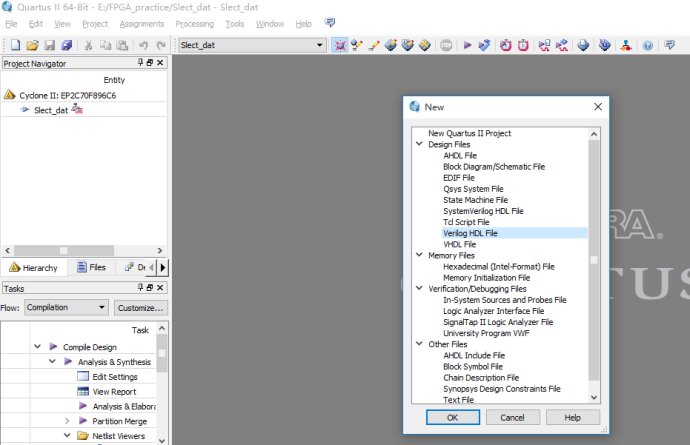

2、新建工程頂層文件:File-->New

彈出如圖所示文件窗口,在這里選擇Verilog HDL file文件

輸入以下測試代碼:

module Slect_dat(

input D0,D1,S,

output reg Y

);

always @(D0,D1,S)

if(S)Y=D1;

else Y=D0;

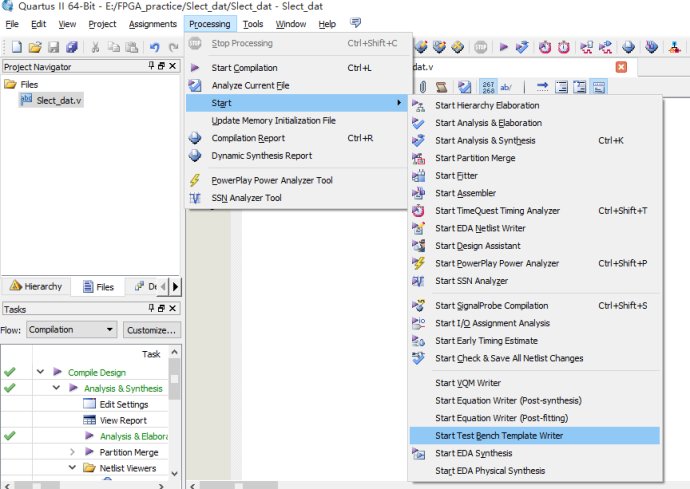

endmodule 然后保存該文件,默認保存路徑為當前的工程文件夾,所以采用默認設(shè)置。保存后,文件會出現(xiàn)在左上角ProjectNavigator框圖里的File文件夾下。 選擇菜單Processing-->StartCompilation,進行編譯,無error即可。 3、建立Verilog HDL測試文件 在新建工程的過程中,我們已經(jīng)設(shè)置了仿真環(huán)境為Modelsim(如果沒有設(shè)置仿真環(huán)境為Modelsim,需要進行配置,配置成功后才能進入下一個環(huán)節(jié)(:Assignments-->Settings-->EDATool Settings-->Simulation,選擇仿真環(huán)境為Modelsim))。 選擇菜單欄下的Processing-->Start-->StartTest Bench Template Writer選項,隨后彈出Test Bench Template Writer WasSuccessful,此時就創(chuàng)建了一個Verilog HDL測試文件,如圖:

剛才生成的VerilogHDL測試文件的默認存儲路徑在工程路徑下的/simulation/modelsim文件夾下,文件名為Slect.vt,在QuartusII 13.0sp1(64-bit)中打開這個文件,刪除原來的內(nèi)容,輸入以下測試代碼,然后重新進行編譯:Processing-->StartCompilation,無error即可。

`timescale 1 ns/ 1 ps

module Slect_dat_vlg_tst(); reg D0;

reg D1;

reg S;

//wires

wire Y; // assign statements (ifany)

Slect_dat i1 (

// port map - connection between master ports andsignals/registers

D0,

D1,

S,

Y

);

initial

begin

// code that executes onlyonce

// insert code here -->begin

// -->end

//$display("Running testbench");

S=0;D1=0;D0=0;

#1 S=0;D1=0;D0=1;

#1 S=0;D1=1;D0=0;

#1 S=0;D1=1;D0=1;

#1 S=1;D1=0;D0=0;

#1 S=1;D1=0;D0=1;

#1 S=1;D1=1;D0=0;

#1 S=1;D1=1;D0=1;

#1 $stop;

end

//always

// optional sensitivitylist

// @(event1 or event2 or .... eventn)

initial

begin

$monitor($time,":\tS=%b\tD1=%b\tD0=%b\tY=%b",S,D1,D0,Y);

end

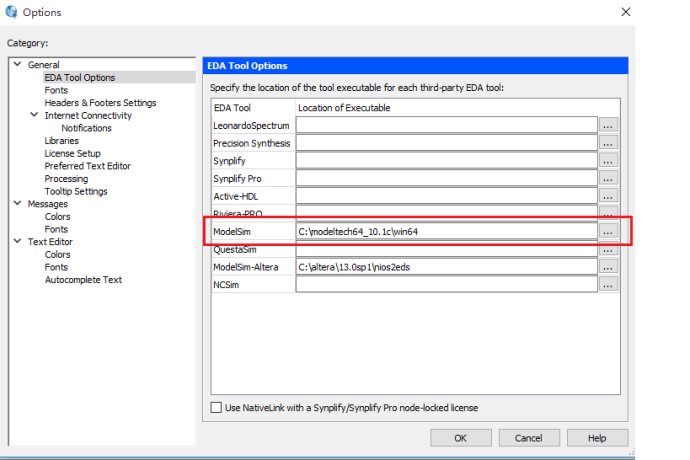

endmodule 4、仿真環(huán)境的詳細配置 選擇菜單欄的Tool-->Options選項,在彈出的窗口中選擇General-->EDA ToolOptions,如圖所示,設(shè)置仿真軟件ModelSim的安裝目錄,然后點擊OK,完成設(shè)置。

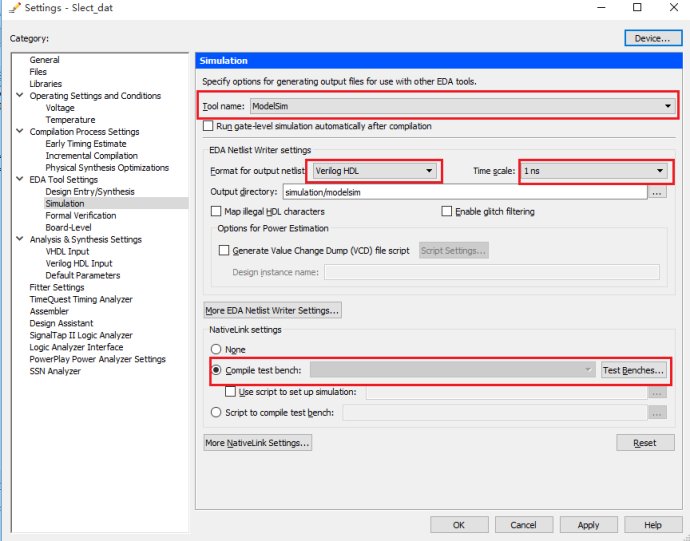

接著選擇菜單欄下的Assignments-->Settings,在彈出的界面中選擇EDA ToolSettings-->Simulation,設(shè)置如下圖所示:

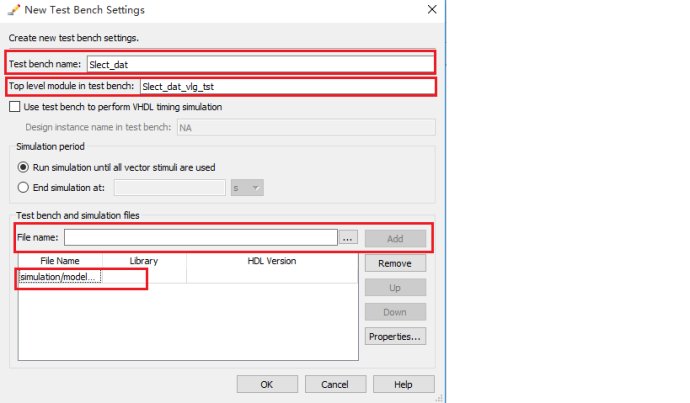

然后點擊上圖中的Text Benches,在彈出的界面中點擊New,如圖進行設(shè)置:

5、開始仿真

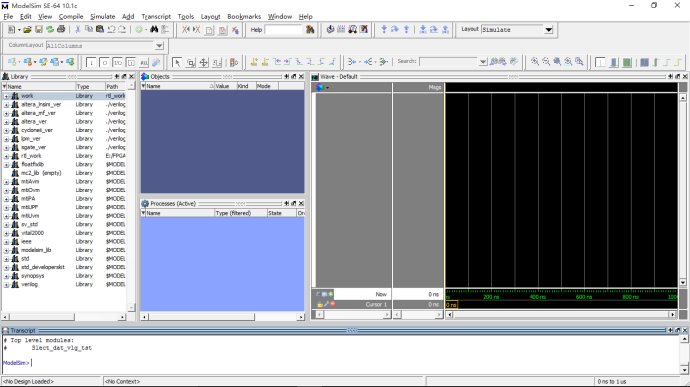

一切準備就緒,選擇菜單欄下面的Tool-->StartSimulation Tool-->RTL Simulation,進行門級仿真,過一會Modelsim SE-6410.1c便會自行啟動,如圖所示:

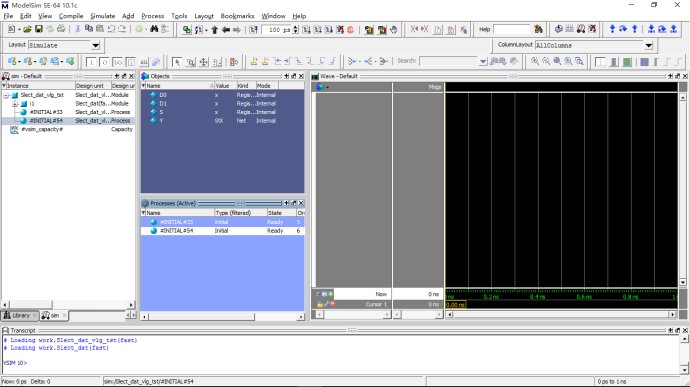

選擇左邊Library框圖下的work-->Select_dat_vlg_tst,點擊右鍵選擇Simulation,彈出界面如圖所示:

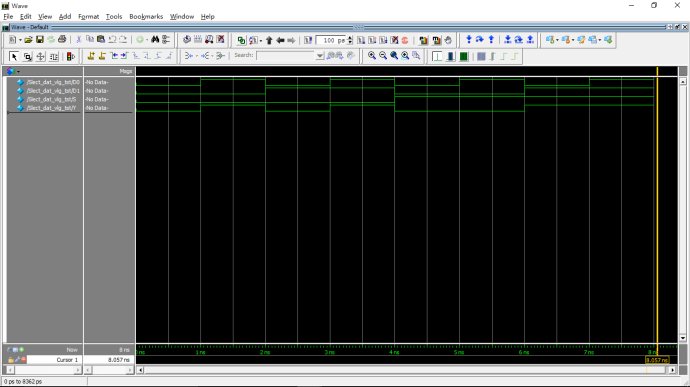

選擇左邊的Sim-Default框圖列表中的Slect_dat_vlg_tst,右擊,選擇Addto-->Wave-->All items inregion,此時Wave-Default框圖的列表中則會出現(xiàn)我們需要觀察的變量,選擇菜單欄Simulate-->Run-->Run-All,系統(tǒng)開始仿真,可以通過觀看波形,驗證系統(tǒng)設(shè)計的正確性!

仿真結(jié)果如圖所示:

GOOD LUCK!

|