本文作者:Miler Shao

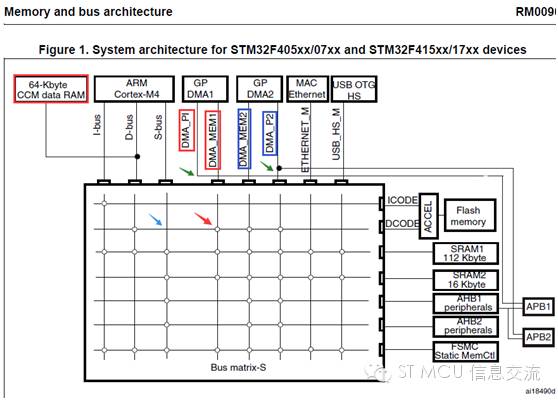

最近有人在STMCU社區網站咨詢如下問題: 由于實驗需要,要用到STM32F407的兩個DMA并用定時器觸發,在使用過程中發現DMA1無法把GPIO的IDR上的數據傳輸到內存,調試過程中出現DMA1的數據流傳輸錯誤標志,但是使用DMA2沒有問題。然后我看了下參考手冊上兩個DMA的控制系統實現圖,DMA1的外設端口有一個橋接器把APB1和AHB1連起來,不知道這個橋連器作用是什么?是把APB1和AHB1連起來互相訪問嗎? 另外測試把GPIO的IDR改成APB1下的tim5的ARR,DMA1正常工作。請問這是怎么回事? 咨詢者提到STM32F4系列中的兩個DMA,即DMA1與DMA2,AHB到APB橋接器;再就是兩個外設,GPIO和TIM5 。為了弄清這個問題,我們有必要先看看STM32F407的總線與存儲框架圖。 如下圖所示:

STM32F4系統存儲及總線框圖

整個系統架構由多層32位AHB總線矩陣及主從總線構成,并建立起各個主從模塊間的互聯訪問。 圖中方框內縱橫交錯的矩陣線就是總線矩陣,猶如縱橫交錯的公路,讓各類交通工具在里面同時運行而互不干擾。只有在圖中紅色箭頭所指的地方,可能出現主控總線訪問撞車的時刻,此時總線矩陣會按照一定規矩進行仲裁,即誰先誰后而不會發生交通事故。 總線矩陣跟圖中上方的8條主控總線和右方的7條從控總線保持互聯。 八條主控總線: [主控總線簡單點說就是可以用來主動訪問別的外設的通路] —Cortex?-M4F 內核 I 總線、D 總線和 S 總線 —DMA1 存儲器總線 —DMA2 存儲器總線 —DMA2 外設總線 — 以太網 DMA 總線 —USB OTG HS DMA 總線 ● 七條被控總線: — 內部 Flash ICode 總線 — 內部 Flash DCode 總線 — 主要內部 SRAM1 (112 KB) — 輔助內部 SRAM2 (16 KB) — 輔助內部 SRAM3 (64 KB)(僅適用于STM32F42xxx 和 STM32F43xxx 器件) —AHB1 外設(包括 AHB-APB 總線橋和 APB 外設) —AHB2 外設 —FSMC 借助于總線矩陣,可以實現主控總線到被控總線的訪問,可以實現多個高速外設并發訪問和高效運行。[需要注意的是,對于STM32F4系列,圖中64K CCM并不經過總線矩陣,只能被CPU訪問。自然DMA是不能訪問它的。] 好,我們接著看看STM32F407 的兩個通用DMA,即DMA1和DMA2。 這兩個DMA都具有雙AHB總線訪問端口,一端用于存儲器訪問,另一端用于外設訪問。同時它們各自都有一個AHB從編程接口,這個不難理解,對它配置編程控制總得有個接口。

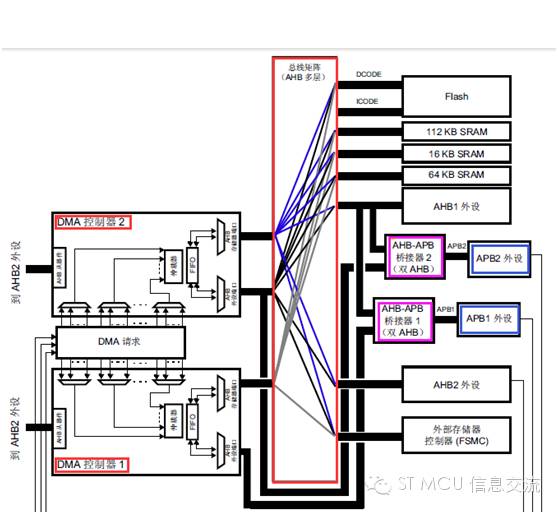

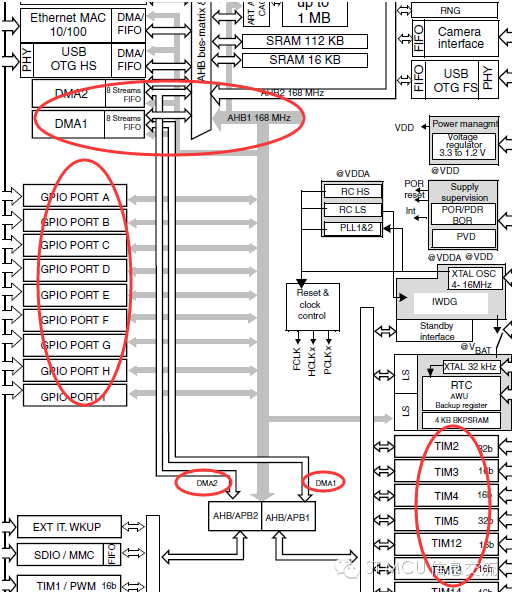

DMA總線訪問框圖 我們結合這幅DMA總線訪問框圖和上面的系統存儲總線框架圖可以明顯看出,2個DMA的外設訪問端口的總線連接有點不一樣。 DMA2的外設訪問端口既與總線矩陣相連,又與AHB-APB橋2相連,可以進一步訪問APB2外設。而DMA1卻沒有與總線矩陣相連,只是跟AHB-APB橋1相連,可以進一步訪問APB1外設。[紅色方框代表總線矩陣] 現在的問題說DMA1訪問不了GPIO,但如果換成TIM5就可以。我們可以去芯片數據手冊的Device overview部分查看相關總線和外設分布圖。我截取STM32F40xblock diagram的部分如下:

我們可以看出GPIO外設跟AHB1相連;TIM5跟APB1相連。而我們從DMA訪問框圖看得清楚,DMA1的外設端口根本沒連接AHB1,自然沒法訪問相應外設,比如GPIO,而DMA2 可以,因為它可以經過總線矩陣后去訪問AHB1的外設。 那DMA1為什么能訪問TIM5呢,因DMA1的AHB外設端口總線經過AHB/APB1橋后就可以訪問APB1各類外設,比方TIM5等。 至于咨詢者問到的兩個橋接器的作用,沒啥過多需要解釋的。橋嘛,連接第一;然后兩邊時鐘的同步和時鐘分頻,滿足不同外設的時鐘需求。 ST MCU的參考手冊里強調了只有DMA2能實現MEMORY到MEMORY的傳輸,DMA1是實現不了的,原理類似。因為要實現M to M 的傳輸,必須兩個端口都能實現對MEMORY的訪問,DMA1的AHB外設端口無法訪問到內部MEMORY。 咨詢者的問題,基本上靠看上面幾幅圖可以得到答案。這些圖很重要,很多信息用圖描述也很直觀明了。各技術手冊里的插圖往往大有乾坤,不要視而不見。上面提到的都是基于STM32F4系列的總線架構,你也可以去看看STM32其它系列的系統總線框圖,相信你一定會另有發現和收獲 |