��������� 51��fan �� 2016-1-31 04:19 ��

����NIOS 91��������(qi��ng)���Д࣬��(d��ng)Ȼ�@���dž��}���P(gu��n)�I���Ҳ�Ԕ�f�������p�IJ��� debug �M(j��n)���Д�n�ο���(x��)��(ji��)���o����������X��������alt_ic_arq_register() ԭ���Լ���(n��i)����int alt_irq_register���Ҳ�֪����ʲô�@�������^������(qi��ng)�ͣ� �f�Ǟ��˱����Ժ�����(j��)�� int alt_ic_isr_register(alt_u32 ic_id, alt_u32 irq, alt_isr_func isr,

void *isr_context, void *flags)

{

return alt_irq_register(irq, isr_context, isr);

} int alt_irq_register (alt_u32 id,

void* context,

alt_isr_func handler)

{

int rc = -EINVAL;

alt_irq_context status; if (id < ALT_NIRQ)

{

/*

* interrupts are disabled while the handler tables are updated to ensure

* that an interrupt doesn't occur while the tables are in an inconsistant

* state.

*/ status = alt_irq_disable_all (); alt_irq[id].handler = handler;

alt_irq[id].context = context; rc = (handler) ? alt_irq_enable (id): alt_irq_disable (id); alt_irq_enable_all(status);

}

return rc;

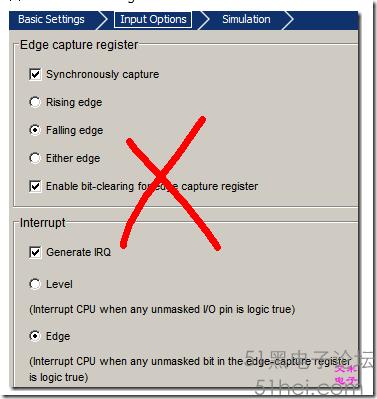

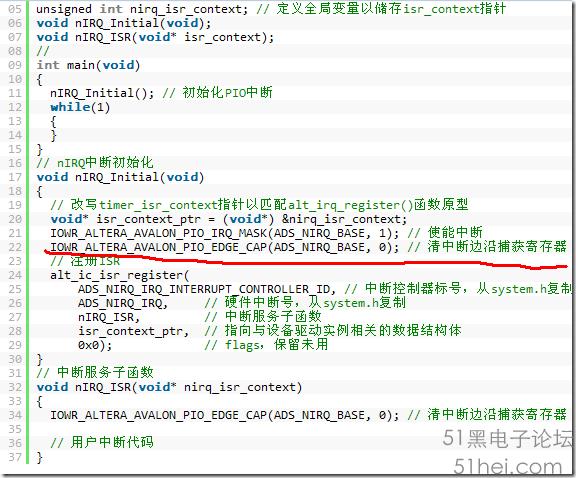

} ��Ⱥ���b�Ď����£�߀��NND�IJ��С��������c���p��o my god�Ĺ�ͬ�f(xi��)���£�߀�Dz��С��������� ���С��ԇԇ���Dz��Ƕ�·���ˆ��}��Ȼ���·����Ȼ�����ˣ����^�^ȥ��SOPC���l(f��)�F(xi��n)���������x��Enable bit_clearing�������@�Ӿ����ˡ� �裬֪��Ȼ����֪��������Ȼ�����҆��}�Ĵ𰸣��������Ǻ���?gu��)���������ʲô��������ͽ�ɽ�Q��n��n�ã��K�ڽ�Q�ˎ���һ��ǰ�Ć��}�Ժ��Ҵ˿����y�ܵ�����������Eanbel bit_clearing�ǵĵ��� ��˼���f�� Bit n ��߅�ز��@�Ĵ����У�������@��ݔ�루����(y��ng)�������أ��½��أ�������(y��ng)λ��λ�͕�(hu��)����1 ��һ��(g��)���C���������O(sh��)�����xȡ߅�ز��@�Ĵ�������Q���l(f��)����PIO���_��߅��׃���� ����x�(xi��ng)��Enable bit_clearing for edge capture register�����P(gu��n)�]���������ֵ��߅�ز��@�Ĵ�������(hu��)������мĴ�������֮����һ��(g��)1���Ĵ�����һ��(g��)�e��λ������(hu��)ʹ��߅�ز��@ʧȥ���á� ����(j��)�ҵČ�(sh��)�H�y(c��)ԇ���(y��n)�C�����ϵ�һЩ��Փ ��1��Enable bit_clearing ���_�ĕr(sh��)�� ��?y��n)�ds�f1 �ĕr(sh��)�����Д࣬����IOWR_ALTERA_AVALON_PIO_EDGE_CAP(KEY_DATA_BASE, 0x03);�����҃ɂ�(g��)���I���Д࣬���}�ɹ���Q�� ��2��Enable bit_clearing �P(gu��n)�]�ĕr(sh��)�� ��?y��n)�ds�f����ֵ���붼����(hu��)������е�߅�ز��@�Ĵ���������IOWR_ALTERA_AVALON_PIO_EDGE_CAP(KEY_DATA_BASE, any vaule);����ʹ��edgecapture���㣬��(sh��)�H�y(c��)ԇ���ˡ�IOWR_ALTERA_AVALON_PIO_EDGE_CAP(KEY_DATA_BASE, 0x00);���͡�IOWR_ALTERA_AVALON_PIO_EDGE_CAP(KEY_DATA_BASE, 0x03);�������_(d��)����Ч������(d��ng)Ȼ��(x��)�T�Ե��҂���(hu��)��0�����㣬���������ٴήa(ch��n)�����`�⡣ �������[���@Щ�����_(d��)��Ŀ���altera��ɶҪ�����ô�����أ����б�Ҫ����� ����(j��)��?gu��)����Ľ�ጣ�������£?/font> ��1����һ����r�£��ⲿ�Д��(hu��)ͬ�r(sh��)�_(d��)�������bit_clearing�@�Û]��ʲô���x�������҂����@���I���ǂ�(g��)���¾��ǂ�(g��)LED����ͬ�r(sh��)���¾�ͬ�r(sh��)�����@��(g��)��ȫ�]���}��ֱ��IOWR_ALTERA_AVALON_PIO_DATA(LED_DATA_BASE, edge_capture);����� ��2�������@����Q�Д�ͬ�����@����r����(d��ng)�Д�ͬ�����@�ĕr(sh��)������bit_clearing���ɻ��ˣ�Ҳ�S���Ը��ӵ��`���?y��n)��Д�ͬ�r(sh��)�_(d��)���ĕr(sh��)��PIO��(d��ng)Ȼ�܉�ͬ�r(sh��)���@�ɂ�(g��)�Д���̖(h��o)�����Ǵ˕r(sh��)main()����(sh��)����Ĉ�(zh��)�оͺ܌����ˣ��ɂ�(g��)�Дൽ�� �l���أ������һ��(g��)��������һ��(g��)���������壬�������� �l�ģ��������^�m(x��)��NIOS2���� �@�ஔ(d��ng)��verilog�еĮ�������Ҫͬ��̎��֮���OK�����������bit_clearing������ͬ�r(sh��)���@�Д��λ����һ����������һ��(g��)��CPU��(zh��)������oCPU���һ��(g��)ԓ �l�ęC(j��)��(hu��)���@��Ҳ����Ч��ֹCPU���C(j��)��TMD���Ӳ����ˣ��� ��?y��n)�PIO IRS�@��(g��)��SOPC��ָ������һ��(g��)IRQ�����ԟo���^��Ƭ�C(j��)�еġ��Д���(y��u)�ȼ�(j��)�����f��������ֻ��ͨ�^bit_clearing���������ķ���CPU ���΄�(w��)�� �����f�������Ͻ��������ZLG�ķ��g���e(cu��)�ˣ���ǰ��Ҳ��(du��)��ds�l(f��)�F(xi��n)�^�e��error������ԭ֭ԭζ��dt���Ǻã� �����һ��(g��)��ʲô��Enable bit_clearing ���_�ĕr(sh��)��IOWR_ALTERA_AVALON_PIO_EDGE_CAP(KEY_DATA_BASE,0x00)��ʲô��(hu��)���C(j��)���������ڳ�ʼ���@��Ԓ�еĆ��}�� ����(j��)altera��dt�������Ϸ����ģ�2�������v���ˮ�(d��ng)���_Enable bit_cleraing�ĕr(sh��)��Ҫ�o����(y��ng)λ��1�����������(bi��o)־λ�����W(w��ng)�Ϻܶ��˶��ǽo0����ģ��@��������?y��n)������]�д��_Enbale bit_clearing���������҂��o��0 �����edagcapture���@�Ӹ�����������Д���(bi��o)־�����һ���������棨���^�������������ò���������Ҳ��������ֻ������˲ſ��ԣ�����(j��)�ҵ��(y��n)�C���˕r(sh��)��1���������(y��ng)��bit���ܺõĽ�Q�ˆ��}��   . . ���}���ˬF(xi��n)�����DZ��^�����ˣ�߀�Ԟ�ALtera�Լ���(j��ng)�������l(f��)�F(xi��n)����ܛ�����}��Ҳ����altera��(j��ng)���������҂��]�кúÿ�ds�� �����f����altara�NJW�������NJW�����ĵܵܣ���ţ���ˣ�MOTO��Ħ���_������Ħ��ҲҪ���������ɴ��ˡ��������������ǂ�(g��)��������˲���һֱ��Թaltera��������������һ�㶼���и����(j��)�ġ� �����N�ϴ��a���Ǻǣ��o�Լ���(g��)�ף� һ����r�£�������Enable bit_clearing��ô���ã��o1 �������h(yu��n)����(hu��)�e(cu��)������ /*

* sys_main.c

*

* Created on: 2011-4-1

* Author: CrazyBingo

*/ #include <stdio.h>

#include "unistd.h"

#include "system.h"

#include "alt_types.h"

#include "sys/alt_irq.h"

//#include "io.h"

#include "altera_avalon_pio_regs.h" //#include "../inc/my_sopc.h"

//#include "../inc/key_scan.h" void key_interrupts(void * key_isr_context);

void key_interrupts_init(void); // ���xȫ��׃���ԃ�(ch��)��߅�ز��@ֵ

volatile int edge_capture; int main(void)

{

key_interrupts_init(); while(1)

{

IOWR_ALTERA_AVALON_PIO_DATA(LED_DATA_BASE, edge_capture);

}

return 0;

} //* ���I�Д��ʼ�� */

void key_interrupts_init(void)

{

/**//* Recast the edge_capture pointer to match the alt_irq_register() function

* prototype. */

void* edge_capture_ptr = (void*) &edge_capture;

/**//* Enable all 2 button interrupts. */

IOWR_ALTERA_AVALON_PIO_IRQ_MASK(KEY_DATA_BASE, 0x03);

/**//* Reset the edge capture register.Enable bit_clearing turn0 off, write any vaule will take effect */

IOWR_ALTERA_AVALON_PIO_EDGE_CAP(KEY_DATA_BASE, 0x03); //active High always take effect

/**//* Register the interrupt handler. */

alt_ic_isr_register

(

KEY_DATA_IRQ_INTERRUPT_CONTROLLER_ID, // �Д��������(bi��o)̖(h��o)����system.h��(f��)��

KEY_DATA_IRQ, // Ӳ���Д�̖(h��o)����system.h��(f��)��

key_interrupts, // �Д����(w��)�Ӻ���(sh��)

edge_capture_ptr, // ָ���c�O(sh��)���(q��)��(d��ng)��(sh��)�����P(gu��n)�Ĕ�(sh��)��(j��)�Y(ji��)��(g��u)�w

NULL // flags�������

);

} //���I�Д����(w��)����(Interrupt service routime),ÿ���½����M(j��n)���Д���(zh��)��һ��

void key_interrupts(void * key_isr_context)

{

/**//* Cast context to edge_capture's type. It is important that this be

* declared volatile to avoid unwanted compiler optimization.

*/

volatile int* edge_capture_ptr = (volatile int*) key_isr_context;

/**//* Store the value in the Button's edge capture register in *context. */

*edge_capture_ptr = IORD_ALTERA_AVALON_PIO_EDGE_CAP(KEY_DATA_BASE);

/**//* Reset the edge capture register. */

IOWR_ALTERA_AVALON_PIO_EDGE_CAP(KEY_DATA_BASE,0x03);

} �K�ڿ����M(j��n)������һ���ˡ�������������----�Еr(sh��)��Q��ʲô�Ƚ�Q��ô�����ӵ�ʹ�࣬���˕r(sh��)��Q�ˎ��������p�ĵ�ʧ�`��ͬ�r(sh��)���ҽK�ڿ��Է���һ���ˣ��@�����?y��n)��@��(g��)�Д࣬��?y��n)�Cyclone III PCB������over�ˣ����^�K�ڽ�Q�ˆ��}�����������_������

|

����TQQ:125739409;���g(sh��)����QQȺ281945664

����TQQ:125739409;���g(sh��)����QQȺ281945664