|

一直做了好久的時序約束,包括源同步輸入數(shù)據(jù)、源同步輸出數(shù)據(jù)以及SDRAM端口的約束,做完這些之后 TimeQuest Timing Analyzer 還是有紅色的 slack 也就是值是負的 不滿足時序約束:如圖: 仔細看其中的錯誤信息都是dcfifo中錯誤,當初還以為altera的ipcore需要特殊的約束呢或者是ipcore有問題,但是這種想法是不對的,fifo這種ipcore是很常用的不應該出問題。一天看到what is false path?于是就百度開始查,看到這樣一篇博客關于FALSE PATH的理解: [size=15.714285850524902px] 對FALSE PATH的理解 [size=15.714285850524902px] [size=15.714285850524902px]

最近做了一點FPGA方面的工作,在用QuartusII對代碼進行綜合時四處查找資料,總算是對FALSE PATH有了一點點的理解,總得來說,F(xiàn)ALSE PATH就是我們在進行綜合分析時,不希望綜合工具進行分析的那些路徑。寫出來和大家一起討論。

在QuartusII的一個培訓文檔里面解釋了什么時候要用到FALSE PATH:

1. 從邏輯上考慮,與電路正常工作不相關的那些路徑,比如測試邏輯,靜態(tài)或準靜態(tài)邏輯。

2. 從時序上考慮,我們在綜合時不需要分析的那些路徑,比如跨越異步時鐘域的路徑。

下面舉例說明:

先看圖1,MUX_1和MUX_2是兩個多路選擇器,MUX_1的使能端C接到時鐘clk,MUX_2的使能端C接到clk的反。于是可以發(fā)現(xiàn)MUX_1的S1端口是不可能經(jīng)過MUX_2的S1端口到達MUX_2的D端口的,同理MUX_1的S2端口是不可能經(jīng)過MUX_2的S2端口到達MUX_2的D端口。于是我們就不希望綜合工具對這兩條路徑進行分析,就是說這兩條路徑就是我們所說的FALSE PATH:

set_false_paths –through Mux_1/S1 –through Mux_2/S1

set_false_paths –through Mux_2/S2 –through Mux_2/S2 [size=15.714285850524902px]

[size=15.714285850524902px]

[size=15.714285850524902px]

[size=15.714285850524902px]圖1 [size=15.714285850524902px]

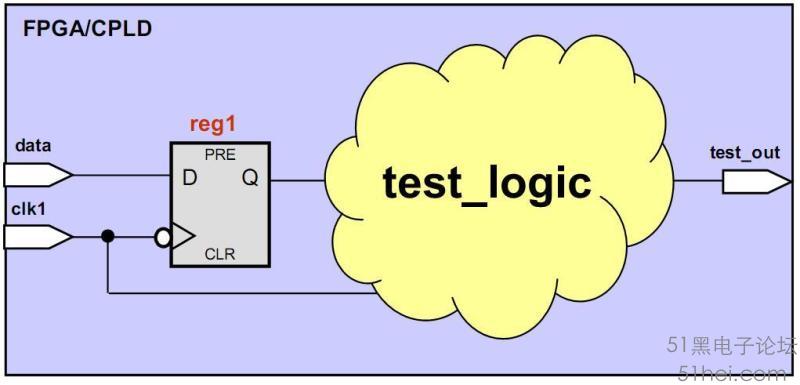

再看圖2,模塊test_logic表示一個測試邏輯,它并不真正實現(xiàn)我們電路的功能,只是為了測試電路功能。所以我們就不希望綜合工具對這這些路徑進行分析,就是說這些路徑就是我們所說的FALSE PATH: [size=15.714285850524902px] [size=15.714285850524902px] [size=15.714285850524902px] [size=15.714285850524902px]圖2 [size=15.714285850524902px] [size=15.714285850524902px]

set_false_path –fall_from clk1–to [get_pins test_logic|*|datain]

set_false_path –from [get_pins test_logic|*|clk] \

-to [get_pins test_logic|*|datain]

set_false_path –from [get_pins test_logic|*|clk] -to [get_ports test_out]

然后看圖3,reg1的輸出和reg2的輸入跨越了不同的時鐘域clk1和clk2,我們不希望綜合工具對這這些路徑進行分析,就是說這些路徑就是我們所說的FALSE PATH:

set_false_path –from [get_pins reg1|clk]–to [get_pins reg2|datain] [size=15.714285850524902px] [size=15.714285850524902px] [size=15.714285850524902px] [size=15.714285850524902px] [size=15.714285850524902px]圖3 [size=15.714285850524902px] [size=15.714285850524902px]最后我們看圖4,clk_100和clk_66仍然是兩個不同的時鐘域,這也是FALSE PATH:

set_false_paths –from [get_clocks clk_100] –to [get_clocks clk_66]

set_false_paths –from [get_clocks clk_66] –to [get_clocks clk_100]

實際上,這兩條FALSE PATH可以用一條命令來代替:

set_clock_groups –exclusive –group {clk_100} \

–group {clk_66} –group {clk_200}

這就涉及到set_clock_groups 命令了,我們以后再說。 [size=15.714285850524902px] [size=15.714285850524902px] [size=15.714285850524902px] [size=15.714285850524902px]圖4對這兩句有感而發(fā) set_false_paths –from [get_clocks clk_100] –to [get_clocks clk_66]

set_false_paths –from [get_clocks clk_66] –to [get_clocks clk_100] 設計中fifo前端時鐘域是cmos_pclk在TimeQuest Timing Analyzer ->Core Cock Setup:pll_c0為(Launch Clock),后端時鐘域是pll_c0在TimeQuest Timing Analyzer ->Core Cock Setup:pll_c0為(Latch Clock)

這兩個是跨時鐘域時鐘,于是根據(jù)文中總結(jié):對于跨時鐘域的處理用set_false_path,約束語句如下: set_false_path -from [get_clocks {cmos_pclk}] -to [get_clocks {pll_c0}]

set_false_path -from [get_clocks {pll_c0}] -to [get_clocks {cmos_pclk}]

ok完美解決 沒有紅色錯誤, slack都為正值。

|