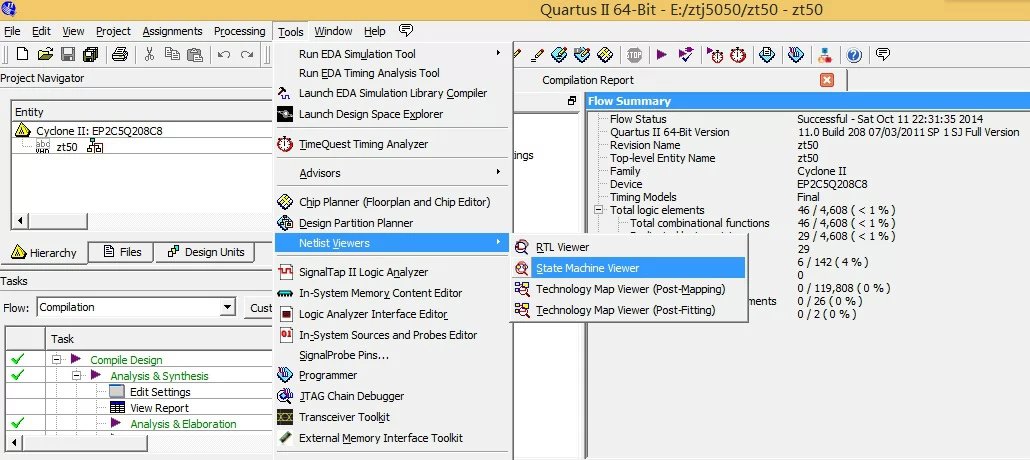

查看狀態機

顯示結果:

Library ieee;

use ieee.std_logic_1164.all;

entity zhuangt is

Port(f10MHz:in bit;

input,reset:in bit;

output:out integer range 0 to 4);

end;

architecture dd of zhuangt is

type state_Type is (s1,s0,s2,s3);

signal state :state_Type;

signal cnt:integer range 0 to 10000000;

signal clk:std_logic;

begin

process(f10MHz)

begin

if f10MHz'event and f10MHz='1' then

if cnt=4999999 then cnt<=0;clk<=not clk;

else cnt<=cnt+1;

end if;

end if;

end process;

Process(clk,reset)

begin

if reset='1' then state<=s0;

elsif clk'event and clk='1' then

case state is

when s0=> state <=s1;

when s1=>

if input='1' then state <=s2;

else state<=s1;

end if;

when s2=>

if input='0' then state <=s3;

else state<=s2;

end if;

when s3=>state<=s0;

end case;

end if;

end process;

process(state,input)

begin

case state is

when s0=>

if input='1' then output<=0;

else output<=4;

end if;

when s1=>

if input='1' then output<=1;

else output<=4;

end if;

when s2=>

if input='1' then output<=2;

else output<=4;

end if;

when s3=>

if input='1' then output<=3;

else output<=4;

end if;

end case;

end process;

end;

|