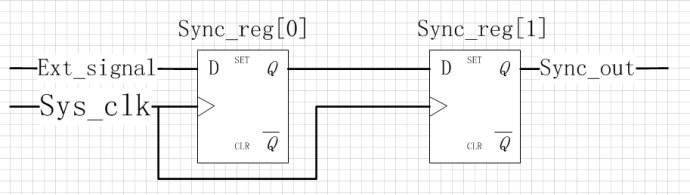

在跨時鐘域中,需要對信號同步才能保證系統(tǒng)的穩(wěn)定。同步的電路設計比較簡單,只需通過2個觸發(fā)器后輸出就能達到同步的目的,同時,為了減少亞穩(wěn)態(tài)發(fā)生的概率也可通過3個觸發(fā)器即可完成。

對應的Verilog代碼:

module sync(

sys_clk,

ext_singal,

sync_out

);

input sys_clk;

input ext_singal;

output sync_out;

reg sync_out;

reg [1:0] sync_reg;

always @(posedge sys_clk)

begin

sync_reg <= {sync_reg[0],ext_singal};

stnc_out <= sync_reg[1];

end

endmodule

對應的電路圖如下:

|