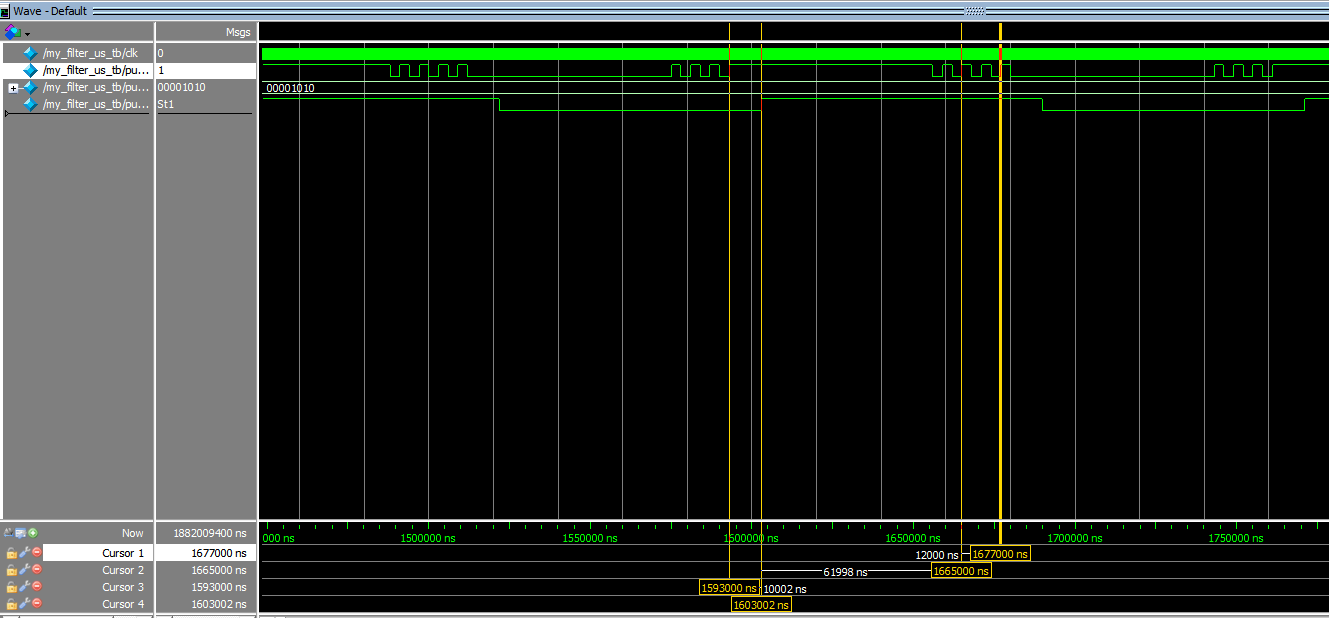

濾波效果如圖所示

直接上代碼

veilog源碼

module my_filter_us(

input clk,//200Mhz

input rst,

input pulse_in,

input[7:0] pulse_delay,//濾波數值輸入,單位us 1-100

output reg pulse_out=1

);

reg[19:0] cnt_delay=0;

reg[3:0] filter_satae=3;

wire[19:0] data;

assign data=pulse_delay*200;

reg[19:0] cnt_rst=0;

reg rst_n=0;

always @(posedge clk)

begin

if(cnt_rst<100000)

begin

cnt_rst<=cnt_rst+1;

end

else

begin

rst_n<=1;

end

end

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

end

else

begin

case(filter_satae)

0: begin

if(pulse_out==0)

begin

filter_satae<=filter_satae+1;

end

else if(cnt_delay<data)

begin

if(pulse_in==0)

begin

cnt_delay<=cnt_delay+1;

end

else

begin

cnt_delay<=0;

//data<=pulse_delay*200;

end

end

else if(pulse_in==0)

begin

pulse_out<=0;

cnt_delay<=0;

end

end

1: begin

filter_satae<=filter_satae+1;

end

2: begin

if(pulse_out==1)

begin

filter_satae<=filter_satae+1;

end

else if(cnt_delay<data)

begin

if(pulse_in==1)

begin

cnt_delay<=cnt_delay+1;

end

else

begin

cnt_delay<=0;

//data<=pulse_delay*200;

end

end

else if(pulse_in==1)

begin

pulse_out<=1;

cnt_delay<=0;

end

end

3: begin

filter_satae<=0;

//data<=pulse_delay*200;

end

endcase

end

end

endmodule

仿真

`timescale 1ns/1ps

module my_filter_us_tb(

);

reg clk=0;

reg pulse_in=0;

reg [7:0]pulse_delay=10;

wire pulse_out;

my_filter_us u1(

.clk(clk),

.pulse_in(pulse_in),

.pulse_delay(pulse_delay),

.pulse_out(pulse_out)

);

initial begin

forever

begin

clk=0; #2 clk=1; #3;//200Mhz

end

end

initial begin

forever

begin

pulse_in=0; #60000;

pulse_in=0; #3000 pulse_in=1; #3000;

pulse_in=0; #3000 pulse_in=1; #3000;

pulse_in=0; #3000 pulse_in=1; #3000;

pulse_in=0; #3000 pulse_in=1; #3000;

pulse_in=1; #60000;

pulse_in=0; #3000 pulse_in=1; #3000;

pulse_in=0; #3000 pulse_in=1; #3000;

pulse_in=0; #3000; pulse_in=1; #3000;

pulse_in=0; #3000; pulse_in=1; #3000;

end

end

endmodule

|