同步降壓芯片TPS40170,發現一篇降低高壓輸入時 TPS40170 的功耗,特分享資料

本文介紹了采用 TI 的 TPS40170 同步 Buck 控制芯片,實現了適合在攝像應用中,寬范圍輸入、高效同步降壓 DC-DC 變換器。文中介紹了在高壓輸入的情況下,如何降低TPS40170的功耗,提高DC-DC變換器的效率。

TPS40170高壓輸入時的功耗分析

TPS40170 的功耗分成兩部分:一是芯片自身控制電路的損耗,二是提供外部 MOS管的驅動部分的驅動功耗。

圖 2 是 TPS40170 的內部框圖。從框圖中可以看到,TPS40170 內部從輸入電壓經過兩個 LDO,分別得到 3.3V 及 8V 兩個電壓。其中 3.3V 主要是給內部邏輯電路供電,8V 電源是給外部 MOS 管驅動供電。

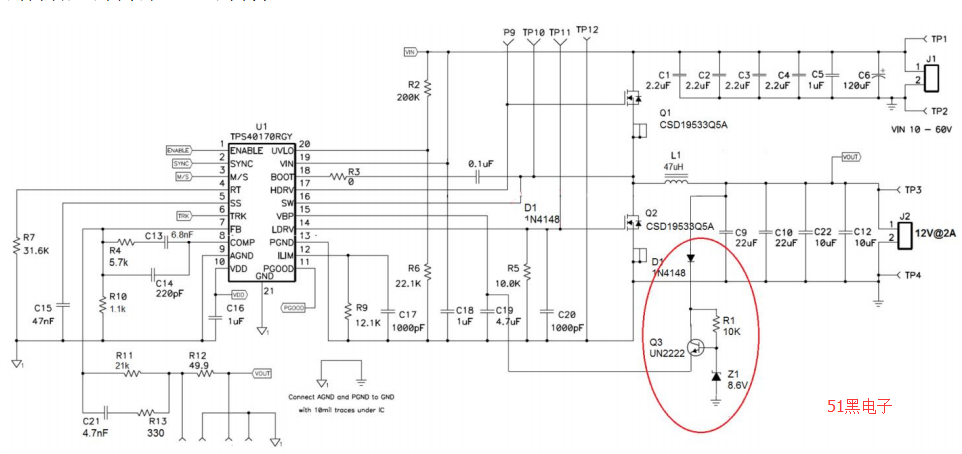

在 48V 輸入,空載輸出情況下,在圖 1 未改進的線路上,跳開 R1,串入萬用表,可測得流入TPS40170 Vin Pin 的電流為 18.5mA。芯片上的損耗為 0.89W 左右,與計算的 0.8W 較為接近。此時,線路的整體輸入電流為51.5mA,線路空載待機功耗2.46W。 在進行改進時,我們需要注意 TPS40170 是采用電壓前饋的電壓控制型芯片,芯片內部對 VDD電壓進行采樣,而產生電壓前饋信號。所以,不能簡單的采用在 VDD 腳外加一個外部低壓電源的方式,該方式會導致在高輸入電壓時,輸出不穩定。

因此,可按圖 4 線路進行修改,在 VBP 腳外加一個 8.4V 左右的電壓(注:VBP 的最大耐受電壓為 8.8V)。需要增加四個元器件,分別是:D1,Q3(NPN 二極管),Z1(8.6V 左右的穩壓管),及 R1。該部分線路的工作原理如下:輸出電壓正常時,Q3, Z1有 R1組成一個線性電源線路,將 VBP的電壓箝位在 8.4V 左右,大于芯片內部 LDO 的輸出,使驅動部分的功耗由外部線性電源線路提供,從而降低芯片內部LDO的功耗。

圖 5 是改進線路與未改進前效率的對比。從實驗可以看出,改進后的線路對 TPS40170 變換器的效率提升有一定的幫助,特別是輕載時,效率提升明顯。在輸入電壓 48V,輸出完全空載時,改進線路的輸入電流為 38.4mA,整體功耗為 1.84W。與原始線路相比,TPS40170 可降低 0.62W 的功耗。

TPS40170 是一款性價比較高的寬范圍 DC-DC 變換器。本文提到的改進線路可以很好的降低TPS40170芯片自身功耗,降低芯片溫升,提高芯片整體的可靠性。

由于 VBP 的外加電壓必須大于 8.3V,該改進線路可以適用與輸出電壓在 10V 以上的應用。10V以下的應用,該線路不是很合適,此時,在高壓輸入時,需要特別考慮 TPS40170 芯片自身的散熱。

以上圖文的PDF格式文檔下載(內容和本網頁上的一模一樣,方便大家保存):

降低高壓輸入時 TPS40170 的功耗.pdf

(936.81 KB, 下載次數: 5)

降低高壓輸入時 TPS40170 的功耗.pdf

(936.81 KB, 下載次數: 5)

2023-9-5 12:35 上傳

點擊文件名下載附件

TPS40170應用

|