一、veilog程序:

module g_b

(

input clk ,

input rst_n,

output out_clk,

output reg out_clk1,

output reg out_clk2,

output reg [3 :0] cnt_1,

output reg [3 :0] cnt_2

);

parameter N = 3 ;

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

begin

out_clk1 <= 0;

cnt_1 <= 1;

end

else

begin

if(out_clk1 == 0)

begin

if(cnt_1 == N/2+1)

begin

out_clk1 <= ~out_clk1;

cnt_1 <= 1;

end

else

cnt_1 <= cnt_1+1;

end

else if(cnt_1 == N/2)

begin

out_clk1 <= ~out_clk1;

cnt_1 <= 1;

end

else

cnt_1 <= cnt_1+1;

end

end

always @(negedge clk or negedge rst_n)

begin

if(!rst_n)

begin

out_clk2 <= 0;

cnt_2 <= 1;

end

else

begin

if(out_clk2 == 0)

begin

if(cnt_2 == N/2+1)

begin

out_clk2 <= ~out_clk2;

cnt_2 <= 1;

end

else

cnt_2 <= cnt_2+1;

end

else if(cnt_2 == N/2)

begin

out_clk2 <= ~out_clk2;

cnt_2 <= 1;

end

else

cnt_2 <= cnt_2+1;

end

end

assign out_clk = out_clk1 | out_clk2;

endmodule

二、module仿真

`timescale 1ns / 1ps

module g_b_tb();

reg sys_clk ;

reg sys_rst_n;

wire out_clk ;

wire [3 :0] cnt_1;

wire [3 :0] cnt_2;

initial begin

sys_clk = 1'b0;

sys_rst_n = 1'b0;

#200

sys_rst_n = 1'b1;

end

always #10 sys_clk = ~sys_clk;

g_b u1(

.clk (sys_clk ),

.rst_n (sys_rst_n ),

.out_clk (out_clk ),

.out_clk1(out_clk1),

.out_clk2(out_clk2),

.cnt_1(cnt_1),

.cnt_2(cnt_2)

);

endmodule

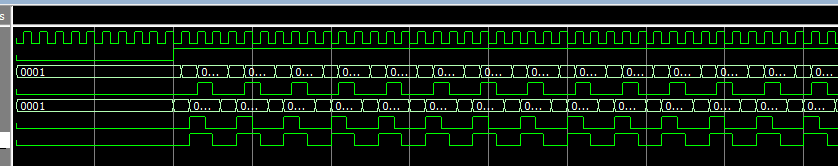

三、仿真時序

|