|

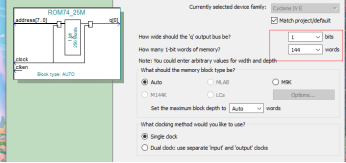

rom ip的配置: 1、寬度1,深度144。

rom

2、

3、這里.mif輸出配置文件,配置文件可在配置altpll ip時獲取。

altpll_recongig 配置 配置成一樣即可。

alt_pll配置 其中rom所需的.mif文件從圖中框選處獲取,或者直接復制圖中序號為1的vga_pll.mif文件也可以(不同的頻率對應不同的mif文件)。 獲取不同pll輸出頻率.mif的具體步驟 1、建立.mif文件

點擊file->New->memory Initialization File 設置 number of words 為144,word size 為1,保存即可,這里需要的時鐘數與.mif文件數對應即可。

2、獲取不同時鐘對應的.mif配置文件(數據)

先配置好輸出的時鐘頻率(Output Clocks界面進行配置)轉到下圖所示的界面,點擊序號為2所在位置的browse ,找到剛剛保存的.mif,然后點擊Generate a Cinfiguration File即可。重復上述步驟可獲取不同的時鐘.mif配置文件。

源碼

module vgaclk_out(

input clk,

input rst,

input[2:0] rom_swn,

output vga_clk,

output reg write_from_rom=0,

output reg reconfig=0,

output busy,

output pll_scandone

);

wire pll_scandataout,pll_areset,pll_configupdate,pll_scanclk,pll_scanclkena,write_rom_ena,pll_scandata;

wire clk_40M,clk_108M,clk_148_5M,clk_27_175M,clk_65M,clk_74_25M;

wire [7:0]rom_address_out;

wire pll_clkout,rom_out;

pll_sw u1(

.clock(clk),

.pll_areset_in(!rst),

.pll_scandataout(pll_scandataout),

.pll_scandone(pll_scandone),

//.read_param(0),

.reconfig(reconfig),//

.reset(!rst),

//.reset_rom_address(0),

.rom_data_in(rom_out),

.write_from_rom(write_from_rom),//

//.write_param(0),

//.counter_param(0),

.pll_scandata(pll_scandata),

//.counter_type(0),

//.data_in(0),

//.data_out(),

.pll_areset(pll_areset),

.pll_configupdate(pll_configupdate),

.pll_scanclk(pll_scanclk),

.pll_scanclkena(pll_scanclkena),

.write_rom_ena(write_rom_ena),

.rom_address_out(rom_address_out),

.busy(busy)

);

wire clk_out;

vga_pll u2(

.areset(pll_areset),

.configupdate(pll_configupdate),

.scanclk(pll_scanclk),

.scanclkena(pll_scanclkena),

.scandata(pll_scandata),

.scandataout(pll_scandataout),

.scandone(pll_scandone),

.inclk0(clk),

.c0(vga_clk)

);

//

ROM108M u3(

.address(rom_address_out),

.clken(write_rom_ena),

.clock(clk),

.q(clk_108M)

);

ROM148_5M u4(

.address(rom_address_out),

.clken(write_rom_ena),

.clock(clk),

.q(clk_148_5M)

);

ROM74_25M u5(

.address(rom_address_out),

.clken(write_rom_ena),

.clock(clk),

.q(clk_74_25M)

);

ROM65M u6(

.address(rom_address_out),

.clken(write_rom_ena),

.clock(clk),

.q(clk_65M)

);

ROM40M u7(

.address(rom_address_out),

.clken(write_rom_ena),

.clock(clk),

.q(clk_40M)

);

ROM27_175M u8(

.address(rom_address_out),

.clken(write_rom_ena),

.clock(clk),

.q(clk_27_175M)

);

rom_sw u9(

.clk(clk),

.rst(rst),

.rom_swn(rom_swn),

.data1(clk_27_175M),

.data2(clk_40M),

.data3(clk_65M),

.data4(clk_74_25M),

.data5(clk_108M),

.data6(clk_148_5M),

.rom_out(rom_out)

);

//用于控制write_from_rom信號和reconfig信號

reg[2:0] SW_IT=3'd0,SWN=3'd7;

//reg[13:0]cnt_sw=14'd0;//8190

always@(posedge clk or negedge rst)

begin

if(!rst)

begin

SW_IT<=0;

SWN<=7;

end

else

case(SW_IT)

3'd0 :begin

if(SWN!=rom_swn)

begin

SW_IT<=3'd1;

write_from_rom<=1;

end

end

3'd1:begin

SW_IT<=3'd2;

write_from_rom<=0;

end

3'd2:begin

if(busy==0)

begin

SW_IT<=3'd3;

reconfig<=1;

end

end

3'd3:begin

SW_IT<=3'd4;

reconfig<=0;

end

3'd4:begin

SW_IT<=3'd0;

SWN<=rom_swn;

end

endcase

end

//assign vga_clk=(rom_swn==SWN)?clk_out:0;

endmodule

rom_sw部分源碼(rom的選擇,不同時鐘的選擇)

module rom_sw(

input clk,

input rst,

input[2:0] rom_swn,

input data1,

input data2,

input data3,

input data4,

input data5,

input data6,

output reg rom_out=0

);

always@(negedge clk)

begin

case(rom_swn)

3'b000:rom_out<=data1;

3'b001:rom_out<=data2;

3'b010:rom_out<=data3;

3'b011:rom_out<=data4;

3'b100:rom_out<=data5;

3'b101:rom_out<=data6;

3'b110:rom_out<=data6;

3'b111:rom_out<=data6;

default: rom_out<=data6;

endcase

end

endmodule

|