利用SystemView及Multisim設計了卷積碼的編解碼過程,,并且有相關參數的測定,內附設計文檔

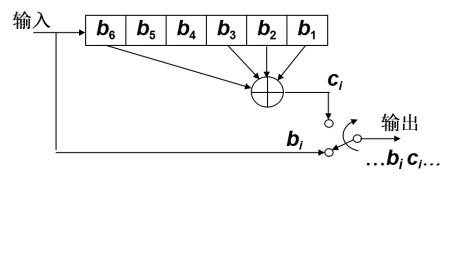

卷積碼編譯碼器設計 (1)利用移位寄存器和異或器實現卷積碼編碼; (2)編碼后信號送入高斯白噪聲信道傳輸; (3)接收端進行大數邏輯解碼譯碼; (4)要考慮實現位同步電路; (5)觀察輸出信號波形與輸入信號波形的相關性,測量誤碼率曲線; (6)基于Systemview/Matlab/Simulink軟件實現。 2 編碼部分 2.1 編碼原理 卷積碼是一種非分組碼,(2,1,6)卷積碼信息位為1,監督位為1,監督位不僅與當前信息段有關還與前面5個信息段有約束關系。卷積碼編碼器由移位寄存器和異或器組成,原理框圖如下。

圖2.1 (2,1,6)卷積碼編碼原理框圖 如圖,信息位的b1,b2,b3,b6異或形成監督位,信息位與監督位交替輸出。 2.2 編碼仿真電路

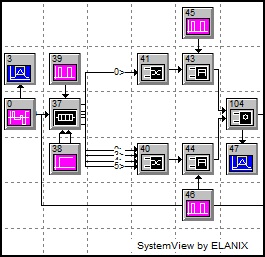

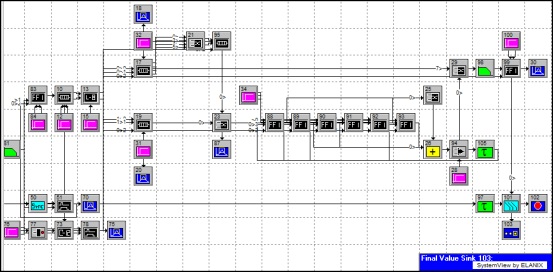

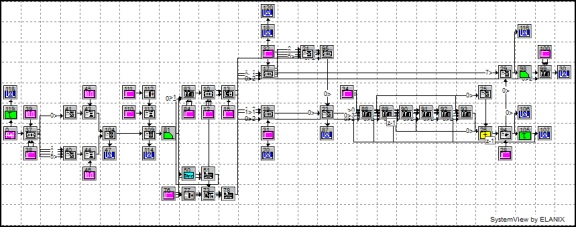

圖2.2 編碼部分仿真電路 上圖為在system view中搭建的電路圖,0號模塊采用PN碼作為信源,頻率為10hz,碼元長0.1s,信息位先存放在移位寄存器中,根據移位寄存器的結構與編碼原理圖對照,移位寄存器的0,3,4,5管腳異或作為監督位,42,43,44,45,46號模塊相當于原理框圖中的開關,45,46模塊為周期10hz的脈沖,一個周期中高低電平各占0.05s,而46模塊相位延遲180,假設45模塊輸出高電平和信息位相與,輸出取決于信息位,此時46號模塊為低電平,44號模塊輸出為0,也就是信息位輸出時,監督位為0,監督位輸出時,信息位為0。 3 位同步

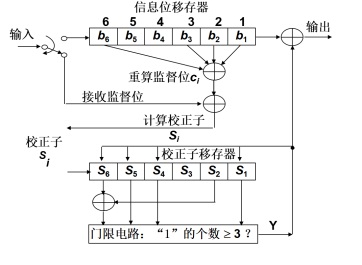

圖3.1 位同步仿真電路 信源經過編碼后,碼元長度變為0.05s,頻率增加了一倍,變成20hz,50號模塊為system view的位同步模塊,設置好參數可以直接輸出位同步信號,51號模塊為單穩態多諧振蕩器,用于保持同步信號的高電平的時間,同時同步信號經過分頻器,作為分離信息位與監督位等后續電路的時鐘。 4 譯碼部分 4.1 譯碼原理 采用大數邏輯譯碼,先將信息位與監督位分離,信息位存放在移位寄存器中,按照編碼的方式重新計算監督位,重新計算的監督位與接收的監督位異或,形成矯正子,若沒有誤碼,重新計算的監督位與接收的監督位相同,矯正子為0,若存在誤碼則矯正子為1,通過矯正子糾正誤碼。

圖4.1 (2,1,6)卷積碼譯碼原理框圖 上圖為(2,1,6)的譯碼原理框圖,信息位暫存于移位寄存器,重新計算監督位,與接收到的監督位異或運算后形成矯正子,矯正子存于移位寄存器中。大數邏輯解碼用正交校驗方程組判斷信息位的對錯,原理如下: S1 = c1 + b1 S2 = c2 + b2 S3 = c3 + b3 S4 = c4 + b1 + b4 S5 = c5 + b1 + b2 + b5 S6 = c6 + b1 + b2 + b3 + b6 監督關系式經過線性變換后形成正交校驗方程組。 S1 = c1 + b1 S4 = c4 + b1 + b4 S5 = c5 + b1 + b2 + b5 S6+S2 = c2 + c6 + b1 + b3 + b6 此時信息位b1同時存在于上面4個式子中,若b1出現誤碼,則S1,S4,S5,S6+S2都為1,若不是b1發生誤碼而是其他碼元發生誤碼,則S1,S4,S5,S6+S2僅有一個為1,從而精確判斷該位信息位是否發生誤碼,若改碼發生誤碼門限電路輸出高電平,與信息位異或,使其取反,從而糾正錯碼,同時利用檢測信號將矯正子清零。 4.2 譯碼仿真電路

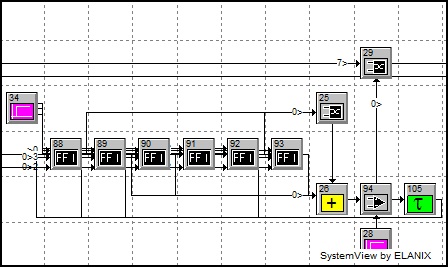

圖4.2 譯碼部分仿真電路 經過信道傳輸和濾波器后,首先抽樣判決,通過移位寄存器于鎖存器分離信息位與監督位,信息位用異或器重新計算監督位,再與接收到的監督位異或形成矯正子,95號模塊移存器用于碼元的對正。

圖4.3 譯碼部分仿真電路 矯正子存放于由D觸發器組成的移位寄存器,方便監測信號反饋清零。按照原理框圖,S6與S2異或后和S1,S4,S5相加,通過94號模塊比較器和28號門限電平3比較,若相加大于等于3,比較器正向輸出口輸出高電平,使信息位取反,同時比較器的反向輸出口延遲一位碼元輸出低電平使移存器清零,這部分電路要求碼元嚴格對正,否則無法糾正錯碼還會增加新的錯碼。

圖4.4 譯碼部分總電路 5 誤碼率仿真

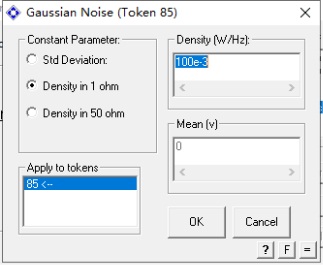

圖5.1 信道部分仿真電路 信道中疊加高斯白噪聲,96號模塊增益設置全局變量使噪聲信號的功率隨loop增加而減小。高斯噪聲以及全局變量的設置如下圖。

圖5.2 高斯噪聲設置

圖5.3 全局變量設置

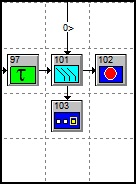

圖5.4 誤碼率監測電路 通過97號模塊延遲器,將信源與輸出碼元對正,送入101比特誤碼率模塊觀測誤碼率。

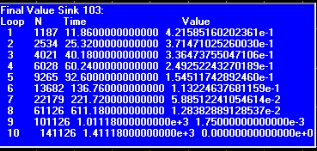

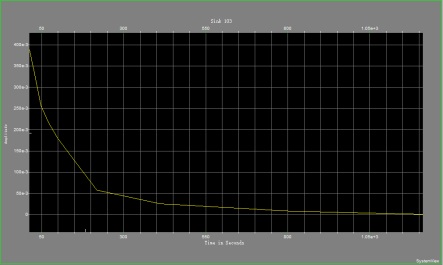

圖5.5 誤碼率 誤碼率可以看出,隨著loop的增加,噪聲的減小,誤碼率呈下降趨勢。103號模塊同時可以描繪出誤碼率曲線,如下圖。

圖5.6 誤碼率曲線

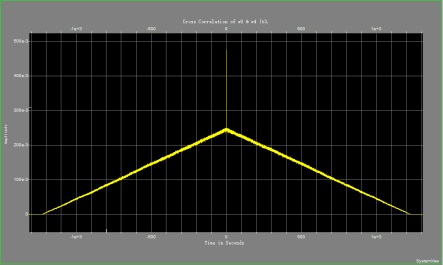

圖5.7 輸出與輸入互相關函數 由相關圖像可知,信源與輸出是相關的。 6 糾正一位錯碼仿真

圖6.1 糾錯仿真電路總圖

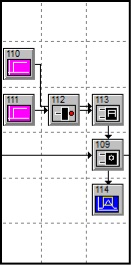

圖6.2 人為添加信道脈沖 與觀測誤碼率不同,信道中不再疊加高斯噪聲。110號階躍模塊起始時間為1s,111號階躍模塊起始時間為1.05s經過反相器后與110號階躍相與,可以人為在1s處加入碼元寬度的脈沖,造成誤碼。

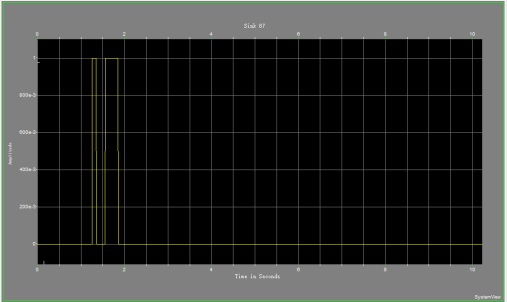

圖6.3 矯正子波形 上圖為87號模塊示波器觀測的矯正子波形,這說明加入的脈沖此時確實產生了誤碼。

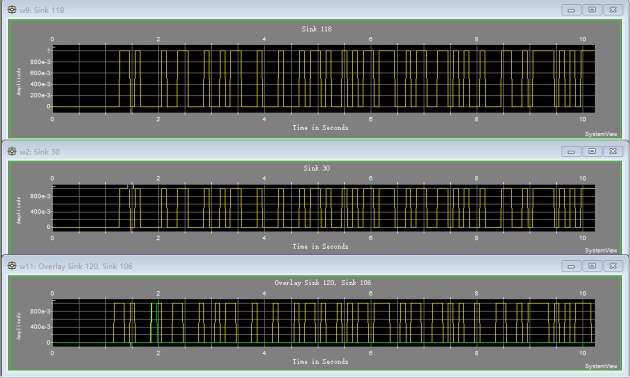

圖6.4 對比觀測圖 最上方為118號模塊示波器觀測的波形,是信源延時后觀測的波形,中間為116號示波器觀測的譯碼完成后的波形,對比觀測上方和中間兩幅圖可以看到輸出和信源一樣,這一位誤碼被糾正了。最下面黃色的波形為120號示波器觀測的接收后的信息位,綠色的波形為106示波器觀測的矯正子相加比較經過門限電路的輸出,同時對比信源的波形可以看到,信息位有一位的誤碼,這一位誤碼被門限電路的輸出糾正過來了。 7 電路級仿真 采用Multisim進行仿真,信源采用4級線性反饋移位寄存器生成的15位m序列,電路如下圖。

圖7.1 信源生成電路

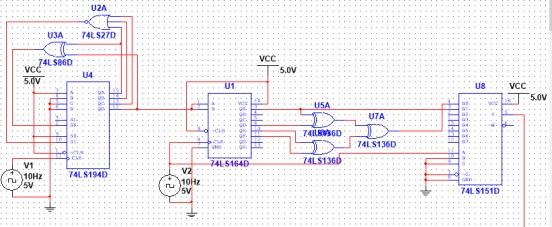

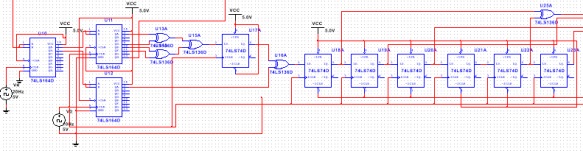

根據原理框圖和system view的仿真電路搭建編碼仿真電路,系統級仿真電路里,信息位與監督位二合一的部分實現比較麻煩,采用數據選擇器并入串出,實現該功能,如下圖。

圖7.2 編碼仿真電路

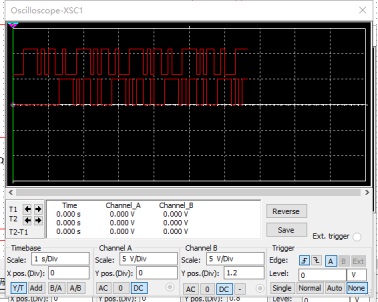

圖7.3 信源波形

圖7.4 編碼后波形 編碼時,信源先經過一次移位寄存器,所以最前面m序列多出一個0,為了方便分析,只選取前幾位,觀察波形可知,信源為0000111101011001,編碼后波形為00000000111111100010011111010011,經過計算后,符合原理規律。

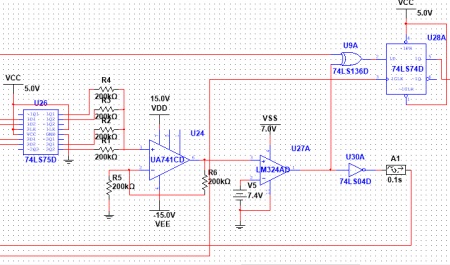

圖7.5 譯碼部分電路 根據原理框圖和system view已做好的電路,前面的譯碼部分電路可以直接使用,而system view中的加法器和比較器可以用運算放大器實現,如下圖。

圖7.6 相加電路與門限電路 加法運算之前,通過鎖存器對波形進行抽樣整形,1信號為5伏,0信號為0伏,加法電路由ua741構成,比較電路由lm324構成,根據同向加法器的原理的計算,每加一個1,輸出上升2.5伏,當S1,S4,S5,S6+S2相加超過3時,輸出大于7.5伏,門限值選擇7.4伏略低于7.5伏,這部分電路單獨仿真驗證過,符合預期計算。

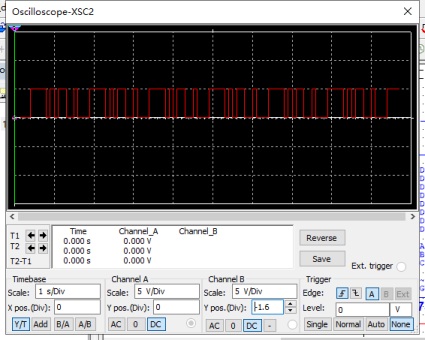

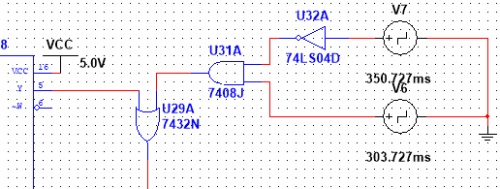

圖7.7 信道人為添加脈沖 與之前的驗證相同,在信道中人為添加脈沖,使其在信息位中產生誤碼,信源由最初的0000111101011001變為0001111101011001。

圖7.8 譯碼分離的信息位與門限電路輸出對比圖 由上圖可以觀察到,門限電路輸出的高電平正好對應誤碼位置,由此糾正誤碼。

圖7.9 信源與譯碼對比圖 根據信源與譯碼對比觀察,譯碼后波形與信源相同,誤碼得以糾正。 8 總結與體會 紙上得來終覺淺,學習過理論課后僅僅了解了卷積碼的工作原理,自己動手實踐才發現有很多細節需要注意。在門限電路的輸出不僅可以糾正一位誤碼,還用于矯正子的清零,而一開始注意到延遲就將比較器反向輸出的信號送入觸發器的清零端,導致其輸出不是矩形波而是三角波;做譯碼部分的時候,沒有注意到碼元的嚴格對正,無法驗證糾正一位誤碼。親自動手實踐后,對卷積碼的理論有了更加深刻的理解和認識。

51hei.png (3.7 KB, 下載次數: 90)

下載附件

2021-7-8 05:28 上傳

全部資料51hei下載地址:

systermview卷積碼設計.zip

(1.03 MB, 下載次數: 42)

systermview卷積碼設計.zip

(1.03 MB, 下載次數: 42)

2021-7-7 16:17 上傳

點擊文件名下載附件

下載積分: 黑幣 -5

|