|

數字時鐘是一種用數字電路技術實現時、分、秒計時的裝置,與機械式時鐘相比具有更高的準確性和直觀性,且無機械裝置,具有更長的使用壽命,已得到廣泛的使用。數字時鐘的設計方法有許多種,例如,可用中小規模集成電路組成電子鐘;也可以利用專用的電子鐘芯片配以顯示電路及其所需要的外圍電路組成電子鐘;還可以利用單片機來實現電子鐘等等。數字時鐘的組成一般由計數器、譯碼器、顯示器、振蕩器及分頻器等幾部分組成。振蕩器產生的時標信號送入分頻器,分頻器將其送入的時標信號分頻成秒脈沖信號。再把秒脈沖送入計數器進行計數,并把累計的計數結果以“時”、“分”、“秒”的數字顯示出來。“秒”的顯示由二級計數器和譯碼器組成六十進制計數器電路來實現,“分”的顯示電路與秒相同。“時”的顯示由二級計數器和譯碼器組成的二十四進制計數器電路來實現。 數字鐘已成為人們日常生活中必不可少的物品,廣泛用于個人家庭以及車站、碼頭、劇場、辦公室等公共場所,給人們的生活、學習、工作、娛樂帶來極大的方便。鐘表的數字化給人們生產生活帶來了極大的方便。它擴展了鐘表原有的報時功能,諸如定時自動報警、按時自動打鈴、時間程序自動控制、定時廣播、定時啟閉電路、定時開關烘箱、通斷動力設備,甚至各種定時電氣的自動啟用等,這些都是以鐘表數字化為基礎的。因此,研究數字電子鐘以及擴大其在生活中的應用,有著非常現實的意義。 盡管目前市場上已有現成的數字鐘集成電路芯片,價格便宜,使用也非常方便。鑒于數字鐘電路的基本組成包含了數字電路的主要組成部分,為了幫助同學們將已經學過的比較零散的數字電路的知識能夠有機的、系統地聯系起來用于實際,培養綜合分析、設計電路的能力,進行數字鐘的設計是必要的。 2.2 數字時鐘的電路組成 數字時鐘是用數字集成電路構成,用數碼顯示的一種現代化計數器。本系統由振蕩器、分頻器、校時電路、計數器、譯碼顯示器以及電源電路組成。秒脈沖發生電路產生秒脈沖信號,不同進制的計數器、譯碼器和顯示器組成計時系統,通過校時電路實現對時、分的校準,電源電路提供穩定的+5v的電壓。 2.3 數字時鐘的工作原理 數字時鐘實際上是一個對1HZ頻率進行計數的計數電路。由于計數的起始時間不可能與標準時間一致,故需要在電路上加一個校時電路,同時標準的1HZ時間信號必須做到準確穩定。通常使用石英晶體振蕩器電路構成數字時鐘,但是出于對材料和成本的考慮,我們決定設計較簡單的中小規模集成電路組成電子鐘,采用由555定時器和RC電路構成振蕩器的方案。 圖 1系統原理框圖 (1)振蕩器電路:一般說來,振蕩器的頻率越高,計時精度越高。本設計中采用由集成定時器555與RC組成的多諧振蕩器,經過調整輸出1000Hz脈沖。 (2)分頻器電路:分頻器電路將1000HZ的方波信號經1000次分頻后得到1Hz的方波信號供秒計數器進行計數。分頻器實際上也就是計數器。 (3)時間計數器電路:時間計數電路由秒個位和秒十位計數器、分個位和分十位計數器及時個位和時十位計數器電路構成,其中秒個位和秒十位計數器、分個位和分十位計數器為60進制計數器,時個位和時十位計數器為24進制計數器。 (4)譯碼顯示電路:譯碼顯示電路將計數器輸出的8421BCD碼轉換為數碼管需要的邏輯狀態,并且為保證數碼管正常工作提供足夠的工作電流,我們采用自帶譯碼功能的數碼管。 (5)整點報時電路:一般時鐘都應具備整點報時電路功能,即在時間出現整點前數秒內,數字鐘會自動報時。其作用方式是在整點前的十秒內,出現奇數秒時報時燈發光,從而實現在最后十秒內閃爍五次,以示提醒。 (6)校時電路:由于數字鐘的初始時間不一定是標準時間,而且在數字鐘的運行過程中可能出現誤差,所以需要校時電路來對“時、分”顯示數字進行校對調整。 3.數字時鐘總設計方案和各部分設計方案 3.1 數字時鐘總設計方案

數字時鐘有振蕩器、分頻器、計數器、譯碼顯示、報時等電路組成。其中,振蕩器和分頻器組成標準秒信號發生器,直接決定計時系統的精度。由不同進制的計數器、譯碼器和顯示器組成計時系統。將標準秒信號送入采用六十進制的“秒計數器”,每秒計60s就發出一個“分脈沖”信號,該信號將作為“分計數器”的時鐘脈沖。“分計數器”也采用六十進制計數器,每累計60min,發出一個“時脈沖”信號,該信號將被送到“時計數器”。“時計數器”采用二十四或十二進制計時器,可實現對一天24h或12h的累計。譯碼顯示電路將“時”、“分”、“秒”計數器的輸出狀態通過六位七段譯碼顯示器顯示出來,可進行整點報時,計時出現誤差時,可以用校時電路校時、校分。數字時鐘的原理框圖如下圖2.1所示。 圖2.1 數字時鐘的原理框圖

3.2 各部分電路設計方案

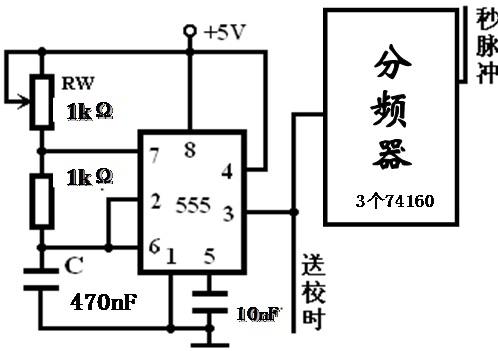

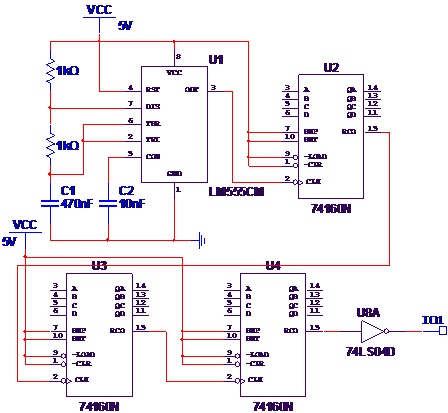

3.2.1 秒脈沖產生電路 秒脈沖產生電路的功能是產生標準秒脈沖信號,主要由振蕩器和分頻器組成。振蕩器是計數器的核心,振蕩器的穩定度和頻率的精準度決定了計時器的準確度,可由石英晶體振蕩電路或555定時器與RC組成的多諧振蕩器構成。一般來說,振蕩器的頻率越高,計時的精度就越高,但耗電量將增大,故設計時一定要根據需要設計出最佳的電路。石英晶體振蕩器具有頻率準確、振蕩穩定、溫度系數小的特點,但是如果精度要求不高的話可以采用555構成的多諧振蕩器。 秒脈沖產生電路在此例中的主要功能有兩個:一是產生標準秒脈沖信號,二是可提供整點報時所需要的頻率信號。在下面電路設計中,為了簡化電路,秒脈沖產生電路用一個1Hz的秒脈沖時鐘信號源替代。 3.2.1.1 555構成的多諧振蕩器 秒脈沖產生電路主要是由一個555定時器和三個十進制計數器74160構成。其中,555定時器與RC組成多諧振蕩器,三個計數器74160組成分頻器。其邏輯圖如圖3.2.1.1所示。

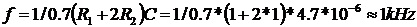

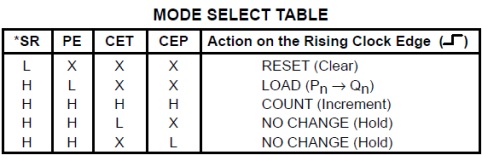

圖3.2.1.1 555構成的多諧振蕩器而成的秒脈沖產生電路邏輯圖 其中555定時器的引腳圖和功能表如圖3.2和圖3.3所示,其中選取R1=R2=1kΩ,C1=470nF,C2=10nF,從而多諧振蕩器的頻率為:

圖3.2.1.2 555定時器的引腳圖

圖3.2.1.3 555定時器的功能表

圖3.2.1.4 計數器74160的引腳圖 圖3.2.1.5 計數器74160的邏輯圖

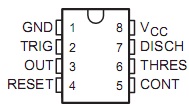

圖3.2.1.6 計數器74160的功能表 160為可預置的十進制同步計數器,共有 74160和74LS160兩種線路結構型式,其管腳圖如圖3.2.1.4所示, 160 的清除端是異步的,當清除端/MR為低電平時,不管時鐘端CP狀態如何,即可完成清除功能。 160的預置是同步的。當置入控制器/PE為低電平時,在CP上升沿作用下,輸出端Q0-Q3與數據輸入端P0-P3一致。當CP由低至高跳變或跳變前,如果計數控制端CEP、CET為高電平,則/PE 應避免由低至高電平的跳變。160 的計數是同步的。靠CP同時加在四個觸發器上而實現的。當CEP、CET 均為高電平時,在CP上升沿作用下Q0-Q3同時變化,從而消除了異步計數器中出現的計數尖峰。對于74160,只有當 CP 為高電平時,CEP、CET 才允許由高至低電平的跳變。160有超前進位功能。當計數溢出時,進位輸出端(TC)輸出一個高電平脈沖,其寬度為 Q0 的高電平部分。在不外加門電路的情況下,可級聯成N 位同步計數器。 計數器74160的引出端符號如下:

電路中多諧振蕩器輸出的是1kHz的脈沖信號,此信號作為第一級計數器的時鐘信號。計數器的四個使能端ENP、ENT、LOAD、CLR均接高電平、由于74160是十進制計數器,因此計數器每計數滿10次有一個進位信號,此信號即為第一級計數器分頻后得到的100Hz的脈沖信號,將這個信號接在下一級計數器的時鐘信號端CLK則可實現繼續分頻,經過兩個74160逐級分頻后依次得到10Hz和1Hz的脈沖信號。其電路仿真圖如圖3.2.1.7所示,用一個四通道的示波器可以清楚看到四個脈沖信號的波形如圖3.2.1.8所示。

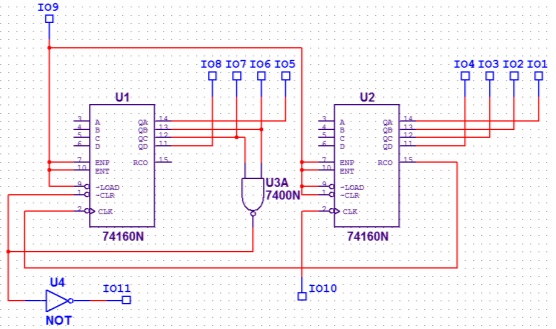

圖3.2.1.7 秒脈沖產生電路仿真圖

圖3.2.1.8 千分頻秒脈沖信號仿真波形 3.2.2計數器電路 根據數字時鐘的原理框圖2.1可知,整個計數器電路由秒計數器、分計數器和時計數器串接而成。秒脈沖信號經過6級計數器,分別得到秒個位、秒十位、分個位、分十位以及時個位、時十位的計時。顯示6位的“時”、“分”、“秒”需要6片中規模的計數器。其中,秒計數器和分計數器都是六十進制,時計數器為二十四/十二進制,都選用74160來實現。實現的方法采用反饋清零法。 3.2.2.1六十進制計數電路 秒計數器和分計數器各由一個十進制計數器(個位)和一個六進制計數器(十位)串接組成,形成兩個六十進制計數器,其中個位計數器接成十進制形式。十位計數器選擇QB與QC端做反饋端,經與非門輸出至控制清零端CLR,接成六進制計數形式(計數至0110時清零)。個位與十位計數器之間采用同步級聯復位方式,將個位計數器的進位輸出端RCO接至十位計數器的時鐘信號輸入端CLK,完成個位對十位計數器的進位控制。將十位計時器的反饋清零信號經非門輸出,作為六十進制的進位輸出脈沖信號,即當計數器計數至60時,反饋清零的低電平信號輸入CLR端,同時經非門變為高電平,在同步級聯方式下,控制高位計數器的計數。 創建如圖3.2.2.1所示的電路,IO1~IO4是個位數碼管的顯示輸出端,IO5~IO8是十位數碼管的顯示輸出端,IO9接電源,給兩個芯片的使能端提供高電平,IO10在此電路作為秒計數電路時接秒信號產生電路,作為分計數電路時接秒計數電路提供過來的進位信號(即接至秒計數器的CLR端)。IO11作為低位計數器的進位輸出,與高位計數器的時鐘信號端相連。

圖3.2.2.1六十進制計數電路 3.2.2.2 二十四/十二進制計數電路 創建如圖3.2.2.2所示的電路,IO1~IO4是個位數碼管的顯示輸出端,IO5~IO8是十位數碼管的顯示輸出端,IO9接電源,給兩個芯片的使能端提供高電平,IO10接分計數電路提供過來的進位信號(即接至分計數器的CLR端)。IO11連接了兩個計數器的清零端,因此可以通過雙向開關接IO12和IO13以實現對與非門的選擇,從而完成進制的轉換。 分計數器需要的是一個二十四/十二進制轉換的遞增計數電路。個位和十位計數器均連接成十進制計數形式,采用同步級聯復位方式。將個位計數器進位輸出端RCO接至十位計數器的時鐘信號輸入端CLK,完成個位對十位計數器的進位控制。若選擇二十四進制,十位計數器的輸出端QB和個位計數器的輸出端QC通過與非門控制兩片計數器的清零端CLR,當計數器的輸出狀態為00100100時,立即反饋清零,從而實現二十四進制遞增計數。若選擇十二進制,十位計數器的輸出端QA和個位計數器的輸出端QB通過與非門控制兩片計數器的清零端CLR,當計數器的輸出狀態為00010010時,立即反饋清零,從而實現十二進制遞增計數。兩個與非門通過一個雙向開關接至兩片計數器的清零端CLR,單擊開關就可以選擇與非門的輸出,實現二十四進制或十二進制遞增計數的轉換。

圖3.2.2.2二十四/十二進制計數電路

3.2.3譯碼顯示電路 采用共陰極七段數碼管將譯碼顯示電路是將計數器輸出的8421 BCD碼譯成數碼管顯示所需要的高低電平。譯碼電路就應選接與它配套的共陰極七段數碼驅動器。譯碼顯示電路采用CD45117段譯碼驅動器。譯碼器A、B、C、D與十進制計數器的四個輸出端相連接,a、b、c、d、e、f、g即為驅動七段數碼顯示器的信號。根據A、B、C、D所得的計數信號,數碼管顯示的相對應的字型。

3.2.3.1 七段數碼管

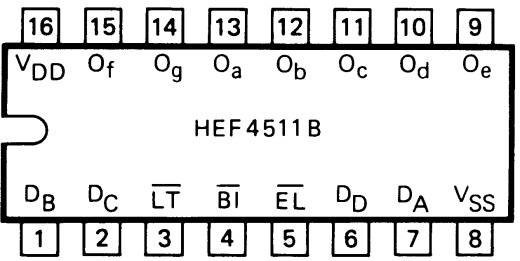

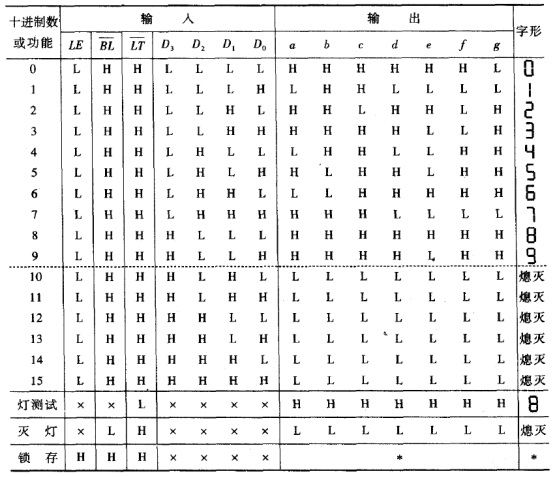

圖3.2.3.1 七段數碼管的引腳圖 3.2.3.2 CD4511譯碼器 為了使數碼管能顯示十進制數。必須將十進制數代碼經譯碼器譯出,然后經驅動器點亮對應的段。所以,譯碼器的功能就是,對應于某一組數碼輸入,相應的幾個輸出端有有效信號輸出。 常用的集成七段顯示譯碼器有兩類,一類譯碼器輸出高電平有效信號,用來驅動共陰極顯示器,另一類輸出低電平有效信號,以驅動共陽極顯示器。 CD4511七段顯示譯碼器的邏輯符號如圖3.2.3.2所示,功能表如圖3.2.3.3所示。當輸入8421BCD碼時,輸出高電平有效。用以驅動共陰極顯示器。當輸入為1010~1111六個狀態時,輸出全為低電平,顯示器無顯示。

圖3.2.3.2 CD4511邏輯符號(引腳圖) 該集成顯示譯碼器設有三個輔助控制端LE、 、 、 ,以增強器件的功能,現分別簡述如下: ,以增強器件的功能,現分別簡述如下: ⑴燈測試輸入端 當 =0時,無論其他輸入端是什么狀態,所有各段輸出a~g均為1,顯示字形 =0時,無論其他輸入端是什么狀態,所有各段輸出a~g均為1,顯示字形 。該輸入端常用于檢查譯碼器本身及顯示器各段的好壞。 。該輸入端常用于檢查譯碼器本身及顯示器各段的好壞。 ⑵滅燈輸入 當 =0,并且 =0,并且 =1時,無論其他輸入端是什么電平,所有各段輸出a~g均為0,所有字形熄滅。該輸入端用于將不必要顯示的零熄滅。 =1時,無論其他輸入端是什么電平,所有各段輸出a~g均為0,所有字形熄滅。該輸入端用于將不必要顯示的零熄滅。 ⑶鎖存使能輸入LE 在 = = =1的條件下,當LE=0時,鎖存器不工作,譯碼器的輸出隨輸入碼的變化而變化;當LE由0跳變1時,輸入碼被鎖存,輸出只取決于鎖存器的內容,不再隨輸入的變化而變化。 =1的條件下,當LE=0時,鎖存器不工作,譯碼器的輸出隨輸入碼的變化而變化;當LE由0跳變1時,輸入碼被鎖存,輸出只取決于鎖存器的內容,不再隨輸入的變化而變化。

圖3.2.3.2 CD4511的功能表

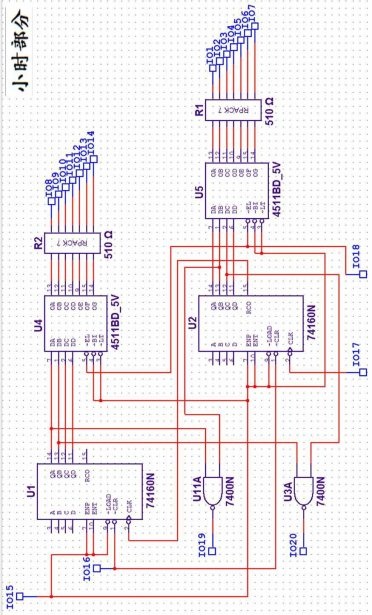

圖3.2.3.4 顯示器顯示字形 3.2.3.3 小時譯碼顯示子電路 只需在 = = =1并且LE=0時,譯碼器的輸出隨輸入碼的變化而變化,所以只要把4511譯碼器的數據輸入端與74160計數器的輸出端相連即可。而分鐘和秒譯碼顯示電路也是如此,如圖3.2.3.5所示。 =1并且LE=0時,譯碼器的輸出隨輸入碼的變化而變化,所以只要把4511譯碼器的數據輸入端與74160計數器的輸出端相連即可。而分鐘和秒譯碼顯示電路也是如此,如圖3.2.3.5所示。

圖3.2.3.5小時譯碼顯示子電路(六十進制計數) 3.2.3.4分鐘/秒譯碼顯示子電路

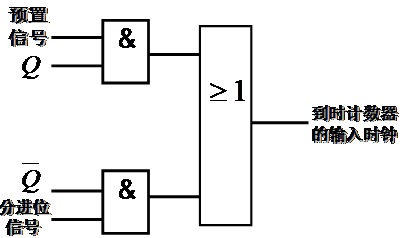

圖3.2.3.6 分鐘/秒譯碼顯示子電路(十二、二十四進制計數) 3.2.4校時、校分電路 校對時間一般在選定的標準時間到來之前進行,可分為4個步驟:首先把時計數器置到所需的數字;然后再將分計數器置到所需的數字;與此同時或之后應將秒計數器清零,時鐘暫停計數,處于等待啟動階段;當選定的標準時刻到達的瞬間,按啟動按鈕,電路則從所預置時間開始計數。由此可知,校時,校分電路應具有預置小時、預置分、等待啟動、計時4個階段。在設計電路時既要方便可靠地實現校時校分的功能,又不能影響時鐘的正常計時,通常采用邏輯門切換。當Q=1時,輸入的預置信號可以傳到時計數器的CLK端,進行校時工作,而分進位信號被封鎖。例如,校時電路原理示意圖如圖3.2.4.1所示。當Q=0時,分進位信號可以傳到時計數器的CLK端,進行計時工作,而輸入的預置信號分進位信號被封鎖。校分電路也仿照此進行。

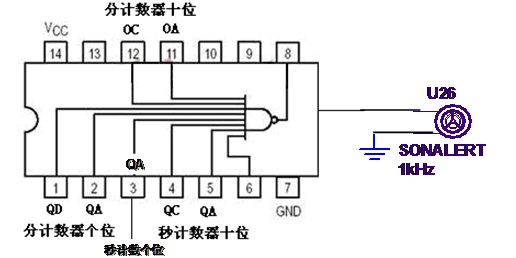

圖3.2.4.1 校時電路原理框圖 當然上述方法比較精確,也比較復雜,在精度要求不高時,也可以采用另一種方法。只需使用兩個雙向選擇開關將秒脈沖直接引入時計數器的分計數器即可實現功能。此時,低位計數器的進位信號輸出端需通過雙向選擇開關的其中一選擇端接至高位計數器的時鐘信號端,開關的另一選擇端接秒脈沖信號。當日常顯示時間時,開關撥向低位計數器的進位信號輸出端;調時調分時撥向秒脈沖信號,這樣可使計數器自動跳至所需要的時間。(具體見總電路圖) 3.2.5整點報時電路 當時間到達整點前10秒開始,蜂鳴器1秒響1秒停地響5次。即當時間達到××時59分50秒時蜂鳴器開始響第一次,并持續一秒鐘,然后停鳴一秒,這樣響五次。利用與非門的相與功能,而已把分十位的OC 、OA ,分個位的QD、QA,秒十位的QC、QA 和秒個位的QA相“與非”作為控制信號控制與非門的開斷,從而控制蜂鳴器的響和停。

圖3.2.5.1 整點報時電路

3.3 總電路設計圖

4.數字時鐘電路仿真

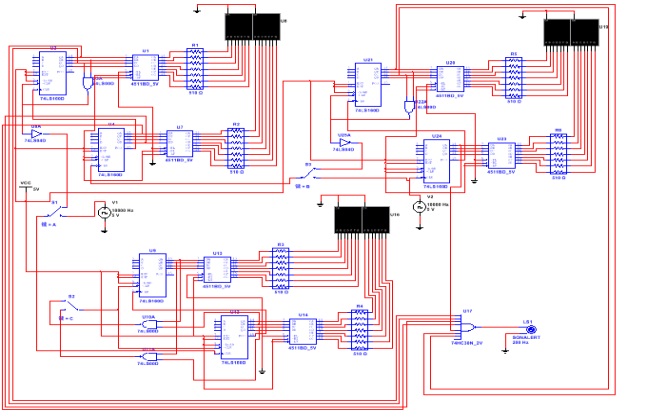

4.1開始狀態

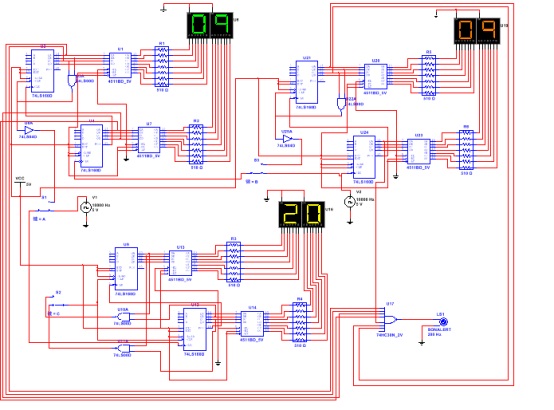

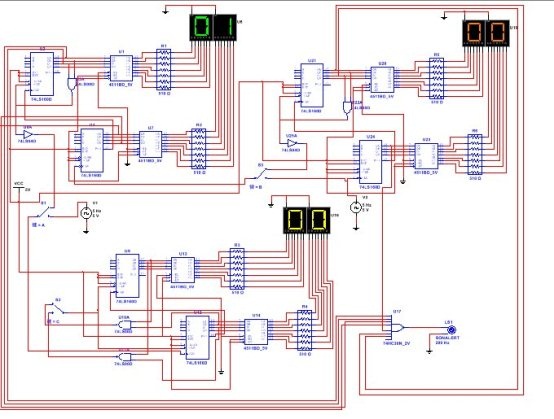

圖4.1.1 開始狀態

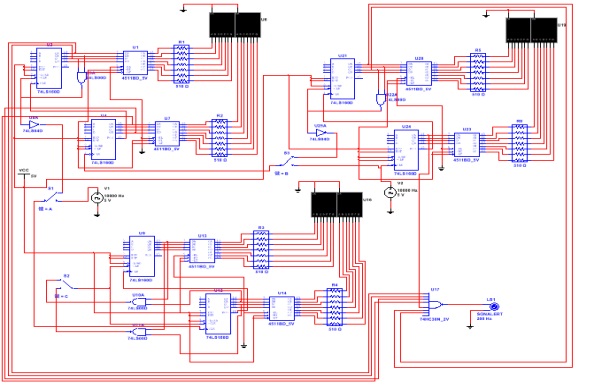

4.2校時、校分功能

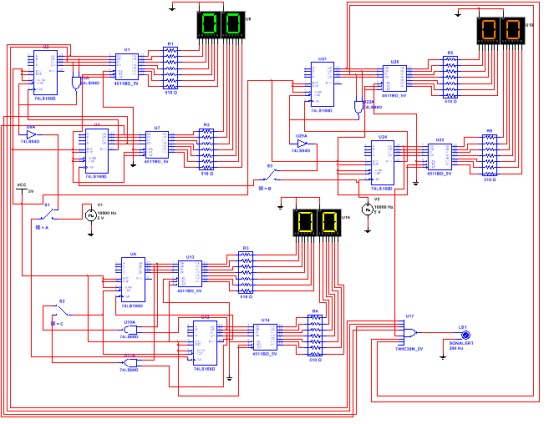

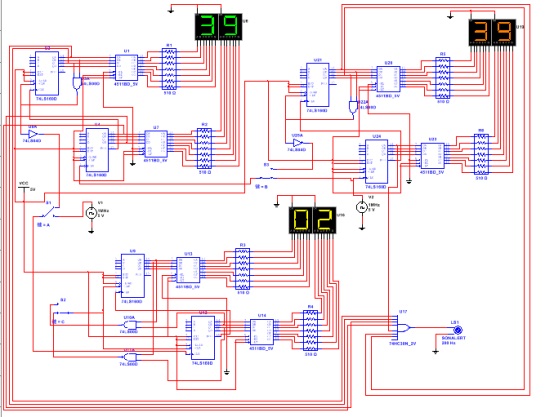

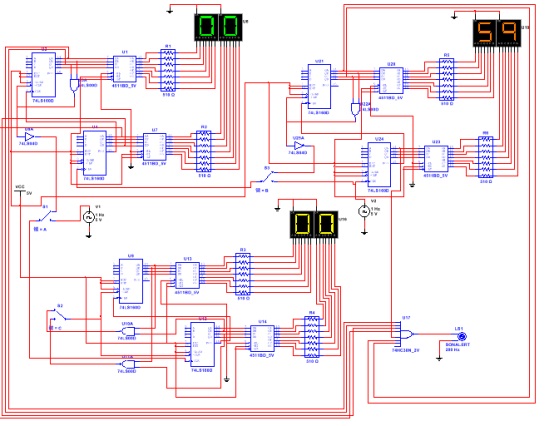

圖4.2.1校時、校分功能 4.3十二進制與二十四進制轉換功能

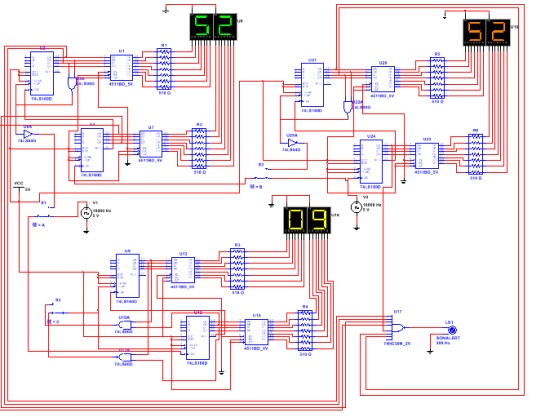

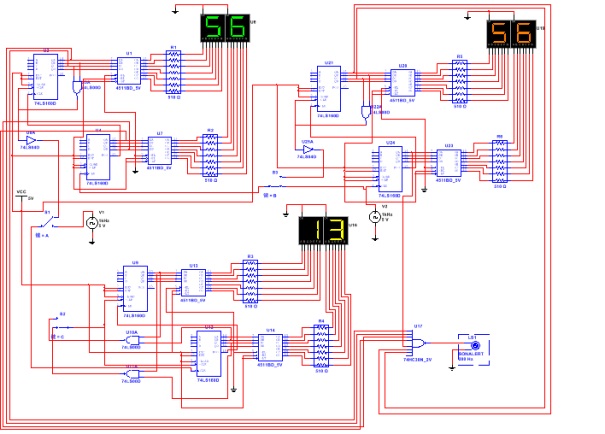

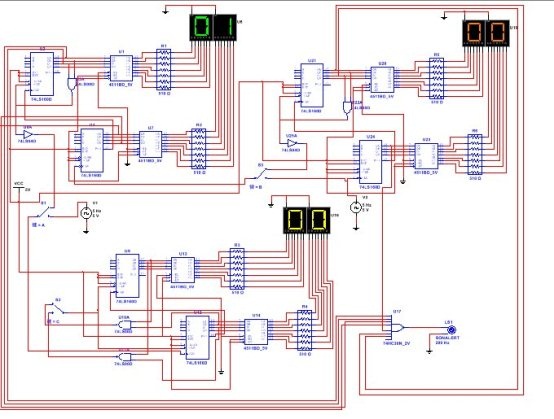

圖4.3.1十二進制與二十四進制轉換功能 4.4滿60秒向分鐘進位狀態

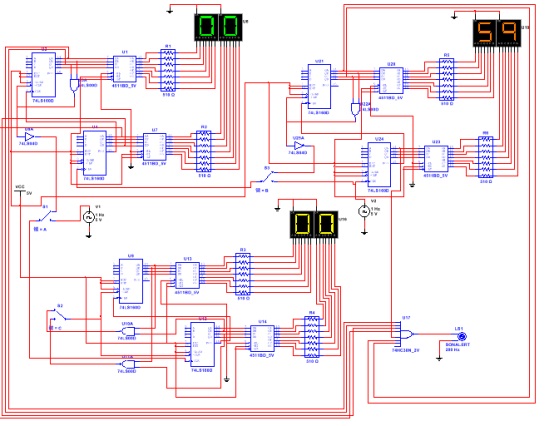

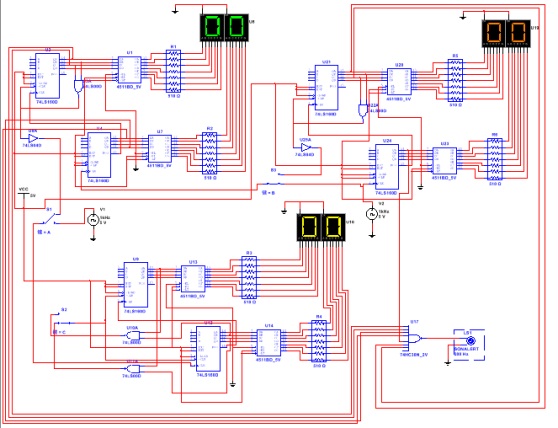

圖4.4.1滿60秒向分鐘進位狀態 4.5滿60分向小時進位狀態

圖4.5.1 滿60分向小時進位狀態 4.6 23:59:59向00:00:00進位狀態

由于我初學以上內容肯定存在很多錯誤,歡迎大家批評指正,一起學習 提高技術(為了方便保存, 把網頁上的內容打包成了word,僅供參考 切勿照搬):

數電51hei設計 數字時鐘.doc

(2.03 MB, 下載次數: 45)

數電51hei設計 數字時鐘.doc

(2.03 MB, 下載次數: 45)

2021-6-22 21:54 上傳

點擊文件名下載附件

下載積分: 黑幣 -5

|