包含硬件PCB硬件設計和FPGA的Verilog代碼的編寫,下圖為主要功能框圖。FPGA作為處理單元,實現了包括電流和電壓的采集、千兆以太網通訊、SD卡本地存儲和串口通訊等。已經打PCB板實際驗證和Verilog代碼在硬件上的實際測試,測試部分包含:千兆網通訊收發測試、AD采集的數據驗證、SD卡存儲驗證、RTC實時時鐘讀取和RTC的RAM突發讀取等。

PCB設計采用的是AD軟件,Verilog程序通過quartus II軟件編寫。現由硬件和軟件兩個方面簡單介紹。

?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70) ?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70)

一、硬件設計

下圖分別為硬件的正面和反面,純手工焊。綜合考慮千兆以太網中的高速數據線的差分阻抗100MΩ、數字電源和模擬電源的劃分等,PCB主要采用四層板的設計方案。頂層和底層為信號走線層;第二層為完整的地層,分為數字地(DGND)和模擬地(AGND),為頂層的信號層和電位電流模擬量的采集提供參考;第三層為電源層,本層提供較為完整的3.3V電源平面和模擬地平面,還有1.2V和2.5V的電源平面。

其中硬件設計中最要小心的是千兆以太網的設計和電流采集部分。千兆網部分采用的是ETL8211EG芯片,支持千兆以太網,要實現千兆網絡,要保證查分阻抗100Ω,就需要考慮蛇形走線和線寬線距、參考層等因素。電流采集部分要考慮模擬地的劃分和電流的放大倍數、高精度電阻等,這里我選的是INA240A系列,包含20、50、100、200四種增益可以選擇。數模轉換是8通道,每通道16位,支持并行的200SPS的AD7606芯片。SD卡就是最常見的Micro SD Card,買的閃迪的16G的卡。RTC是常見的DS1302。考慮版面問題,數碼管只留了一個。硬件下載AD源文件下載鏈接:https://download.csdn.net/download/qq_39521541/15110220

?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70) ?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70)

?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70) ?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70)

?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70) ?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70)

AD中的三維圖如下:

?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70) ?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70)

?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70) ?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70)

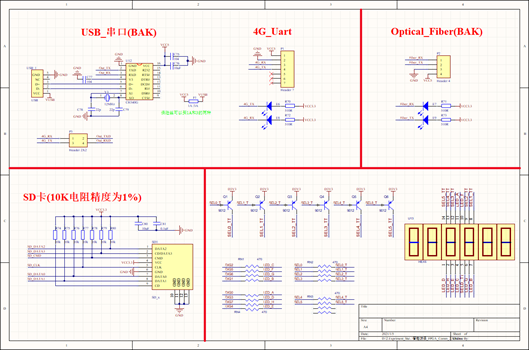

各模塊的原理圖如下,這是初版 的原理圖,實際的硬件在此基礎上進行了修改,但是變化不大,就不再截圖了。

?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70) ?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70)

?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70) ?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70)

?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70) ?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70)

?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70)[存儲通訊和顯示電路]( ?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70)[存儲通訊和顯示電路]( ?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70) ?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70) ?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70)

二、軟件程序編寫

在以上硬件的基礎上編寫了程序,總程序5000余行。實現了AD7606電壓和電流數據的采集和RTC的時間和內部RAM突發讀寫,然后并行的存儲和通過千兆以太網與串口發送到電腦上。

程序的頂層模塊設計如下圖:

?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70) ?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70)

通過電腦上的網絡助手同時采集到的串口數據、千兆以太網數據和用Winhex查看的SD卡內存儲的數據如下圖,數據完全一致。串口數據為什么也用網絡助手顯示呢,因為我板子上的串口上可以插上一個網絡模塊,這樣串口數據也可以通過無線發送到電腦了,當然硬件上也有有線的串口端子,也進行了驗證,不再截圖贅述。

?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70) ?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70)

程序主要難點在于邏輯與時序的處理,程序中進行了一些時序的操作。為了方便我理清思路也進行了主要的時序圖的繪制,如下圖所示,畫時序圖的軟件可以在這里下載https://download.csdn.net/download/qq_39521541/14951291,破解版很好用。 ?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70) ?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70)

程序的模塊結構如下圖所示,其中4G其實就是串口,為了進行跨時鐘域和SD的閃存,用了雙口FIFO、雙口RAM、單口RAM、ROM等IP核。

?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70) ?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70)

接下來是編譯后的資源占用情況和編譯信息,從圖中可以看出基本不存在警告,其實現存的三個警告,完全不影響結果,而且知道警告存在的原因即可。

?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70) ?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzM5NTIxNTQx,size_16,color_FFFFFF,t_70)

時序約束部分截圖如下,時鐘主要約束了50M的系統時鐘、25M的SD卡時鐘和125M的千兆網時鐘。

) )

最后的最后附上總的程序源碼:https://download.csdn.net/download/qq_39521541/15110143

感謝大家的批評指正

|