|

設計一個30s倒計時器。滿足如下要求: (1)具有30s計時功能; (2)設置外部操作開關,控制計數器的直接清零、啟動和停止功能; (3)在直接清零時,要求數碼顯示器滅燈; (4)計時器為30s遞減計時,計時間隔為1s; (5)計時器遞減計時到零時,數碼顯示器不能滅燈,LED發光。

20201102154950.png (188.19 KB, 下載次數: 410)

下載附件

2020-11-2 15:52 上傳

2 總體設計方案 圖2-1系統框圖 本設計的核心是一個30s計時器,根據要求要將計時進行實時顯示,同時達到設計任務中的清零、重置、報警等各項要求。初時確定課題后,是沒有什么頭緒的,想法就是通過元器件以秒為單位發出脈沖,并計次顯示,如此大致思路。結合目前學習中的知識,定時器、計數器、7段譯碼器以及7段顯示器首先成為選擇,翻閱了數電書后,簡單繪圖大致思路即定型,方案初步可行。細節性的東西再結合以往知識來完成,設計課題大致不會有問題,借此機會加深對各個元器件的了解和運動,來完成課題設計。 電路系統應包括幾個部分,分別為:脈沖發生器、計數器、譯碼器、顯示電路、控制系統以及報警系統幾個主要部分來完成。其中計數顯示是電路的核心部分。計數器完成30s計時功能,而控制電路具有直接控制計數器的啟動計數、暫停、連續計數、譯碼顯示電路的顯示和滅燈功能。為了滿足系統的設計要求,在設計控制電路時,應正確處理各個信號之間的時序關系。在操作直接清零開關時,要求計數器清零,數碼顯示器顯示零。當啟動開關閉合時,控制電路應封鎖時鐘信號CP,同時計數器完成置數功能,譯碼顯示電路顯示30s字樣;當啟動開關斷開時,計數器開始計數;當暫停、連續開關撥在暫停位置上時,計數器的停止計數,處于保持狀態;當暫停、連續開關撥在連續時,計數器繼續遞減計數。 其設計思路及各電路單元大致如下: 由基本電源供電,通過對電源的開關選擇來達到整個計數工具的開啟與關閉。脈沖發生器以秒為單位發出脈沖信號,并配以開關控制與電源的接觸達到脈沖波的暫停與繼續。通過計數器進行脈沖計數,并根據計數,自動鳴叫,閃光。通過控制電路,對計數器進行清零和置數控制。計數器的數字信號,通過譯碼器以及最后的數字顯示器,達到計數顯示的最終設計目的。 3 單元電路的設計 3.1脈沖發生器555定時器是一種中規模集成電路,利用它可以方便的構成施密特觸發器、單穩態觸發器和多諧振蕩器等。555定時器具有功能強、使用靈活、應用范圍廣等優點。目前在儀器、儀表和自動化控制中得到了廣泛的應用。 555定時器有TTL/COMS型兩類,它們的邏輯功能和外部引腳排列完全相同。它是雙列直插式組件,它由分壓器、電壓比較器、基本RS觸發器、放電管和輸出緩沖級幾個基本單位組成。主要是通過外接電阻R和電容C構成充放電電路,并由兩個比較器來檢測電容器上的電壓,以確定輸出電平的高低和放電開關管的通斷。這就很方便地構成從微秒到數十分鐘的延時電路、以及多諧振蕩器、單穩態觸發器、施密特觸發器等脈沖波形產生和整形電路。

表3-1 555定時器功能表

555為8腳時基集成電路,各腳主要功能: 1 接地GND 2 低觸發端TR 3 輸出端OUT 4 復位端R 5 控制電壓CV 6 高觸發端TH 7 放電端DC 8 電源電壓VCC 用555定時器構成多諧振蕩器電路如圖3-2,電路沒有穩態,只有兩個暫穩態,也不需要外加觸發信號,利用電源VCC通過R1和R2向電容器C充電使Uc逐漸升高,升到2VCC/3時,U0跳變到低電平,放電端D導通,這時,電容器C通過電阻R2和D端放電,使Uc下降,降到VCC/3時,U0跳變到高電平,D端截止,電源VCC又通過R1和R2向電容C充電。如此循環,振蕩不停,電容器C在VCC/3和2VCC/3之間充電和放電,輸出連續的矩形脈沖。 輸出信號U0的脈寬tW1、tW2、周期T的計算公式如下: tW1=0.7(R1+R2)C tW2=0.7R2C T=0.7(R1+2R2)C 圖3-2 555多諧振蕩器 圖3-3 555工作波形 本次設計的核心之一便是555多頻振蕩器,設計選用555多頻振蕩器來做為計時器并以1s為周期發出的脈沖。其周期計算為: 0.7(R1+2R2)C=T=1s=0.7(4.4kΩ+2*5kΩ)100uf 得出多頻振蕩器各輔助器件參數R1=5.1kΩ,R2=5.1kΩ,C=100uf,連接電路,多頻振蕩器即脈沖發生器完成。 3.2 計數器計數器是一個用以實現計數器功能的時序邏輯部件,它不僅可以用來對脈沖進行計數,還常用作數字系統的定時、分頻和執行數字運算以及其他特定的邏輯功能。 74ls192為可預置的十進制同步加/減計數器(雙時鐘),其清除端是異步的。當清除端(MR)為高電平時,不管時鐘端(CPD、CPU)狀態如何,即可完成清除功能;預置是異步的,當置入控制端(PL)為低電平時,不管時鐘CP的狀態如何,輸出端(Q0-Q3)即可預置成與輸入端(P0-P3)相一致的狀態,計數是同步的,靠CPD.CPU同時加在4個觸發器上而實現。在CPD,CPU上升沿作用下Q0-Q3同時變化,從而消除了同步計時器中出現的技術尖峰。當進行加計數或減計數時可分別應用CPD或CPU。此時另一個時鐘應為高電平。當計數上溢出時,進位輸出端(TCU)輸出一個低電平脈沖,其寬度為CPU低電平部分的低電平脈沖,當計數下溢出時,錯位輸出端(TCD)輸出一個低電平脈沖,其寬度為CPD低電平部分的低電平脈沖。當把TCD和TCU分別連接后一級的CPD,CPU,即可進行級聯。 74LS192是雙時鐘方式的十進制可逆計數器,如圖3-7。 CPU為加計時器時鐘輸入端,CPD為減計數器時鐘輸入端。 LD為預置輸入控制端,異步預置。 CR為復位輸入端,高電平有效,異步清除。 C0為進位輸出端,1001狀態后負脈沖輸出。 B0為借位輸出端,0000狀態后負脈沖輸出。 引出端符號 TCD 錯位輸出端(低電平有效) TCU 進位輸出端(低電平有效) CPD 減計數時鐘輸入端(上升沿有效) CPU 加計數時鐘輸入端(上升沿有效) MR 異步清除端 P0-P3 并行數據輸入端 PL 異步并行置入控制端(低電平有效) Q0-Q3 輸出端 圖3-4 三進計數器 圖3-5 74LS192結構圖 因其本質即十進制計數器,清零置數減法等功能完善符合設計要求,故選用兩片74LS192芯片對脈沖信號進行計數。兩片芯片分別計數十位和個位,置數端,個位置數為0,十位置數為3,即30S倒計時開始。DN端接入555多頻振蕩器的脈沖信號,UP端接高電平,TCD端空接來達到減計數的效果。Q端信號輸出給譯碼器進行譯碼顯示。TCD端借位信號接入十位片的DN端進行十位的減法計數,兩片互相配合完成兩位數30S的計數。兩片芯片PL端同接入控制電路置數開關進行控制,兩個MR端同接入控制電路清零開關進行清零控制。

表3-6 74LS192功能表

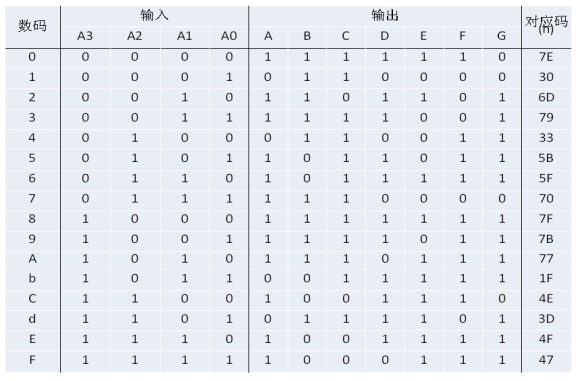

圖3-7十進計數器 3.3譯碼顯示電路用數碼管來顯示數字,這種數碼管的每個線段都是一個發光二極管,因此也稱LED數碼管或LED七段顯示器。因為計算機輸出的是BCD碼,要想在數碼管上顯示十進制數,就必須把BCD碼轉換成7段字形數碼管所要求的代碼。我么們能夠將計算機輸出的BCD碼轉換成7段字型代碼,并使數碼管顯示出十進制數的電路稱為“七段字型譯碼器”,其功能表如表3-10。因此在本次的設計中我們采用了常用的74ls48。

表3-8數碼管功能表

如前所述,分段式數碼管是利用不同發光段組合的方式顯示不同數碼的。因此,為了使數碼管能將數碼所代表的數顯示出來,必須將數碼經譯碼器譯出,然后經驅動器點亮對應的段。例如,對于8421碼的0011狀態,對應的十進制數為3,則譯碼驅動器應使a、b、c、d、g各段點亮。即對應于某一組數碼,譯碼器應有確定的幾個輸出端有信號輸出,這是分段式數碼管電路的主要特點。 74LS48為4線-七段譯碼器/驅動器(BCD輸入。有上拉電阻),其輸出端為高電平有效,可驅動燈緩沖器或共陰極VLED。當要求輸出0-15時,消隱輸入(BI)應為高電平或開路,對于輸出為0時還要求脈沖消隱輸入(RBI)為高電平或者開路。當BI為低電平時。不管其他輸入端狀態如何,Ya-Yg均為低電平。當RBI和地址端均為低電平,并且燈測試輸入端(LT)為高電平時,Ya-Yg為低電平,脈沖消隱輸出(RBO)也變為低電平。當BI為高電平或開路時,LT為低電平可使Ya-Yg均為高電平。48與248的引出端排列、功能和電特性均相同,差別僅在顯示6和9,248所顯示的6和9比48多出上杠和下杠。 引出端符號: A-D 譯碼地址輸入端 BI/RBO 消隱輸入(低電平有效)/脈沖消隱輸出(低電平有效) LT 燈測試輸入端(低電平有效) RBI 脈沖消隱輸入端(低電平有效)a-g段輸出 將兩個芯片的使能段同接入高電平使兩組譯碼顯示能夠正常運行工作,實時傳遞計數器的計數信號,達到30s可視計數的效果。 3.4 控制及警告電路當計數器74LS192的清零端MR=1有效時,即可實現對電路清零;而當清零端無效,置數端PL=0有效時,即可實現對電路的置數;通過開關對555脈沖發生器輸入端電源的進行控制,即可實現對整個電路進行暫停計時,為減小開關按鍵產生的機械抖動對計時電路的影響,應接-RS鎖存器;當十位計數器74LS192的借位輸出端有效時,即可實現報警。 具體實施如下: 啟動/暫停:通過對電源的控制,進行電路總啟動停止的控制。 暫停/繼續:通過對555多頻振蕩器的電源控制,達到對脈沖的暫停/繼續控制。 清零:通過按鈕開關將兩片計數器MR清零端接入高電平達到清零效果 置數:通過單刀雙擲開關,將兩片計數器的PL置數端接地達到低電平清零效果。報即鳴叫,閃光,歸零。當TCD輸出借位信號,即表示計數完畢,為使示數停留00并發出警報,接入一JK鎖存器,鎖存TCD借位信號并將jK端高電平信號傳達至MR端達到清零效果以及LED/喇叭端達到閃光鳴叫的報警效果,并通過JK鎖存器的翻轉效果,使得Q和非兩輸入端電平的恢復為下一次計數報警做準備,通過按鈕開關的清零效果也可以達到翻轉jk鎖存器為下次警報做準備的效果. 圖3-9 報警電路 如圖3-11。啟動電路后,當電路中的數碼管的示數顯示為00時,D1開始閃爍并且報警器發出滴滴的報警聲。 圖3-10暫停電路 如圖3-12。啟動電路后,電路在運行過程中時,數碼管是示數一直在減小,當你將SW1開關打開時,數碼管的示數將停止變化。

4 系統仿真調試

圖4-1 啟動電路 如圖4-1,當SW2關閉后數碼管顯示為30并穩定不動,當打開SW2后開始進行倒計時。 圖4-2電路運行中 如圖4-2,電路在運行的過程中,當打開SW1時,數碼管的數字停止不動,起到暫停作用,當關閉SW1后,電路繼續進行倒計時。

圖4-3電路運行結束 如圖4-3,當電路運行的數碼管顯示00時,即表示計數完畢,為使示數停留00并發出警報,接入JK鎖存器,鎖存TCD借位信號并將jK端高電平信號傳達至MR端達到清零效果以及LED/喇叭端達到閃光鳴叫的報警效果,并通過JK鎖存器的翻轉效果,使得Q和非兩輸入端電平的恢復為下一次計數報警做準備,通過按鈕開關的清零效果也可以達到翻轉jk鎖存器為下次警報做準備的效果.

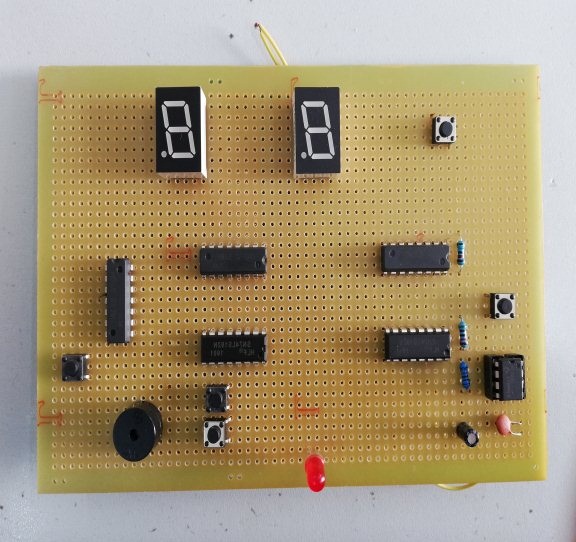

圖4-4 實物圖 5 總結 通過自己選題,找材料,分析,設計等,也掌握了一些軟件的操作方法,這為以后的學習做了鋪墊。整個設計實現了從單一的理論學習到解決實際問題的轉變。通過本次的設計,我最大的收獲是提高了自己的動手能力,培養了我的尋求解決問題的能力和團隊精神也增強了我其他方面的能力。在設計中,我充分應用我們所學的知識,例如:集成電路74ls系列、定時器555等元器件的使用。這次事件使我受益匪淺,在摸索該如何設計電路使之實現所需功能的過程中,特別有趣,培養了我的設計思維增強了我的實際操作能力。增強了我的實際操作能力。這次設計所用的工具是Proteus,仿真比較方便,使設計的質量得到了保證。

以上的Word格式文檔51黑下載地址:

30S倒計時器的設計.doc

(4.65 MB, 下載次數: 64)

30S倒計時器的設計.doc

(4.65 MB, 下載次數: 64)

2020-11-2 15:51 上傳

點擊文件名下載附件

下載積分: 黑幣 -5

|