設計簡易鐘表邏輯電路,功能內容包括(基本計時、顯示功能、具有分、秒的數字顯示),能實現停表和設置時間功能。

baa8b6a41705cde4df9839c24b70f41.png (160.34 KB, 下載次數: 142)

下載附件

設計圖紙

2020-7-20 23:00 上傳

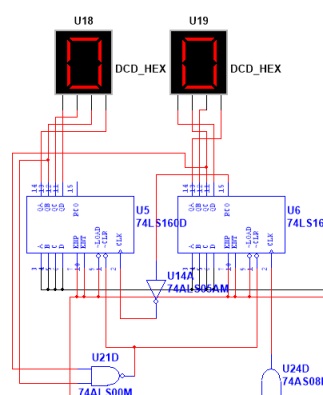

設計電路3.1.1元器件型號計數器74LS160D、與非門74ALS00M、與門74AS08M、非門 74ALS05AM、數碼管DCD_HEX。

3.1.2 秒鐘電路

圖3-1 秒鐘電路

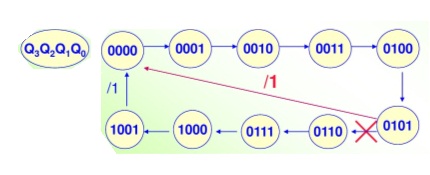

秒鐘電路搭建如圖3-1,由兩片74LS160構成60進制計數器,十位由十進制計數器加與非門構成六進制計數器,狀態圖如圖3-2,中間采用串行級聯連接(由十位計數器的ENP和ENT端連接到個位計數器的RCO進位端),來構成60進制計數器。

圖3-2 74LS160十進制構成六進制狀態圖

3.1.3分鐘電路

3.1.3分鐘電路

圖3-3 分鐘電路

分鐘電路如圖3-3與秒鐘電路搭建并無太大區別,這里的秒到分進位時鐘信號,直接選取的預置數置一的低電平信號。

3.1.4 小時電路

3.1.4 小時電路

圖3-4 小時電路

3.1.5 特殊功能鍵電路

圖3-5 特殊功能鍵電路

時鐘調節和分鐘調節功能鍵電路如圖3-5,由VCC提供高電平信號,當按下按鈕時,經過非門,刷新與門的電平信號,從而為CLK提供時鐘信號,實現調節時鐘的功能。

圖3-6 暫停功能鍵

暫停時鐘功能,由開關A實現如圖3-6,當打開開關時,時鐘信號關閉,秒鐘的時鐘信號源關斷,暫停計時。

3.1.6 簡易鐘表邏輯電路

圖3-7 簡易鐘表邏輯電路

3.2相關計算74LS160進制計算方法有,當使用同步預置數法連接時,進制數為

,當使用異步清零時,進制數為

。

60進制計算,本設計60進制計數器構成由兩片74LS160通過同步預置數的方法連接而成,同步預置數連接方法進制計算公式為

,因此Q為0101,為5。D為0000,為0。并采用串行級聯方法得60進制計數器。

24進制計數,本設計24進制計數器構成由兩片74LS160通過異步清零的方法連接而成,異步清零連接方法的進制計算公式為

,因此十位的Q為0010,為2。個位Q為0100,為4。D為0000,為0。構成24進制計數器。

四、測試方案

4.1仿真測試的步驟

仿真測試步驟:

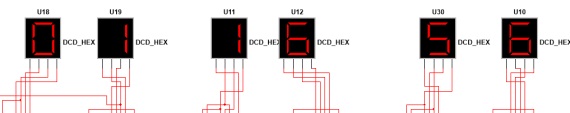

(1)秒計時進行仿真測試

先將時鐘信號源頻率加快,打開仿真開關,觀看秒數碼管時鐘信號是否給入,觀看個位進位信號是否給入十位,74LS160計數器是否構成60進制計數器。

先將分計時的CLK接入時鐘信號源,同樣加快頻率,打開仿真,同樣觀看個位進位信號是否給入十位,74LS160計數器是否構成60進制計數器。斷開仿真,將秒進位的信號接入分計時的CLK端(這里進位捕捉信號為L端的預置數低電平信號),啟動仿真,是否成功由秒進位到分。

同前面秒、分測試方法相同

打開仿真,按動時、分調節按鈕,是否有脈沖信號給入對應的計時數碼管。打開暫停開關,計時是否暫停。

4.2實驗數據

4.2實驗結果分析和結論

4.2實驗結果分析和結論本設計成功的完成了簡易鐘表邏輯電路的設計,實現了24小時制計時,以及小時和分鐘的調節機制。采用了普通方波信號發生器,頻率設置為1HZ,來提供1秒的時鐘信號。通過6片74LS160分別構成了一片24進制和兩片60進制計數器,實現了時、分、秒的計時功能,并通過七段數碼管顯示,相應的數字。

進行仿真實驗成功不代表著現實實驗成功,或許仿真中有恰當的地方,到了實驗室就不一定恰當。

五、安裝、調試中的問題、解決方法及效果5.1仿真調試電路過程中的遇到的問題

仿真問題1

秒鐘進位信號給上去,是在8變9時進位,而不是9變為0時進位。

解決方法:

對74LS160的知識內容有些淡忘,在網上找到了74LS160構成進制的正確連接方法,當M>N時,進制連接采用串行連接或是并行連接方法。

仿真問題2

采用74LS160構成60進制時,采用的異步清零的連接方法,導致60秒進位信號給不到分,以為清零的信號太短暫,而沒有捕捉到這個信號。

解決方法:

加入信號鎖存器,在Multisim中使用倆個與非門構成RS信號鎖存器,講清零信號置位低電平信號接入RS鎖存器,低電平S端,成功的捕捉到了清零信號,并成功進位。

仿真問題3

24進制計數器,制作錯誤

解決方法

將個位和十位的置數端連到一個與非門,連到復位端,構成異步清零的24進制計數器。

仿真問題4

成功的構成了24小時鐘表,在加特殊功能鍵時,將開關的電平信號和秒分進位信號、分時進位信號進行相或時,可以調試,但無秒分進位信號和分時進位信號。

解決方法

將74LS160的異步清零接法,換成了同步預置數法,將相或換成了與開關低電平相與,實現調試功能。

設計說明書目錄.png (111.61 KB, 下載次數: 172)

下載附件

設計說明書目錄

2020-7-20 23:02 上傳

2cc435944f9740251heie22fe1e77fc37.png (28.1 KB, 下載次數: 143)

下載附件

附件內容

2020-7-20 23:06 上傳

全部資料51hei下載地址(仿真+文檔):

簡易鐘表邏輯電路設計.rar

(616.74 KB, 下載次數: 35)

簡易鐘表邏輯電路設計.rar

(616.74 KB, 下載次數: 35)

2020-7-20 23:07 上傳

點擊文件名下載附件

下載積分: 黑幣 -5