壓縮包保護(hù)各模塊的原文件,原理手繪圖。可實(shí)現(xiàn)全部功能。

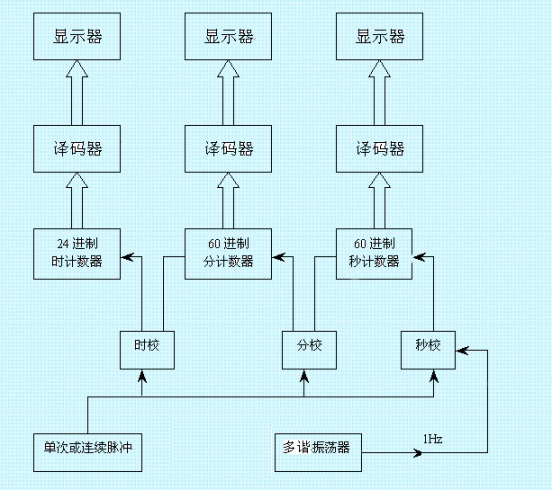

總體設(shè)計(jì) 數(shù)字電子鐘一般由振蕩器、分頻器、計(jì)數(shù)器、譯碼器、顯示器等幾部分組成。采用的555定時(shí)器構(gòu)成的多諧振蕩器來產(chǎn)生秒信號。“秒”、“分”計(jì)數(shù)器為六十進(jìn)制計(jì)數(shù)器,小時(shí)為二十四進(jìn)制計(jì)數(shù)器。仿真軟件中選擇合適的顯示器件,由于走時(shí)不準(zhǔn)確而造成顯示的時(shí)間快或慢,就要對表進(jìn)行校準(zhǔn)。這一功能利用手動(dòng)單脈沖或連續(xù)脈沖對其進(jìn)行校準(zhǔn)。由電源電路提供穩(wěn)定的+5V電壓。 (2)數(shù)字電子鐘設(shè)計(jì)框圖

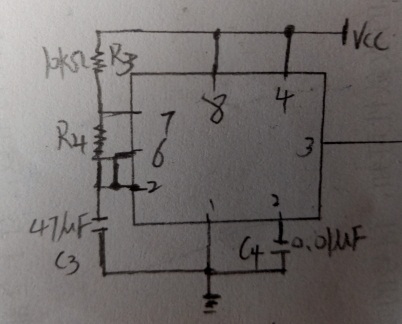

三、詳細(xì)設(shè)計(jì) (1)1Hz標(biāo)準(zhǔn)脈沖發(fā)生器: 1Hz標(biāo)準(zhǔn)脈沖發(fā)生器是數(shù)字鐘的核心部分,它的精度和穩(wěn)定度決定了數(shù)字鐘的質(zhì)量。采用的555定時(shí)器構(gòu)成的多諧振蕩器來產(chǎn)生秒信號。取參數(shù)R 3 =10K,R4 =10K,C3=47μF 。f=1/[ln2(R3+2R4)C3]≈1Hz,即產(chǎn)生1Hz的脈沖信號。而單個(gè)周期為T=(R3+2*R4)*C3*ln2=1s。

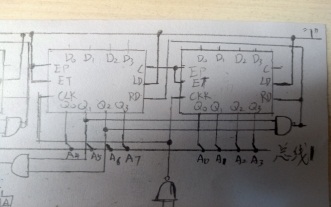

1Hz標(biāo)準(zhǔn)脈沖發(fā)生器 (2)計(jì)數(shù)器 計(jì)數(shù)器由時(shí)分秒組成,分秒為60進(jìn)制計(jì)數(shù)器,計(jì)數(shù)范圍為00~59。時(shí)為24進(jìn)制計(jì)數(shù)器,計(jì)數(shù)范圍為00~23。 設(shè)計(jì)的60和24進(jìn)制加法計(jì)數(shù)器都大于一個(gè)74LS160的計(jì)數(shù)范圍,所以需要級聯(lián)。當(dāng)且僅當(dāng)秒的個(gè)位計(jì)數(shù)到10的瞬間,即輸出為1010時(shí),向本位發(fā)送一個(gè)清零信號,并同時(shí)向十位發(fā)送一個(gè)進(jìn)位脈沖。但是74LS160的清零方式為異步清零,所以必須要把脈沖調(diào)整到一個(gè)較低的周期,才會(huì)產(chǎn)生有效地清零和進(jìn)位信號。為了使清零和進(jìn)位同步進(jìn)行,在清零的輸出端需要引出一根線,加上與門引入下一級計(jì)數(shù)器的輸入端。這種可以實(shí)現(xiàn)多重清零的方式。 分、秒都是60進(jìn)制(00~59),所以它們的電路都是一樣的,采用2片74LS160和與非門實(shí)現(xiàn),該芯片為十進(jìn)制加法器,D四個(gè)引腳全部接地,表示從0開始計(jì)數(shù)。邏輯門組是實(shí)現(xiàn)的關(guān)鍵,當(dāng)記滿59時(shí),再來一個(gè)脈沖就清零變?yōu)?0,接著再重新開始計(jì)數(shù)。 秒計(jì)數(shù)器:

分計(jì)數(shù)器:

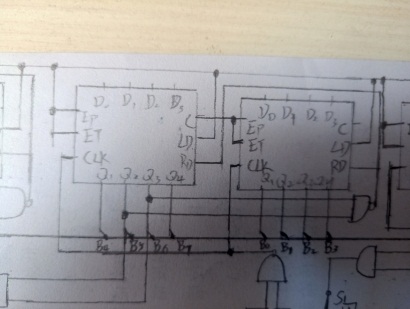

用的2片74LS160芯片以及與非門實(shí)現(xiàn)24進(jìn)制(00~23)。時(shí)計(jì)數(shù)器的十位是二進(jìn)制,個(gè)位是十進(jìn)制,同時(shí)和與非門相連,實(shí)現(xiàn)滿24時(shí)清零。 時(shí)計(jì)數(shù)器:

(3)譯碼顯示

DCD-HEX數(shù)碼管4條引腳從左到右對應(yīng)BCD碼位的左高右低。在Multisim仿真當(dāng)中其內(nèi)部自帶譯碼功能,無需設(shè)計(jì)譯碼電路,可直接連接計(jì)數(shù)器顯示時(shí)間。 (4)校時(shí)電路 由于走時(shí)不準(zhǔn)確而造成顯示的時(shí)間快或慢,就要對表進(jìn)行校準(zhǔn)。由于CLK連續(xù)脈沖(1H Z )只能送給秒計(jì)數(shù)器個(gè)位芯片的CLK端,且在校準(zhǔn)時(shí),僅需校準(zhǔn)脈沖,而秒脈沖無效。因此設(shè)計(jì)門電路滿足此功能。 當(dāng)A為0正常計(jì)數(shù),當(dāng)A為1時(shí)采用校對脈沖輸入。但為了滿足校對時(shí)不產(chǎn)生進(jìn)位的需求,在進(jìn)位端同樣設(shè)計(jì)一開關(guān),由A控制。當(dāng)A為0時(shí),開關(guān)閉合。計(jì)數(shù)器正常計(jì)數(shù)和進(jìn)位,而A為1時(shí),校對脈沖輸入,開關(guān)斷開,不再產(chǎn)生進(jìn)位。 四、組裝電路并調(diào)試 按照原理框圖對數(shù)字時(shí)鐘各部件進(jìn)行組裝連接,調(diào)試。圖見尾頁 五、元件明細(xì)表 六、心得體會(huì) 這學(xué)期一開學(xué)就待在家里線上教學(xué),雖然不能走出去,但通過線上老師辛苦的教學(xué),讓我在家也不會(huì)耽誤學(xué)習(xí)進(jìn)度。這次設(shè)計(jì)自己感覺最大的收獲是更好的認(rèn)識了這門學(xué)科以及自己所學(xué)的專業(yè)。之前一直有疑惑,自己學(xué)這個(gè)能干什么?感覺自己所學(xué)的跟日常所見是不一樣的。但是這次設(shè)計(jì)的成功完成,讓我看到了另一番不同的天地。極大提升了自己的學(xué)習(xí)興趣。這次設(shè)計(jì)也加強(qiáng)了我對multisim仿真軟件的運(yùn)用,相信對我以后的學(xué)習(xí)有很大幫助,這次課設(shè)也進(jìn)一步鞏固了課上學(xué)習(xí)的各種知識。 當(dāng)然突然拿到這個(gè)項(xiàng)目還是比較迷茫的,無從下手。所以我花了些時(shí)間去分析題目,設(shè)計(jì)原理圖,了解基本運(yùn)行原理來論證和改進(jìn)。基本方案確定后,再去查資料,通過Multisim仿真、請教同學(xué)來重新改進(jìn)。雖然實(shí)際運(yùn)行中出現(xiàn)了很多問題,換了不少設(shè)計(jì),有時(shí)無法找出錯(cuò)誤就換元器件重新接線。有些在理論上可行的電路在調(diào)試中未必正確,這就需要耐心、仔細(xì)分析和解決問題,不斷嘗試才能得出正確的答案。最后完成了項(xiàng)目并驗(yàn)證,把理論和實(shí)際緊密的聯(lián)系在了一起。

附錄:總體電路連接圖

51hei.png (19.29 KB, 下載次數(shù): 327)

下載附件

2020-7-1 22:22 上傳

全部資料51hei下載地址:

仿真源文件.zip

(1.63 MB, 下載次數(shù): 140)

仿真源文件.zip

(1.63 MB, 下載次數(shù): 140)

2020-7-1 22:35 上傳

點(diǎn)擊文件名下載附件

下載積分: 黑幣 -5

手繪電路圖清晰.7z

(126.09 KB, 下載次數(shù): 39)

手繪電路圖清晰.7z

(126.09 KB, 下載次數(shù): 39)

2020-7-1 22:35 上傳

點(diǎn)擊文件名下載附件

下載積分: 黑幣 -5

|