Quartus II9.0 進行的EDA頻率計設計

1.png (16.03 KB, 下載次數: 86)

下載附件

2020-5-9 10:56 上傳

1、頻率計的測量范圍為1MHz,量程分10KHz、100KHz和1000KHz三檔(最大讀數分別為9.99KHz、99.9KHz、999KHz)。

2、當讀數大于999時,頻率計處于超量程狀態。此時顯示器發出溢出指示(最高位顯示F,其余各位不顯示數字),下一次測量時,量程自動增大一檔。讀數小于000時,頻率計處于欠量程狀態。下次測量時,量程減小一檔。 3、要求實現溢出報警功能。即當頻率高于999KHz時,頻率計處于超量程狀態,產生一報警信號,點亮LED燈,從而實現溢出報警功能。 4、用記憶顯示方式,即計數過程中不顯示數據,待計數過程結束后,顯示計數結果,并將此顯示結果保持到下一次計數結束。顯示時間應不小于1秒,小數點位置隨量程變更自動移位。 2. 系統總體設計 本設計采用的是直接測頻率的方法。即測頻率法就是在一定的時間間隔內TW內,得到這個周期信號重復變化的次數NX,則被測頻率可表示為FX=NX/TW。 頻率計的系統設計可以分為計頻基準時鐘模塊、自動換檔模塊、4位10進制計數模塊鎖存模塊、譯碼顯示模塊。 計頻基準時鐘模塊: 以1kHZ為基準,產生三個不同占比的0.5Hz脈沖信號其高電平時間分別為1s、0.1s、0.01s,分別用以測量頻率在0~9.99KHz、0~99.9KHz、0~999KHz的頻率。 自動換檔模塊: 先以最低檔位測量,溢出時下一次計數自動切換高檔位,計數不滿“000”下一次自動切換到低檔位。計數溢出999khz時,發出警報。 四位10進制計數模塊鎖存模塊: 四位十進制計數,檔位基準信號為高電平時,開始計數,低電平時鎖存輸出計數結果的前三位,計數器清零。當溢出或計數不滿時,輸出換擋信號。計數刷新頻率為0.5Hz。 譯碼顯示模塊: 將計數器輸出的結果按位譯成7段顯示數碼管對應數字碼,根據所選檔位信號設置小數點位置。刷新頻率為 系統框圖(可打印) 3. 系統詳細設計 3.1 計頻基準時鐘模塊設計 該模塊的電路框圖 各輸入輸出引腳的定義及作用 Clk:為基準時鐘信號,選用1kHz時鐘信號 F0:根據clk分頻出的0.5Hz高電平為1s的計頻信號,用以0~9.99kHz檔計頻。 F1:根據clk分頻出的0.5Hz高電平為0.1s的計頻信號,用以0~99.9kHz檔計頻。 F2:根據clk分頻出的0.5Hz高電平為0.01s的計頻信號,用以0~999kHz檔計頻。 - library ieee;

- use ieee.std_logic_1164.all;

- use ieee.std_logic_arith.all;

- use ieee.std_logic_unsigned.all;

- entity dw is port(clk:in std_logic;

- f0:out std_logic;

- f1:out std_logic;

- f2:out std_logic);

- end dw;

- architecture body_dw of dw is

- begin

- process(clk) --clk選用1kHz時鐘信號

- variable ct:integer range 0 to 2000;

- begin

- if clk'event and clk='1'then --分頻周期為2s的脈沖

- ct:=ct+1;

- if ct=2000 then ct:=0;

- end if;

- if ct<1000 then f0<='1';

- elsif ct<2000 then f0<='0'; --f0為0.5Hz高電平為1s

- end if;

- if ct<100 then f1<='1';

- elsif ct<2000 then f1<='0'; --f1為0.5Hz高電平為0.1s

- end if;

- if ct<10 then f2<='1';

- elsif ct<2000 then f2<='0'; --f2為0.5Hz高電平為0.01s

- end if;

- end if;

- end process;

- end body_dw;

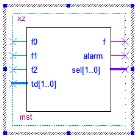

(可打印) 仿真波形(可打印) 對波形的分析說明: Ct為整數計數,檢測到clk上升沿時則加一計數,f0,f1,f2根據ct計數結果分頻輸出所需脈沖。 3.2 自動換檔模塊設計  f0,f1,f2為各檔位計頻信號 f0,f1,f2為各檔位計頻信號 td為換擋信號 f為所選檔位輸出的測頻信號 sel輸出檔位選擇信號,用以小數點位置控制 alarm為999kHz溢出報警 - library ieee;

- use ieee.std_logic_1164.all;

- use ieee.std_logic_arith.all;

- use ieee.std_logic_unsigned.all;

- entity xz is port(f0:in std_logic;

- f1:in std_logic;

- f2:in std_logic;

- td:in std_logic_vector(1 downto 0);

- f:out std_logic;

- alarm:out std_logic;

- sel:out std_logic_vector(1 downto 0)); --輸出檔位選擇信號

- end xz;

- architecture body_xz of xz is

- begin

- process(td,f0)

- variable dwxz:std_logic_vector(1 downto 0);

- begin

- if f0'event and f0='1' then --計數前以0.5Hz信號的上升沿檢測是否有換擋信號

- if td="10" then --換擋信號td為10表示切換到高一檔

- if dwxz="10" then alarm<='1'; --如果檔位已是最高,則報警

- else dwxz:=dwxz+1;

- alarm<='0'; --正常換擋則消除報警

- end if;

- elsif td="01" then --換擋信號td為01表示切換到低一檔

- if dwxz="00" then null;

- else dwxz:=dwxz-1;

- alarm<='0';

- end if;

- else alarm<='0'; --正常計頻,消除報警

- end if;

- sel<=dwxz;

- if dwxz=0 then f<=f0;end if;

- if dwxz=1 then f<=f1;end if;

- if dwxz=2 then f<=f2;end if;

- end process;

- end body_xz;

開始時量程輸出為(檔位選擇)sel=“00”,即最小檔,輸出f為f0,當接收到(調檔)td=“10”切換高一檔,sel變為“10”。 3.3 四位10進制計數鎖存模塊設計 M輸入被測量信號 En輸入測量脈沖,高電平時開始計頻率,低電平輸出鎖存結果。 q3,q2,q1為鎖存的計頻結果。 Td在溢出和欠量程時候輸出調檔信號。 library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity js is port(m:in std_logic;

en:in std_logic;

q1,q2,q3:out std_logic_vector(3 downto 0);

td:out std_logic_vector(1 downto 0));

end js;

architecture body_js of js is

signal js_td:std_logic_vector(1 downto 0);

signal b3,b2,b1: std_logic_vector(3 downto 0);

begin

process(en,m)

variable w0,w1,w2,w3:std_logic_vector(3 downto 0); --四位十進制計數

begin

if en='1' then --當計頻脈沖為1是開始計數

if m'event and m='1' then

if w3="1010" then null;

else w0:=w0+1;

if w0="1010" then

w0:="0000";w1:=w1+1;

if w1="1010" then

w1:="0000";w2:=w2+1;

if w2="1010" then

w2:="0000";w3:=w3+1;

end if ;

end if ;

end if;

end if;

b1<=w1; --計數結果實時緩存至b1,b2,b3

b2<=w2;

b3<=w3;

end if ;

end if ;

if en='0'then

q1<=b1; --en檔位脈沖為低電平時b1,b2,b3結果為最終值,保持不變

q2<=b2; --將結果輸出至Q1,Q2,Q3

q3<=b3; --當下一次低電平時,刷新計數結果

w0:="0000";

w1:="0000"; --低電平時,計數器清零

w2:="0000";

w3:="0000";

end if;

end process;

process(en) --計數一結束,以下降沿觸發判斷是否欠量程或則溢出

begin --并輸出相應調檔信號

if en'event and en='0'then

if b1="0000" and b2="0000" then

if b3="0000" then td<="01";

elsif b3="1010" then td<="10";

elsif b3>"0000"and b3<"1010" then td<="00";

end if;

end if;

end if;

end process;

end body_js;

En脈沖為99.9Hz量程脈沖 m被測脈沖設置為0~5s 50Hz;5~10s 10000Hz;10~13s 100000Hz; 第一個測量脈沖判定結果為欠量程,調檔信號TD輸出01,調低檔位 第三個脈沖檢測判定10.0kHz,在量程范圍,調檔不做輸出 第六個脈沖檢測判定100kHz,溢出,調檔TD輸出10,調高檔位

3.4 譯碼模塊 Clk為1kHz時鐘信號,用以觸發賦值語句等 Sel為檔位信號 Q1,Q2,Q3為計數器鎖存結果輸入 LED0,LED1,LED2為三位結果的譯碼輸出

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity ym is port(

clk:in std_logic;

sel:in std_logic_vector(1 downto 0);

q1,q2,q3:in std_logic_vector(3 downto 0);

led0,led1,led2:out std_logic_vector(7 downto 0));

end ym;

architecture body_ym of ym is

signal tp:std_logic_vector(3 downto 0);

signal led:std_logic_vector(6 downto 0);

begin

led<="0111111"when tp="0000"else --0

"0000110"when tp="0001"else --1

"1011011"when tp="0010"else --2

"1001111"when tp="0011"else --3

"1100110"when tp="0100"else --4

"1101101"when tp="0101"else --5

"1111101"when tp="0110"else --6

"0000111"when tp="0111"else --7

"1111111"when tp="1000"else --8

"1101111"when tp="1001"else --9

"1110001"when tp="1010"; --F

process(clk,sel)

variable c:std_logic_vector(1 downto 0) ;

begin

if clk'event and clk='1' then

if c="10"then c:="00";

else c:=c+1;

end if;

if q3="1010"then --溢出顯示F

led2<="01110001";

led1<="00000000";

led1<="00000000";

else

if sel="10" then --999KHZ檔小數點賦值

case c is

when "00"=>tp<=q2;

led0<='1'&led;

when "01"=>tp<=q3;

led1<='0'&led;

when "10"=>tp<=q1;

led2<='0'&led;

when others=>null;

end case;

elsif sel="01" then -- 99.9khz檔小數點

case c is

when "00"=>tp<=q2;

led0<='0'&led;

when "01"=>tp<=q3;

led1<='1'&led;

when "10"=>tp<=q1;

led2<='0'&led;

when others=>null;

end case;

elsif sel="00" then --9.99kHz檔小數點

case c is

when "00"=>tp<=q2;

led0<='0'&led;

when "01"=>tp<=q3;

led1<='0'&led;

when "10"=>tp<=q1;

led2<='1'&led;

when others=>null;

end case;

end if;

end if;

end if;

end process;

end body_ym;

設置0~2s 輸出為1017,溢出,LED2輸出F的段碼,兩外兩個消隱。 設置2s后輸出217,按照(量程選擇)sel=0時,為0~9.99khz,小數點在高位即led2[7]為1。 3.4 顯示模塊 Clk:動態顯示觸發信號,1khz每一個點亮一個數碼管,三個循環,其頻率顯然大于人眼可識別。 Led0,led1,led2:為譯碼輸出的數碼管顯示信號。 Ledag,sel:為動態顯示

library ieee;

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity dynamic_display is port(clk:in std_logic;

ledag:out std_logic_vector(7 downto 0);

sel:out std_logic_vector(2 downto 0);

led0,led1,led2:in std_logic_vector(7 downto 0));

end dynamic_display;

architecture body_display of dynamic_display is

begin

process(clk)

variable c:std_logic_vector(1 downto 0) ;

begin

if clk'event and clk='1' then

if c="10"then c:="00";

else c:=c+1;

end if;

end if;

case c is

when"00"=>sel<="001";

ledag<=led0;

when"01"=>sel<="010";

ledag<=led1;

when"10"=>sel<="100";

ledag<=led2;

when others=>null;

end case;

end process;

end body_display;

4. 系統調試 4.1 系統總體仿真 系統總體輸入輸出引腳的定義及作用 仿真波形(可打印) M在0~6s 設置為1000Hz 讀取波形led為1.00kHz

M在6~12s 設置為100khz 讀取顯示應為100.khz

M在6~12s 設置為1mhz Alarm 溢出報警 顯示為F 0

51hei.png (6.96 KB, 下載次數: 104)

下載附件

2020-5-9 15:19 上傳

全部資料51hei下載地址:

頻率計.zip

(3.3 MB, 下載次數: 85)

頻率計.zip

(3.3 MB, 下載次數: 85)

2020-5-9 10:51 上傳

點擊文件名下載附件

下載積分: 黑幣 -5

|