|

(1) 設計該課題所需的六十進制、二十四進制。 (2) 設計數碼管譯碼顯示電路。 (3) 設計秒與分、分與時之間的進位控制電路。 (4) 設計整點提醒電路。 (5) 設計手動校時電路。

2 電路總體設計

設計框圖:

總體原理說明: 整體電路共分為五大模塊: 脈沖產生模塊、 計時模塊、譯碼顯示模塊、 整點報時模塊、 校時模塊。 主要由555定時器器、秒計數器、分計數器、時計數器、 BCD-七段顯示譯碼 / 驅動器、 LED七段顯示數碼管、時間校準電路構成以及各種門電路。 數字鐘數字譯碼顯示部分,采用共陰譯碼器與共陰極數碼管串聯電路,將譯碼器、 七段數碼管連接起來之間串個組排,組成十進制數碼顯示電路, 即時鐘顯示。要完成顯示需要 6 個數碼管, 八段的數碼管需要譯碼器將計數信號譯碼成BCD碼才能顯示,然后要實現時、分、秒的計時需要 60 進 制計數器和 24 進制計數器,脈沖發生電路則有555定時器構成的多諧振蕩電路。 60 進制則由 10進制和 6 進制的計數器串聯而成,。 計數器的輸出分別經譯碼器送顯示器顯示。 計時出現誤差時,可以用校時電路校 時、校分。校時電路由復位按鈕構成,復位按鈕按下產生手動脈沖,從而調節計數器,實現校時。 整點報時電路則有門電路構成的判斷模塊對時計時和分計時的輸出進行判斷,從而實現整點報時。

3各部分電路設計 3.1 脈沖產生模塊設計 脈沖發生電路采用555構成的多諧振蕩電路。

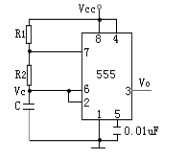

用 555 定時器構成的多諧振蕩器電路如圖所示:圖中電容 C、電阻 R1 和 R2 作 為振蕩器的定時元件,決定著輸出矩形波正、負脈沖的寬度。定時器的觸發輸入端(2腳)和閥 值輸入端(6 腳)與電容相連;集電極開路輸出端(7腳)接 R1、R2 相連處,用以控制電容 C 的充、放電;外界控制輸入端(5腳)通過 0.01uF 電容接地。

多諧振蕩器的工作波形如圖 6-11(b) 所示: 電路接通電源的瞬間,由于電容 C 來不及充電, Vc=0v ,所以 555 定時器狀態為 1,輸出 Vo 為高電平。同時,集電極輸出端(7 腳)對地斷開,電源 Vcc 對電容 C 充電,電路進入暫穩態 I,此后,電路周而復始地產生周期性的輸出脈沖。多諧振蕩器兩個暫穩態的維持時間取決于 RC 充、放電回路的參數。暫穩態Ⅰ的維持時間,即輸出 Vo 的正向脈沖寬度 T1≈0.7(R1+R 2)C; 暫穩態Ⅱ的維持時間,即輸出 Vo 的負向脈沖寬度 T2≈0.7R 2C。 因此, 振蕩周期 T=T 1+T 2=0.7(R 1+2R 2 )C,振蕩頻率 f=1/T 。正向脈沖寬度 T1 與振蕩周期 T 之比稱矩形波的 占空比D ,由上述條件可得 D=(R1+R2)/(R1+2R 2),若使 R2>>R 1,則 D≈1/2, 即輸出信號的正負向脈沖寬度相等的矩形波(方波)。

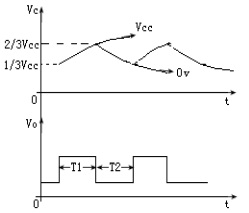

仿真電路如下圖1:

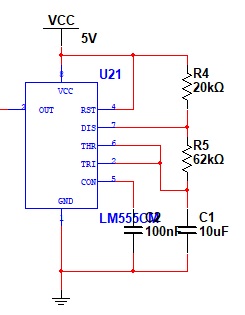

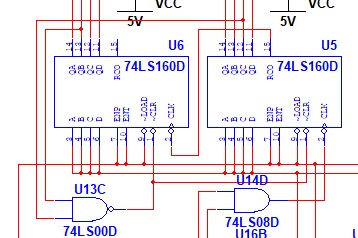

圖1 3.2計時模塊設計 (1)分、秒計時 在數字鐘的控制電路中, 分和秒的控制都是一樣的, 都是由一個十進制計數器和一個六進制計數器串聯而成的,在電路的設計中我采用的是統一的器件 74LS160D的異步清零法來實現十進制功能和六進制功能, 根據 74LS160D的結構 把輸出端的 0110(十進制為 6)用一個與非門 74LS00引到 CLR端便可置 0,這 樣就實現了六進制計數。而74LS160D本身為計滿后為10,與前文6進制串聯后成60進制。 仿真電路如下圖2所示:

圖2 (2)時計時器 由兩片十進制同步加法計數器 74LS160 級聯產生,采用的是異步清零法, u1輸出端為 0001(十進制為 4)與 u2輸出端 0010(十進制為2)經過與非門接 兩片的清零端,從而實現了24進制計數。 仿真電路如下圖3所示:

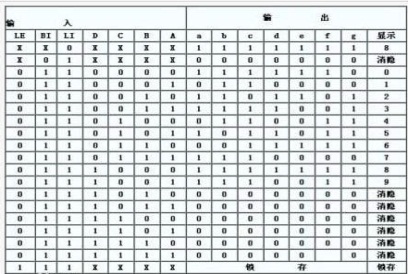

圖3 3.3 譯碼顯示模塊設計 譯碼顯示模塊采用共陰極數碼管及共陰七段數碼管譯碼器驅動器CD4511構成。 CD4511 是一片 CMOS BCD—鎖存/7 段譯碼/驅動器,用于驅動共陰極 LED (數碼管)顯示器的 BCD 碼-七段碼譯碼器。具有BCD轉換、消隱和鎖存控制、七段譯碼及驅動功能的CMOS電路能提供較大的拉電流。可直接驅動共陰LED數碼管。 其功能表如下所示:

將計數器輸出連接至譯碼器輸入,再將譯碼器輸出接入數碼。 數碼管本質為LED燈構成所以需要串聯電阻進行分壓,防止LED燈燒毀。 仿真圖如下圖4所示:

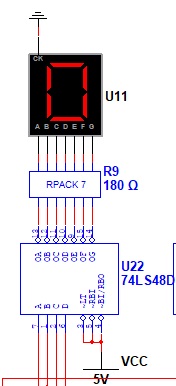

圖4 3.4 整點報時模塊設計 整點報時電路由門電路以及蜂鳴器構成。 由門電路判斷整時,即判斷59分50秒,即分計時為(0110)、(1001),秒計時為(0110)。以此判斷整時,實現整時報時。 門電路由74LS20D四輸入與非門判斷(0110)、(1001),二輸入與非門判斷(0110)。 仿真電路如下圖5所示:

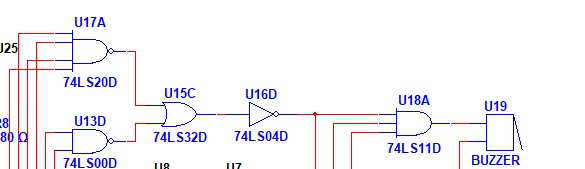

圖5 3.5校時模塊設計 校時模塊電路由復位按鈕及二輸入或門構成。 復位按鈕上拉電阻,當分為按鈕按下時,電阻接地,電平由高變低,實現手動產生脈沖。 將手動脈沖以及進位產生的脈沖分別輸入二輸入或門,或門輸出進入計數器CLK端,則當按鈕按下手動脈沖產生,計時器亦會進行計時,從而實現校時。 仿真電路如下圖6所示:

圖6

4 結論 通過對軟件 Multisim 的學習和使用,進一步加深了對數字電路的認識。在 仿真過程中遇到許多困難, 但通過自己的努力和同學的幫助都一一克服了。 首先, 連接電路圖過程中, 數碼管不能顯示, 后經圖形放大后才發現是電路斷路了。 其 次,布局的時候因元件比較多,整體布局比較困難,因子電路不如原電路直觀, 最后在不斷努力下,終于不用子電路布好整個電路。 調試時有的器件在理論上可行, 但在實際運行中就無法看到效果, 所以得換 不少器件,有時無法找出錯誤便更換器件重新接線以使電路正常運行。 在整個設 計中,74LS160的接線比較困難,反復修改了多次,在認真學習其用法后采用歸 零法和置數法設計出 60 進制和 24 進制的計數器。 同時,在最后仿真時,預置的頻率一開始用的是 1hz,結果仿真結果反應很 慢,后把頻率加大, 這才在短時間內就能看到全部結果。總之, 通過這次對數字 時鐘的設計與仿真, 為以后的電路設計打下良好的基礎, 一些經驗和教訓, 將成 為寶貴的學習財富。

全部資料51hei下載地址:

數字鐘改_1.zip

(1.18 MB, 下載次數: 291)

數字鐘改_1.zip

(1.18 MB, 下載次數: 291)

2019-11-5 20:47 上傳

點擊文件名下載附件

|