|

�n�����Q����(sh��)��߉�·���A �ڶ���ԇ� ������Q���ɾ��̔�(sh��)��߉�O(sh��)Ӌ���A(ch��) Ժϵ����ӿƌW(xu��)�c���̌W(xu��)Ժ ���I(y��)����ӿƌW(xu��)�c���g(sh��)��� Ŀ�ĺ�Ҫ�� - �˽�ɾ��̔�(sh��)��ϵ�y(t��ng)�O(sh��)Ӌ������

- ����Quartusܛ����ʹ�÷���

- ���ո�����ð�U�Ļ���������·�ĕr�ӷ�������

- ���ԭ�������F(xi��n)������

���ԭ���� - �^�첢ӛ䛌�����ϵ�FPGA��̖���½�һ��Project,�����x�Ì�����ϵ�FPGA;

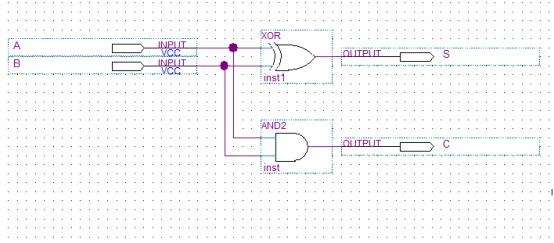

����Ӳľ�n���ϵ�FPGA��̖�顱Cyclone ����������������õİ汾Quartus9.1��֧�ִ���̖���������½�project�r����Assignment���x��Device,�x�����е�Family�������c����Cyclone��Available devices�б����x��EP3C5E144C8,�c����OK�����ɡ� - �á�AND2���͡�XOR�������O(sh��)Ӌһ��1λ����������ù��ܷ����M����C��

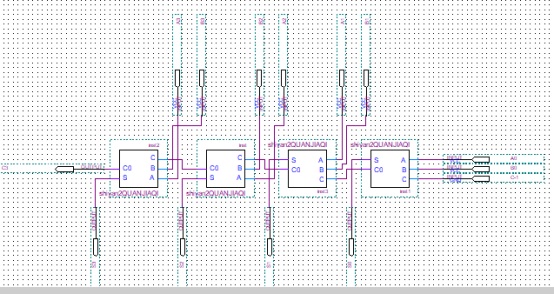

�O(sh��)Ӌ��������AND2��һ����ݔ���c�T��XOR���ݔ�뮐���T�����һλ������o�Mλݔ�����������O(sh��)ݔ��׃����A�cB��ݔ��׃����S��C��S��Y(ji��)����C���Mλݔ������ �ڸ���(j��)һλ�������Ҫ���г���ֵ�����±���ʾ�� �����ݔ��������(sh��)�^�٣�ֱ�Ӹ���(j��)��ֵ���ɵ�S=A��B+AB��,����A�cB�Į��� C=AB�����ԓ�(j��)�˵õ��˶�ݔ����߉����(sh��)��S=A��B+AB����C=AB�� ���c��File�е�New헣������F(xi��n)�½��ļ���Ԓ���x��Design File/Block Diagram/Schematic File��헣��c����OK�����ɴ��_��Block Editor��,�p��ԭ��D�հײ��֣���name���зքe����imput��output��XOR��AND2�õ�����Ԫ����Ȼ���������(c��)�L�D���߽���ԭ��D��������Project����ͬ�ļ��A�С����D��ʾ��

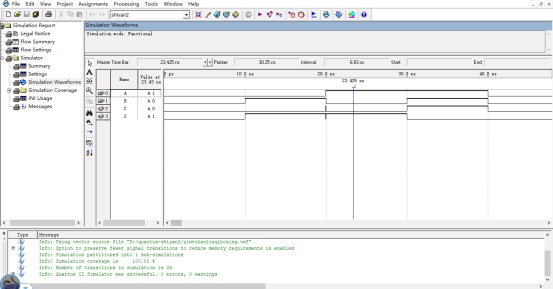

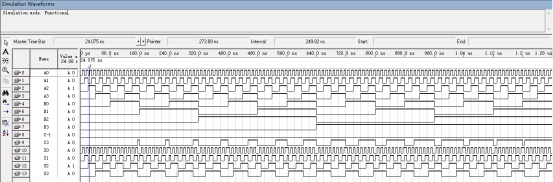

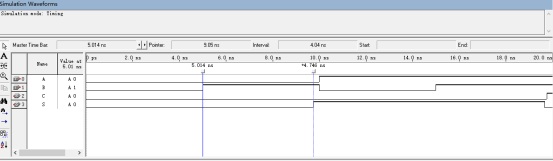

�ݹ�����C�� �����c��Project Navigator/files/Device Design Files,�x��Ҫ���g�ġ�yiweibanjiaqi.bdf���ļ������I���䡰Set as Top-level Entity��,�Ȳ�������_�����潨��ݔ�뼤����ļ�������New/Verification/Debugging Files/Vector Waveform File�����ļ����p��Name�հ�̎������Insert Node or Bus/Node Finder/list/��>>�������������D�Ĺ��ߌ��������ɺ��䡰Save����Project���ļ��A�У�ע�������Ƽ���εĕr����Edit/End time.Grid size�O(sh��)�úý�ֹ�r�g�Է����O(sh��)�����ڼ�����ĕr�ӷ�����Ȼ���ա�Processing/Simulator Tool/Functional��,Ȼ����Simulator input��ָ��֮ǰ������IJ��μ����ļ������ա�Generate Functional Simulator Netlist�����ɹ��ܷ���W(w��ng)���ļ����c����Start���M�з���Ӌ�㣬��ɺ��c����Report�����_����Y(ji��)�����Ρ�����Y(ji��)���������£�

�������ݔ��ݔ�������c��ֵ����Ȍ�ݔ���Y(ji��)����ȫ���_��������C��ɡ� - �c����File��?��Create/Update����Create Symbol File for Current File���ˆ�헣���1λ��������b��Ԫ�����½�һ��ԭ��D�ļ����{(di��o)��2����������F(xi��n)һ��1λȫ���������ù��ܷ����M����C��

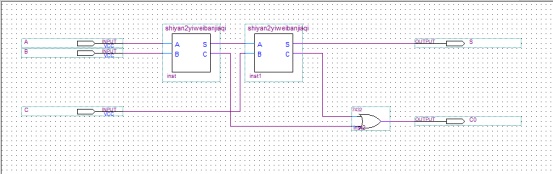

��������Ĺ��ܷ���Y(ji��)����ֱ���ڮ�(d��ng)ǰ�����°��ա�File/Create/Update/Create Symbol File for Current File�������?q��)�һλ��������b��Ԫ�������顰shiyan2yiweibanjiaqi�������b�����. �O(sh��)Ӌ�������O(sh��)Ӌһ��һλȫ������Ҫ����ݔ��������̎���x��A,B,C,����A,B��Ӕ�(sh��)�c���Ӕ�(sh��)��C��ݔ���Mλ����ݔ������S�cC0��S��ͣ�C0��ݔ���Mλ���ȸ���(j��)һλȫ�����Ķ��x�г���ֵ�����±���ʾ�� ����(j��)������ֵ���г����Z�D���D��ʾ�� �ٌ�S��

����(j��)���Z�D���������õ��P(gu��n)��ݔ����S��߉����(sh��)���_ʽ�飺S=A��B��C; �ٌ�C0�� ����(j��)���Z�D���������õ��P(gu��n)��ݔ����C0��߉����(sh��)���_ʽ�飺C0=AB+AC; �������߉����(sh��)���_ʽ�_��ԭ��D���L���^�����£�Ȼ����֮ǰ����ԭ��D������c��File�е�New헣������F(xi��n)�½��ļ���Ԓ���x��Design File/Block Diagram/Schematic File��헣��c����OK�����ɴ��_��Block Editor��,�p��ԭ��D�հײ��֣���name����������yiweibanjiaqi�������{(di��o)���������b��һλ�����Ԫ�����^�m(x��)��������(y��ng)�ġ�output/input/7432(���T)������������߉����(sh��)�M��ԭ��D���L�ƣ��L�ƺ��ԭ��D������ʾ��

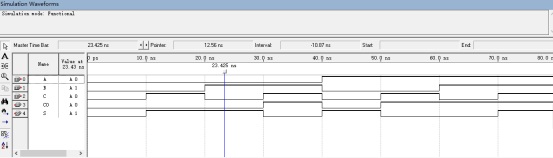

�����c��Project Navigator/files/Device Design Files,�x��Ҫ���g�ġ�yiweibanjiaqi.bdf���ļ������I���䡰Set as Top-level Entity��,�Ȳ�������_�����潨��ݔ�뼤����ļ�������New/Verification/Debugging Files/Vector Waveform File�����ļ����p��Name�հ�̎������Insert Node or Bus/Node Finder/list/��>>�������������D�Ĺ��ߌ��������ɺ��䡰Save����Project���ļ��A�У�ע�������Ƽ���εĕr����Edit/End time.Grid size�O(sh��)�úý�ֹ�r�g�Է����O(sh��)�����ڼ�����ĕr�ӷ�����Ȼ���ա�Processing/Simulator Tool/Functional��,Ȼ����Simulator input��ָ��֮ǰ������IJ��μ����ļ������ա�Generate Functional Simulator Netlist�����ɹ��ܷ���W(w��ng)���ļ����c����Start���M�з���Ӌ�㣬��ɺ��c����Report�����_����Y(ji��)�����Ρ�����Y(ji��)���������£�

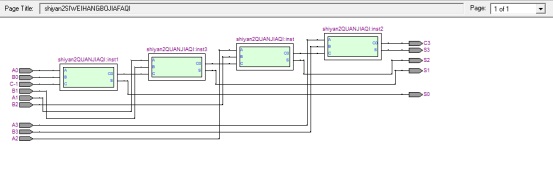

������ĽY(ji��)�������c��ֵ������^���Y(ji��)��һ�£�������C�ɹ���ɡ� - �� 1 λȫ�������b��Ԫ�����½�ԭ��D�ļ����{(di��o)�� 4 ��ȫ�������F(xi��n)һ�� 4 λ�в��ӷ������ù��ܷ����M ����C���á�Tools����Netlist Viewers����RTL Viewer���鿴�·�C�ϽY(ji��)����

��������Ĺ��ܷ���Y(ji��)����ֱ���ڮ�(d��ng)ǰ�����°��ա�File/Create/Update/Create Symbol File for Current File�������?q��)�һλȫ�������b��Ԫ�������顰yiweiquanjiaqi�������b�����. �O(sh��)Ӌ�������O(sh��)Ӌһ����λ�в��ӷ�����Ҫ�ł�ݔ��������C-1,A3,A2,A1,A0,B3,B2,B1,B0����ʾ������C-1���λλ�Mλ����̎���㡣�O(sh��)Ӌ�в��ӷ������ò�����Ӵ����Mλ�ķ�ʽ����λȫ�������Mλ�M����һλ�ļӷ�����������λ�в��ӷ�������r�^�࣬�҂�ֻ��ԭ���ĽǶ��M�з�������̎�����г���ֵ��������(j��)��λ�в��ӷ����Ĺ���ԭ���ɮ��������ԭ��D�� Ȼ����֮ǰ����ԭ��D������c��File�е�New헣������F(xi��n)�½��ļ���Ԓ���x��Design File/Block Diagram/Schematic File��헣��c����OK�����ɴ��_��Block Editor��,�p��ԭ��D�հײ��֣���name����������yiweiquanjiaqi�������{(di��o)���������b��һλȫ����Ԫ�����^�m(x��)��������(y��ng)�ġ�output/input����������������ԭ���M��ԭ��D���L�ƣ��L�ƺ��ԭ��D������ʾ��

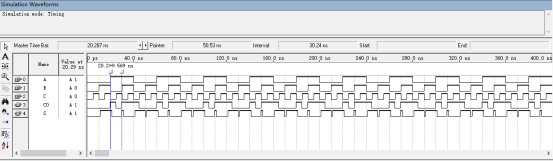

��������ԭ��D֮�������c��Project Navigator/files/Device Design Files,�x��Ҫ���g�ġ�yiweiquanjiaqi.bdf���ļ������I���䡰Set as Top-level Entity��,�Ȳ�������_�����潨��ݔ�뼤����ļ�������New/Verification/Debugging Files/Vector Waveform File�����ļ����p��Name�հ�̎������Insert Node or Bus/Node Finder/list/��>>�������������D�Ĺ��ߌ��������ɺ��䡰Save����Project���ļ��A�У�ע�������Ƽ���εĕr����Edit/End time.Grid size�O(sh��)�úý�ֹ�r�g�Է����O(sh��)�����ڼ�����ĕr�ӷ�����Ȼ���ա�Processing/Simulator Tool/Functional��,Ȼ����Simulator input��ָ��֮ǰ������IJ��μ����ļ������ա�Generate Functional Simulator Netlist�����ɹ��ܷ���W(w��ng)���ļ����c����Start���M�з���Ӌ�㣬��ɺ��c����Report�����_����Y(ji��)�����Ρ�����Y(ji��)���������£�

������C�Y(ji��)���c߉ֵһ�£�������C��ɡ� ���������}��Ҫ����ʾ�鿴�·�C��Ч�����Y(ji��)�����£�

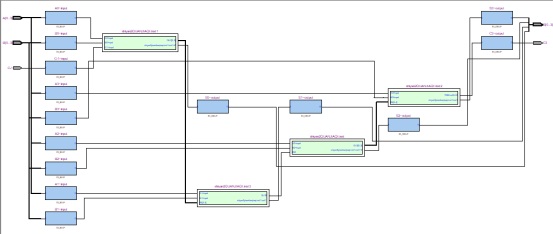

- �m�侎�g���á�Tools����Netlist Viewers����Technology Map Viewer���鿴�· Map �Y(ji��)������ ��Tools��?��Chip Planner���鿴�����m��Y(ji��)����

�����}�ɲ鿴�·Map�Y(ji��)����Ч�����£�

�����}�ɲ鿴�����m��Y(ji��)����Ч�����£� �� 6.�� 4 λȫ�������d������䣬�B��߉�ƽ�_�P(gu��n)�M�й�����C���n��(n��i)��գ��� Ӳľ�n���ϵ�FPGA��Cyclone ��������Quartus9.1�汾��Device�����°汾FPGAֻ����Cyclone �ʌ�FPGA���c��X�B��Ȼ����_��X�O(sh��)��������x��ͨ�ô��п��������������x�����еġ�Altera USB-Blaster��,���I�x�����(q��)�ӳ�������(j��)��?q��)��c�����g�[�ҵ�Ӌ��C�Բ����(q��)�ӳ���ܛ�������ҵ�Quartus���b���еġ�drivers��,���x���������ļ��A���M���(q��)���O(sh��)��ĸ��¼��ɡ� �½�project�r����Assignment���x��Device,�x�����е�Family�������c����Cyclone �� E����Available devices�б����x��EP4CE6F17C7,�c����OK�����ɡ�����FPGA����Ĺ��_����(sh��)�o��λ�в��ӷ����������_����C-1���_������KEY0̎��������߉�ƽSW0~SW7����ݔ������ݔ������LED0~LED4�����c�������@ʾݔ���������_������ɺ��c����Programmer��,����Ӳ����USB-Blaster,�c��start���_ʼ߉�ƽ�Ĺ�����C����ͨ�^�n��(n��i)��ա� - �� 1 λ��������M�Еr����棬�����r�ӷ������Ʌ����A(y��)��֪�R���P(gu��n)��(n��i)�ݣ�

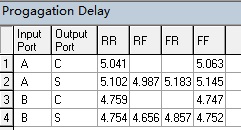

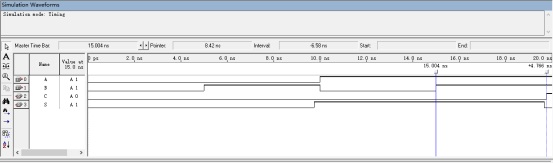

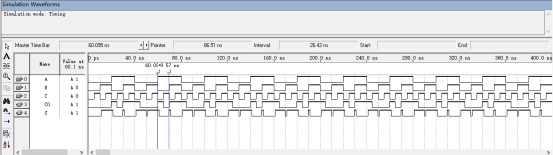

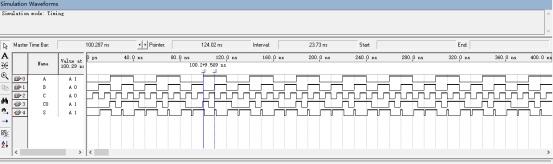

�����c��Project Navigator/files/Device Design Files,�x��Ҫ���g�ġ�yiweibanjiaqi.bdf���ļ������I���䡰Set as Top-level Entity��,Ȼ���ա�Processing/Simulator Tool���M�������棬Simulator mode���������x��Timing��,������ļ��x��֮ǰ�����ġ�shiyan2yiweibanjiaqi.vmf���ļ���start֮���x��Report���Բ鿴����Y(ji��)�����Ρ� �ڲ鿴����Y(ji��)������֮ǰ���҂��Ȳ鿴�·�ĕr����Ϣ���r����Ϣ���±���ʾ��

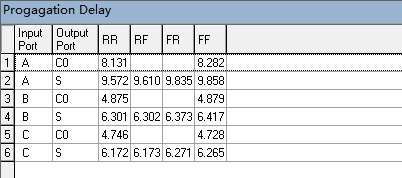

����RR,RF,FR,FF�քe��ʾݔ����Ϣ׃���cݔ����������(y��ng)֮�g�ĕr�g����r�ӣ������҂��鿴����Y(ji��)�����Σ����D��ʾ��

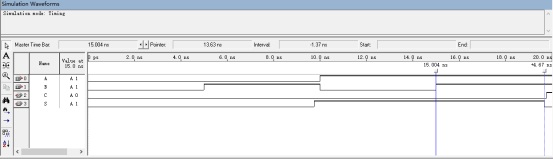

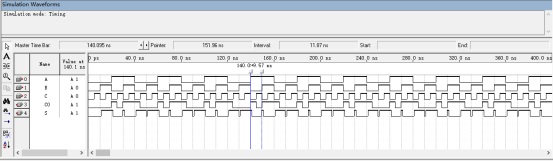

Ȼ��ͨ�^�ɂ�TimeBar���_���r����Ϣ����D����ʾ����(d��ng)B��0׃��1�r��CҲ��0׃��1���˕r�r�g���4.766ns������B��C��RR,�c�ϱ��б��^�`���4.766-4.759=0.007ns���`���^С��ͬ����֪��B��S��RF��4.67ns���c���Еr�Ӕ�(sh��)��(j��)����0.014ns,�`���^С��B��S��RR=4.746ns���c�����л���һ�£��f���r�g���t�c���Д�(sh��)��(j��)����һ�¡���ֱ�Ӱ��ձ��Еr�Ӕ�(sh��)��(j��)�M���·�ķ����� - �� 1 λȫ�������M�Еr����棬�����r�ӷ�����Ҫ��a) �y��A��1~4�������ص�����(y��ng)�ĵ�Sݔ��֮�g�����t�r�g��b) ��ݔ��S��ë���M�Мy���ͷ�����c) ��ݔ��C��ë���M�Мy���ͷ�����d) ���y�õĕr�ӽY(ji��)���M�з�����

�r����Ϣ���±���ʾ�� a ��һ�����r��9.569ns;

�ڶ������r��9.57ns;

���������r��9.569ns;  �������r�� 9.57ns�� �������r�� 9.57ns��

b

��̎��ݔ��ë�̞�1.531ns,��̎ABC����(y��ng)���ƽ��110��S����(y��ng)��ݔ����(y��ng)��(d��ng)���㣬���dz��F(xi��n)�˶̕���ë�̣��f����̎���������·�ӕr�����F(xi��n)�ĸ���ð�U��r�� C0��ݔ����D��ʾ����δ���F(xi��n)���@��ë�̬F(xi��n)�� - �·������ݔ���cݔ��֮�g���ӕr����(d��o)���·���F(xi��n)����ð�U��r������ͬһ�r�̣�ݔ���cݔ������r������(y��ng)���͕���(d��o)�����O(sh��)Ӌ�Įa(ch��n)Ʒ���F(xi��n)��������(w��n)������r������ͨ�^߉����(sh��)�Ļ�������������ð�U��r��

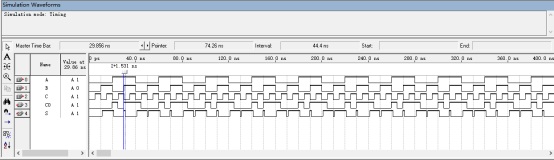

- �� 4 λȫ�������M�Еr����棬�����r�ӷ�����Ҫ�� a) �y�� Cin=��0����B=��0111����A �ġ�0000��?��0001�� ������(y��ng)ݔ�� S3�ĕr�ӣ� b) �y�� Cin=��0����B=��0110����A �ġ�0000��?��0010�� ������(y��ng)ݔ�� S3�ĕr�ӣ� c) �y�� Cin=��0����B=��0100����A �ġ�0000��?��0100�� ������(y��ng)ݔ�� S3�ĕr�ӣ� d) �y�� Cin=��0����B=��0000����A �ġ�0000��?��1000�� ������(y��ng)ݔ�� S3�ĕr�ӣ� e) �y�� Cin=��1����B=��0000����A �ġ�0000��?��0111�� ������(y��ng)ݔ�� S3�ĕr�ӣ� f) �y�� Cin=��0����B=��1111����A �ġ�0000��?��0001�� ������(y��ng)ݔ�� Cout�ĕr�ӣ� g) �y�� Cin=��0����B=��1110����A �ġ�0000��?��0010�� ������(y��ng)ݔ�� Cout�ĕr�ӣ� h) �y�� Cin=��0����B=��1100����A �ġ�0000��?��0100�� ������(y��ng)ݔ�� Cout�ĕr�ӣ� i) �y�� Cin=��0����B=��1000����A �ġ�0000��?��1000�� ������(y��ng)ݔ�� Cout�ĕr�ӣ� j) �y�� Cin=��1����B=��1000����A �ġ�0000��?��0111�� ������(y��ng)ݔ�� Cout�ĕr�ӣ� k) ���y�õĕr�ӽY(ji��)���M�з���

�r�Ӟ�10.785ns; �r�Ӟ�10.354ns; �r�Ӟ�9.491ns; �r�Ӟ�8.8ns; �r�Ӟ�10.526ns; �r�Ӟ�10.526ns; �r�Ӟ�10.008ns; �r�Ӟ�9.146ns; �r�Ӟ�8.628ns; �r�Ӟ�10.354ns;

������Word��ʽ�ęn51�����d��ַ��

��W(xu��)�r�ڵĔ�(sh��)����T���.docx

(365.78 KB, ���d��(sh��): 29)

��W(xu��)�r�ڵĔ�(sh��)����T���.docx

(365.78 KB, ���d��(sh��): 29)

2019-9-15 20:52 �ς�

�c���ļ������d����

���d�e��: �ڎ� -5

|

����TQQ:125739409;���g(sh��)����QQȺ281945664

����TQQ:125739409;���g(sh��)����QQȺ281945664