一、數字集成電路封裝

中、小規模數字IC中最常用的是TTL電路和CMOS電路。TTL器件型號以74(或54)作前綴,稱為74/54系列,如74LS10、74F181、54S86等。中、小規模CMOS數字集成電路主要是4XXX/45XX(X代表0—9的數字)系列,高速CMOS電路HC(74HC系列),與TTL兼容的高速CMOS電路HCT(74HCT系列)。TTL電路與CMOS電路各有優缺點,TTL速度高,CMOS電路功耗小、電源范圍大、抗擾能力強。由于TTL電路在世界范圍內應用極廣,在數字電路教學實驗中,我們主要使用TTL74系列電路作為實驗用器件,采用單一作為供電電源。

數字IC器件有多+5V種封裝形式。為了教學實驗方便,實驗中所用的74系列器件封裝選用雙列直插式。圖1是雙列直插封裝的正面示意圖。雙列直插封裝有以下特點:

圖1 雙列直插式封裝圖 圖2 PLCC封裝圖

1.從正面(上面)看,器件一端有一個半圓的缺口,這是正方向的標志。缺口左邊的引腳為1,引腳號按逆時針方向增加。圖1中的數字表示引腳號。雙列直插封裝IC引腳數有14、16、20、24、28等若干種。

2.雙列直插器件有兩列引腳。引腳之間的間距是2.54毫米。兩列引腳之間的距離有寬(15.24毫米)、窄(7.62毫米)兩種。兩列引腳之間的距離能夠少做改變,引腳間距不能改變。將器件插入實驗臺上的插座中去或者從插座中拔出時要小心,不要將器件引腳搞彎或折斷。

3. 74系列器件一般左下角的最后一個引腳是GND,右上角的引腳是VCC。例如,14引腳器件引腳7是GND,引腳14是VCC;20引腳器件引腳10是GND,引腳20是VCC。但也有一些例外,例如16引腳的雙JK觸發器74LS76,引腳13(不是引腳8)是GND,引腳5(不是引腳16)是VCC。所以使用集成電路器件時要看清它的引腳圖,找對電源和地,避免因接線錯誤造成器件損壞。

二、數字電路測試及故障查找、排除

設計好一個數字電路后,要對其進行測試,以驗證設計是否正確。測試過程中,發現問題要分析原因,找出故障所在,并解決它。數字電路實驗也遵循這些原則。

1.數字電路測試

數字電路測試大體上分為靜態測試和動態測試兩部分。靜態測試指的是,給定數字電路若干組靜態輸入值,測試數字電路的輸出值是否正確。數字電路設計好后,在實驗臺上連接成一個完整的線路。把線路的輸入接電平開關輸出端,線路的輸出接電平指示燈,按功能表或狀態表的要求,改變輸入狀態,觀察輸入和輸出之間的關系是否符合設計要求。靜態測試是檢查設計是否正確,接線是否無誤的重要一步。

在靜態測試基礎上,按設計要求在輸入端加脈沖信號,觀察輸出端波形是否符合設計要求,這是動態測試。有些數字電路只需進行靜態測試即可,有些數字電路則必須進行動態測試。一般地說,時序電路應進行動態測試。

2.數字電路的故障查找和排除

在數字電路實驗中,出現問題是難免的。重要的是分析問題,找出出現問題的原因,從而解決它。一般地說,有四個方面的原因產生問題(故障):器件故障、接線錯誤、設計錯誤和測試方法不正確。在查找故障過程中,首先要熟悉經常發生的典型故障。

(1)器件故障

器件故障是器件失效或器件接插問題引起的故障,表現為器件工作不正常。不言而喻,器件失效肯定會引起工作不正常,這需要更換一個好器件。器件接插問題,如管腳折斷或者器件的某個(或某些)引腳沒插到插座中等,也會使器件工作不正常。對于器件接插錯誤有時不易發現,需仔細檢查。判斷器件失效的方法是用集成電路測試儀測試器件。需要指出的是,一般的集成電路測試儀只能檢測器件的某些靜態特性。對負載能力等靜態特性和上升沿、下降沿、延遲時間等動態特性,一般的集成電路測試儀不能測試。測試器件的這些參數,須使用專門的集成電路測試儀。

(2)接線錯誤

接線錯誤是最常見的錯誤。據有人統計,在教學實驗中,大約百分之七十以上的故障是由接線錯誤引起的。常見的接線錯誤包括忘記接器件的電源和地;連線與插孔接觸不良;連線經多次使用后,有可能外面塑料包皮完好,但內部線斷;連線多接、漏接、錯接;連線過長、過亂造成干擾。接線錯誤造成的現象多種多樣,例如器件的某個功能塊不工作或工作不正常,器件不工作或發熱,電路中一部分工作狀態不穩定等。解決方法大致包括:熟悉所用器件的功能及其引腳號,知道器件每個引腳的功能;器件的電源和地一定要接對、接好;檢查連線和插孔接觸是否良好;檢查連線有無錯接、多接、漏接;檢查連線中有無斷線。最重要的是接線前要畫出接線圖,按圖接線,不要憑記憶隨想隨接;接線要規范、整齊,盡量走直線、短線,以免引起干擾。

(3)設計錯誤

設計錯誤自然會造成與預想的結果不一致。原因是對實驗要求沒有吃透,或者是對所用器件的原理沒有掌握。因此實驗前一定要理解實驗要求,掌握實驗線路原理,精心設計。初始設計完成后一般應對設計進行優化。最后畫好邏輯圖及接線圖。

(4)測試方法不正確

如果不發生前面所述三種錯誤,實驗一般會成功。但有時測試方法不正確也會引起觀測錯誤。例如,一個穩定的波形,如果用示波器觀測,而示波器沒有同步,則造成波形不穩的假象。因此要學會正確使用所用儀器、儀表。在數字電路中,尤其要學會正確使用示波器。在對數字電路測試過程中,由于測試儀器、儀表加到被測電路上后,對被測電路相當與一個負載,因此測試過程中也有可能引起電路本身工作狀態的改變,這點應引起注意。不過,在數字電路實驗中,這種現象很少發生。

當實驗中發現結果與預期不一致時,千萬不要慌亂。應仔細觀測現象,冷靜思考問題所在。首先檢查儀器、儀表的使用是否正確。在正確使用儀器、儀表的前提下,按邏輯圖和接線圖逐級查找問題出現在何處。通常從發現問題的地方,一級一級向前測試,直到找出故障的初始發生位置。在故障的初始位置處,首先檢查連線是否正確。前面已說過,實驗故障絕大部分是由接線錯誤引起的,因此檢查一定要認真、仔細。確認接線無誤后,檢查器件引腳是否全部正確插進插座中,有無引腳折斷、彎曲、錯插問題。確認無上述問題后,取下器件測試,以檢查器件好壞、或者直接換一個好器件。如果器件和接線都正確,則需考慮設計問題。

實驗一 常用集成門電路邏輯功能測試及其應用

實驗目的:

1、掌握集成門電路的邏輯功能、邏輯符號和邏輯表達式;

2、了解邏輯電平開關和邏輯電平顯示的工作原理;

3、學會驗證集成門電路的邏輯功能;

4、掌握集成門電路邏輯功能的轉換;

5、學會連接簡單的組合邏輯電路。

二、實驗原理:

1、功能測試

(1).TTL集成門電路的工作電壓:+5V

(2).TTL集成門引腳識別方法:從正面(上面)看,器件一端有一個半圓的缺口,這是正方向的標志。缺口左邊的引腳為1,引腳號按逆時針方向增加。

(3).TTL集成門電路管腳識別示意圖及各個引腳的功能 (74LS00、74LS04、74LS08、74LS32)

圖1 雙列直插式封裝圖 圖2 PLCC封裝圖

74系列器件一般左下角的最后一個引腳是GND,右上角的引腳是VCC。例如,14引腳器件引腳7是GND,引腳14是VCC;20引腳器件引腳10是GND,引腳20是VCC。但也有一些例外,例如16引腳的雙JK觸發器74LS76,引腳13(不是引腳8)是GND,引腳5(不是引腳16)是VCC。所以使用集成電路器件時要看清它的引腳圖,找對電源和地,避免因接線錯誤造成器件損壞。

2、功能應用

(1).常用門電路的邏輯表達式:

與門:Y=AB 或門:Y=A+B 非門:Y=A▔

(2).邏輯代數基本定理:

1:0 ?0=0 ?1=0 1 ?1=1 0+0=0 0+1=1+0=1+1=1 1▔=0 0▔=1

0-1率:A+0=0 A+1=1 A?0=0?A=0 A?1=1

互補率:A+A▔=1 A ?A▔=0 重疊率:A+A=A A ?A=A

還原率:A▔▔=A 交換律:A+B=B+A A ?B=B ?A

結合律:A+(B+C)=(A+B)+C=(A+C)=B A ?(B ?C)=(A ?B) ?C=(A ?C) ?B

分配率:A ?(B+C)=A ?B=A ?C A+B ?C=(A+B) ?(A+C)

吸收率:A+AB=A A(A+B)=A A+A▔B=A+B A(A▔+B)=AB

反演率:(A+B)▔=A▔?B▔ (A?B) ▔= A▔+B▔

包含率:AB+A▔C+BC=AB+A▔C (A+B)(A▔+C)(B+C)=(A+B)(A▔+C)

(3)、簡單組合邏輯電路的連接注意事項:

簡單組合邏輯電路的連接注意事項:熟悉所用器件的功能及其引腳號,知道器件每個引腳的功能;器件的電源和地一定要接對、 接好;檢查連線和插孔接觸是否良好;檢查連線有無錯接、多接、漏接; 檢查連線中有無斷線。最重要的是接線前要畫出接線圖,按圖接線, 不要憑記憶隨想隨接;接線要規范、整齊,盡量走直線、短線, 以免引起干擾。

三、實驗儀器設備及器材:

集成塊:74LS00、74LS04、74LS08、74LS32、

四、實驗內容與步驟:

(一)功能測試

1、集成門電路邏輯功能測試:

(1)、集成門的邏輯功能測試

a|、電路圖:

b、測試結果:

0.png (20.02 KB, 下載次數: 153)

下載附件

2019-4-24 15:19 上傳

0.png (7.53 KB, 下載次數: 158)

下載附件

2019-4-24 15:20 上傳

(二)功能應用

1.用與非門實現非門;

電路圖:

| | |

| | |  =A+B |

| | |

| | |

| | |

2.用非門和與非門實現或門;

電路圖:

3.用與非門和與非門實現或門;

電路圖:

4.用非門和與門實現同或門;

電路圖:

| | |

| | | |

Y=  |

| | | |

| | | |

| | | |

| | | |

| | | |

| | | |

| | | |

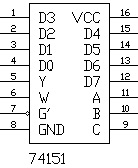

5.用74LS00和74LS08實現邏輯函數表達式:Y=

。

電路圖:

五、實驗總結和體會:

1、做實驗時一定要看清實驗要求,按步驟做,一定要仔細。

2、這次實驗讓我知道了各類芯片的組成與原理,知道了與門、或門、非門之間的相互作用。

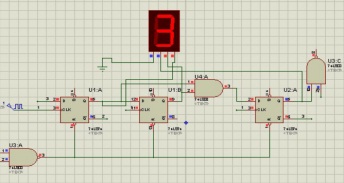

3、仿真時可以不用連線直接編號,讓電路圖看起來整潔而且方便。

實驗二 組合邏輯電路功能分析與設計

1、了解組合邏輯電路的特點;

2、掌握組合邏輯電路功能的分析方法;

3、學會組合邏輯電路的連接方法;

4、掌握組合邏輯電路的設計方法。

二、實驗原理:

1、組合邏輯電路的特點:

任意時刻的輸出僅僅取決于該時刻的輸入,與電路原來的狀態無關,電路無記憶功能。

2、組合邏輯電路的分析方法:

1. 根據給定的組合邏輯電路,逐級寫出邏輯函數表達式;

2. 化簡得到最簡表達式;

3. 列出電路的真值表;

4. 確定電路能完成的邏輯功能

3、組合邏輯電路的設計步驟:

1.仔細分析設計要求,確定輸入、輸出變量。

2.對輸入和輸出變量賦予0、1值,并根據輸入輸出之間的因果關系,列出輸入輸出對應關系表,即真值表。

3.根據真值表填卡諾圖,寫輸出邏輯函數表達式的適當形式。

4.畫出邏輯電路圖。

三、實驗器件

集成塊:74LS00、74LS04、74LS08、74LS32

四、實驗內容:

(一)、組合邏輯電路功能分析

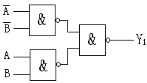

分析圖4-1所示電路的邏輯功能:

分析圖4-1所示電路的邏輯功能:

1.根據電路圖得出表達式

2.真值表如下

2.真值表如下

3.由上可得:此電路的邏輯功能相當于同或門,即“輸入相同出1,輸入不同出0”

(二)、組合邏輯電路設計(根據組合邏輯電路的設計步驟,分別寫出各個組合邏輯電路的設計步驟。)

1、設計一個舉重裁判表決器。設舉重比賽有三個裁判,一個主裁判和兩個副裁判。杠鈴完全舉上的裁決由每一個裁判按一下自己面前的按鈕來確定。只有當兩個或兩個以上裁判(其中必須有主裁判)判明成功時,表示“成功”的燈才亮。(要求用與非門實現)

解:設三個裁判分別為A、B、C,Y表示輸出,成功,1表示成功,0表示失敗。

2、某設備有開關A、B、C,要求僅在開關A接通的條件下,開關B才能接通;開關C僅在開關B接通的條件下才能接通。違反這一規程,則發出報警信號。設計一個由與非門組成的能實現這一功能的報警控制電路。(要求用與非門實現)

解:設開關接通為1,未接通為0;輸出信號為Y,報警為1 ,不報警為0。

3、設計全減器,(要求用與非門實現)

解:1.分析如下:可用集成譯碼器74LS138和與非門實現

2.真值表如下:其中Ai和Bi表示二進制數的第i位,Ci表示本位最終運算結果,即就是低位向本位借位或本位向高位借位之后的最終結果,Di-1表示低位是否向本位借位,Di表示本位是否向高位借位。

五、實驗總結與體會:

1、了解了全加器和全減器的原理。

2、更了解了邏輯電路的功能。

實驗三 編碼器、譯碼器及應用電路設計

一、實驗目的:

- 掌握中規模集成編碼器、譯碼器的邏輯功能測試和使用方法;

- 學會編碼器、譯碼器應用電路設計的方法;

- 熟悉譯碼顯示電路的工作原理。

二、實驗原理:

1、什么是編碼:

用文字、符號、或者數字表示特定對象的過程稱為編碼

2、編碼器74LS147的特點及引腳排列圖:

譯碼是編碼的逆過程,把給定的代碼進行“翻譯”,變成相應的狀態,使輸出通道中相應的一路有信號輸出。

譯碼器按照功能的不同,一般分為三類:

二進制譯碼器、二—十進制譯碼器、顯示譯碼器。

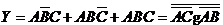

74LS138的特點及其引腳排列圖:

74LS138的特點及其引腳排列圖:

74LS138的特點反碼輸出,

ABC:地址輸入端,

Y0—Y7:輸出端,

G1、G2A’、G2B’:使能端,只有當G1=G2A’

=G2B’=1時,譯碼器才工作。

譯碼器74LS42的特點及其引腳排列

譯碼器74LS42的特點及其引腳排列

譯碼器74LS42的特點是能將8421BCD碼譯成10個對象,

它有四個輸入端,十個輸出端。

(3)數碼顯示與七段譯碼驅動器:

a、七段發光二極管數碼顯示管的特點:(共陰極)

b、七段譯碼驅動器:

此類譯碼器型號由74LS247(共陽)、74LS248(共陰)、CC4511(共陰)等,本實驗采用CC4511BCD碼來驅動共陰數碼管。圖6-5為CC4511引腳圖:

4、在本數字電路實驗裝置上已完成了譯碼器74LS48和數碼管之間的連接圖。

三、實驗器件:集成塊:74LS147 74LS138 74LS42

四、實驗內容與步驟:

- 74LS147編碼器邏輯功能測試:

- 將編碼器9個輸入端各接一根導線,來改變輸入端的狀態,4個輸入端依次從高到低Q3-Q0顯示,在各輸入端輸入有效電平,觀察并記錄電路輸入與輸出的對應關系,以及當幾個輸入同時為有效電平編碼器的優先級別關系。

2、274LS138 譯碼器邏輯功能測試:

將譯碼器的使能端

輸入端、

分別接到邏輯電平開關上,八個輸出端

依次連接在邏輯電平顯示上,改變輸入端的狀態組合,觀察輸出端的變化,并將實驗結果記錄下表:

3、74LS47譯碼器邏輯功能測試:

4、編碼器、譯碼器和顯示器三者之間的聯接:

5、用兩片74LS138組合成一個4-16線的譯碼器,并進行實驗。

五、實驗報告結果進行分析、討論。

1.了解譯碼,編碼的概念;譯碼和編碼互為逆過程;

2.74LS147是優先編碼器,當輸入端有兩個或兩個以上為低電平,它將對優先級別相對較高的優先編碼;

3.74LS138: Y0 -Y7 是輸出端,G1、G2A’、G2B' 為使能端,只有當G1=G2A’=G2B’=1時,譯碼器才工作

4了解共陰、共陽和數碼管的接法;

實驗四用譯碼器實現組合邏輯電路

一、實驗目的:學會用譯碼器實現組合邏輯電路

二、實驗原理:

用譯碼器加上門電路的方法,來實現較復雜的組合邏輯電路,簡單方便。本實驗主要使用的譯碼器是74LS138。對門電路的選擇以與非門居多。

72LS138譯碼器的功能特點:

1.譯碼器的工作條件:只有當使能端G1=G2A’=G2B’=1時,譯碼器才工作。

2、譯碼器實現函數所用門電路的特點:

三、實驗儀器及器材:

集成塊:74LS138 74LS42 74LS20 74LS08

四、實驗內容與步驟:(要求寫出各電路的設計步驟,并畫出實驗電路圖。)

1、設計一個三變量,判斷奇數個“1”的電路(要求用譯碼器和與非門實現)。

解:設三個輸入變量分別為A、B、C,輸出變量為Y,輸入有奇數個1輸出1,否則輸出0

2、某工廠有A、B、C三臺設備,A、B的功率均為10W,C的功率為20W,這些設備由和兩臺發電機供電,兩臺發電機的最大輸出功率分別為10W和30W,要求設計一個邏輯電路以最節約能源的方式啟、停發電機,來控制三臺設備的運轉、停止(要求用譯碼器和與非門、與門實現)。

解:設三個輸入變量分別為A、B、C,輸出變量為D、E

1.真值表如下

3、設計一個全加器(要求用譯碼器和與非門實現)。

解:1.真值表如下

2.邏輯電路如下所示

五、實驗體會:通過與“實驗三”實現組合邏輯電路的方法的比較,寫出使用自己的體會。

譯碼是編碼的逆過程。它的功能是將具有特定含義的二進制碼轉換成對應的輸出信號

1

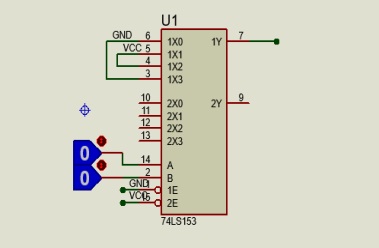

實驗五 數據選擇器邏輯功能測試及應用

1、掌握集成數據選擇器的邏輯功能及使用方法;

2、學會用數據選擇器實現組合邏輯電路的方法。

二、實驗原理:

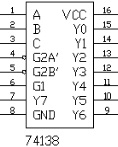

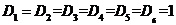

數據選擇器的芯片種類很多,常用的2選1、4選1、8選1、16選1、32選1等。本實驗使用的是8選1 數據選擇器74LS151。

用數據選擇器實現邏 輯函數表達式有兩種常用的方法:

數據選擇器又叫“多路開關”。 數據選擇器在地址控制端(或叫選擇控制)的控制下,從多個數據輸入通道中選擇其中一通道的數據傳輸至輸出端。

工作條件:

工作條件:

:接低電平 Y:輸出端

:接低電平 Y:輸出端

A、B、C:地址輸入端

D0-D7:輔助輸入端

W:擴展端

圖5—1數據選擇器74LS151引腳排列

三、實驗儀器及器材:

實驗儀器設備:D2H+型數字電路實驗箱

集成塊:74LS151 74LS153 74LS04

四、實驗內容與步驟:(寫出用數據選擇器實現邏輯函數設計過程、畫出接線圖)

1、測試數據選擇器74LS151的邏輯功能:

2、用數據選擇器74LS151實現邏輯函數:

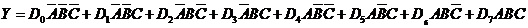

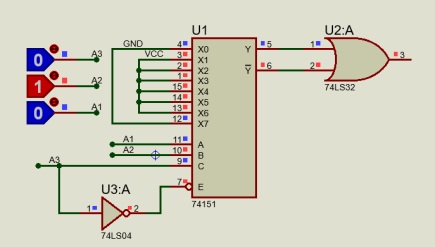

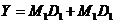

解:74LS151的表達式為

因為

所以有:

電路圖如下所示

- 用數據選擇器74LS153實現邏輯函數:

解:

故:D0=D3=0,D1=D2=1

五、實驗收獲、體會:

數據選擇是指經過選擇,把多路數據的某一路數據傳送到公共數據線上,實現數據選擇功能的邏輯電路。它的作用相當于多個輸入的單刀多擲開關。

實驗六 觸發器邏輯功能測試及應用

一、實驗目的:

1、掌握基本RS、JK、D、T和T′觸發器的邏輯功能;

2、學會驗證集成觸發器的邏輯功能及使用方法;

3、熟悉觸發器之間相互轉換的方法。

二、實驗原理:

觸發器:根據觸發器的邏輯功能的不同,又可分為:

三、實驗儀器與器件:

實驗儀器設備:D2H+型數字電路實驗箱。

集成塊:74LS112 74LS74 74LS04 74LS08 74LS02 74LS86

四、實驗內容與步驟:

1、基本RS觸發器邏輯功能的測試:

(約束條件)

狀態圖為:

電路圖為:

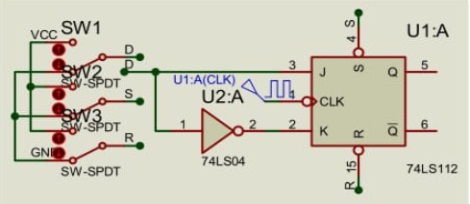

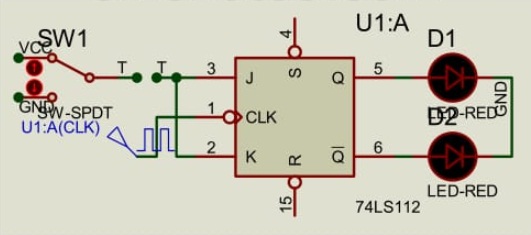

2、JK觸發器邏輯功能測試:

狀態圖為:

電路圖為:

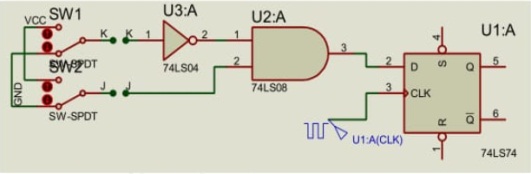

3、D觸發器邏輯功能測試:

(1)異步輸入端 功能測試:

功能測試:

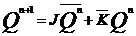

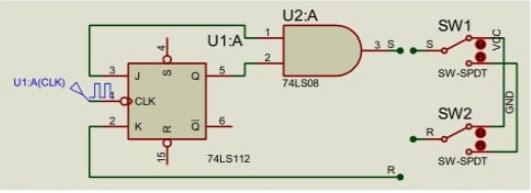

4、不同類型時鐘觸發器間的轉換:

JK轉換為D觸發器:D轉換為JK 觸發器:

D轉換為JK 觸發器:

JK轉換為T觸發器:T轉換為JK觸發器:

JK轉換為RS觸發器:RS轉換為JK觸發器:

五、實驗體會與要求:

1、根據實驗結果,寫出各個觸發器的真值表。

2、試比較各個觸發器有何不同?

3、寫出不同類型時鐘觸發器間的轉換過程。

實驗七 時序邏輯電路的測試

1、熟悉時序邏輯電路的分析方法。

2、掌握時序邏輯電路的測試方法。

二、實驗原理:

簡述時序邏輯電路的分析方法:

根據時序邏輯電路分析步驟,得出電路的邏輯功能,進行測試。在時鐘信號輸入端加入合適的脈沖信號,然后觀察各單元部件之間的配合是否滿足要求,將實驗現象和理論分析結果進行比較。

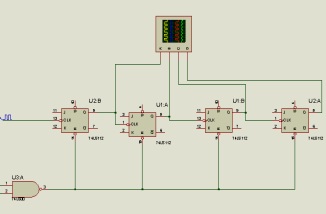

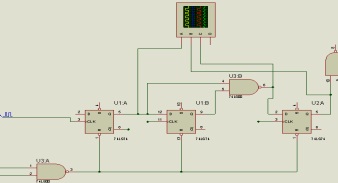

例如,圖10—2是4位二進制異步加法計數器的測試,

圖10—1 實驗電路圖 圖10—2 實驗電路圖 圖10—3 實驗電路圖

可以采用以下幾種方法:

(1)用示波器觀察波形。在計數器的CP端加入時鐘脈沖信號,然后用示波器分別測試脈沖信號CP的波形及計數器的輸出端Q3、Q2、Q1、Q0的波形。

(2)用數碼管顯示。 在計數器的CP端加入時鐘脈沖信號,將計數器的輸出端接至字符顯示譯碼器,由數碼管可以顯示出計數器CP端輸入脈沖的個數。

(3)用0—1顯示器顯示二進制數。在計數器的CP端加入時鐘脈沖信號,然后用0—1顯示器觀察計數器的輸出端Q3、Q2、Q1、Q0狀態的變化。

三、實驗儀器及器材:

實驗儀器設備:DGJ—2型電工技術實驗裝置 (D71—2數電實驗掛箱)

集成塊:74LS112 74LS74 74LS00

四、實驗內容與步驟:

(1)根據圖10—1連接電路,然后分別用“實驗原理”介紹的方法對該電路進行測試,并畫出電路的工作波形、狀態表,描述電路的邏輯功能。

(2)根據圖10—2連接電路,然后分別用“實驗原理”介紹的方法對該電路進行測試,并畫出電路的工作波形、狀態表,描述電路的邏輯功能。

(3)根據圖10—3連接電路,然后分別用“實驗原理”介紹的方法對該電路進行測試,并畫出電路的工作波形、狀態表,描述電路的邏輯功能。

五、實驗報告要求

1、分析實驗中各個電路的工作波形、狀態表,弄清各個實驗電路的邏輯功能及工作特點。

2、分別畫出各個電路的狀態轉換圖和時序圖。

六、寫出實驗體會

實驗八 移位寄存器邏輯功能測試及應用

1、掌握中規模4位雙向移位寄存器邏輯功能及使用方法;

2、熟悉移位寄存器的應用——構成環形計數器和實現數據的串行、并行轉換。

二、實驗原理:

移位寄存器是一個具有移位功能的寄存器,是指寄存器中所存的代碼能夠在移位脈沖的作用下依次左移或右移。既能左移又能右移的稱為雙向移位寄存器,只需要改變左、右移的控制信號便可實現雙向移位要求。本實驗選用的4位雙向移位寄存器,型號為74LS194,其引腳排列如圖11—1所示。

移位寄存器不僅可以組成串行—并行數碼轉換器,還可以方便地組成移位寄存器型計數器、脈沖分配器等電路。常用的移位寄存器有環行計數器和扭環型計數器。

圖11—1 74LS194引腳排列及功能

三、實驗儀器及器材:

實驗儀器設備:DGJ—2型電工技術實驗裝置 (D71—2數電實驗掛箱)

集成塊:74LS194 74LS04

四、實驗內容與步驟:

1、驗證移位寄存器74LS194的邏輯功能:

計數脈沖由單次脈沖源提供,清零端 、工作狀態控制端M1 M2、并行數據輸入端D0—D3、DSL為左移串行數據輸入端、DSR右移串行數據輸入端分別接邏輯電平開關,輸出端Q0—Q3均接邏輯電平顯示。按如下逐項測試并判斷該集成塊的功能是否正常。

、工作狀態控制端M1 M2、并行數據輸入端D0—D3、DSL為左移串行數據輸入端、DSR右移串行數據輸入端分別接邏輯電平開關,輸出端Q0—Q3均接邏輯電平顯示。按如下逐項測試并判斷該集成塊的功能是否正常。

(1)異步清零功能:當 =0時,這時Q3Q2Q1Q0=0000,雙向移位寄存器清零。其它輸入信號都不起作用,與CP無關,故稱為異步清零。

=0時,這時Q3Q2Q1Q0=0000,雙向移位寄存器清零。其它輸入信號都不起作用,與CP無關,故稱為異步清零。

(2)保持功能:當 =1,且CP=0或M1 =M2=0時,雙向移位寄存器保持狀態不變。

=1,且CP=0或M1 =M2=0時,雙向移位寄存器保持狀態不變。

(3) 同步并行送數功能:當 =1,M1 =M2=1時,在CP上升沿操作下,并行輸入數據d3 d2 d1 d0送入寄存器。

=1,M1 =M2=1時,在CP上升沿操作下,并行輸入數據d3 d2 d1 d0送入寄存器。

(4)右移串行送數功能:當 =1,M1 =0、M2=1時,在CP上升沿操作下,可依次把加在

=1,M1 =0、M2=1時,在CP上升沿操作下,可依次把加在 端的數據從時鐘觸發器 行送入寄存器中。

端的數據從時鐘觸發器 行送入寄存器中。

(5)左移串行送數功能:當 =1,M1 =1、M2=0時,在CP上升沿操作下,可依次把加在DSL端的數據從時鐘觸發器串行送入寄存器中。

=1,M1 =1、M2=0時,在CP上升沿操作下,可依次把加在DSL端的數據從時鐘觸發器串行送入寄存器中。

2、用74LS194構成環行計數器,畫出實驗電路圖及其狀態圖,并陳述電路功能。

- 用74LS194構成扭環行計數器,畫出實驗電路圖及其狀態圖,并陳述電路功能。

狀態圖為:

1000 ←0000← 0001 ←0011

↓ ↑

1100→ 1110 →1111 →0111

1001 ← 0100 ←1010 ←1101

↑ ↓

0010 ←0101← 1011 ←0110

五、實驗報告要求

整理實驗數據,總結本次實驗的收獲與體會。

只要將寄存器最高位的輸出接至最低位的輸入,或將最低位的輸出接至最高位的輸入,就可以實現環形移位寄存器。

實驗九 算術運算電路設計

一、實驗目的:

- 掌握中規模集成加法器的邏輯功能和使用方法;

- 學會使用二進制中規模集成加法器設計十進制加法運算電路;

- 使用全加器電路實現全減器運算。

二、實驗原理:

1、中規模集成加法器74X83的邏輯功能;

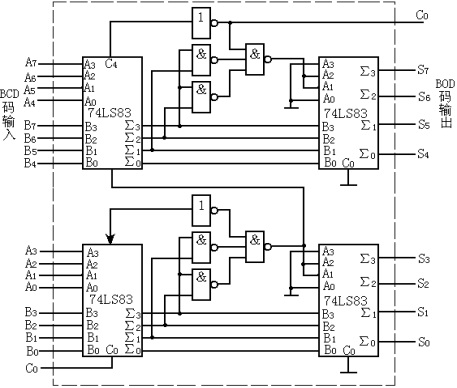

2、一位BCD碼相加的電路如圖1所示

二位二進制BCD碼數字相加參考電路圖如圖2所示

。

三、實驗內容

1、設計兩位BCD碼相加,和為BCD碼輸出的算術運算電路

2、設計輸出為原碼的4位減法運算邏輯圖

設計提示:

若n位二進制的原碼為N原,則與它相對應的2 的補碼為

補碼與反碼的關系式

設兩個數A、B相減,利用以上兩式可得:

因此,在實際應用中,通常是將減法運算變為加法運算來處理,即采用加補碼的方法完成減法運算。

參考電路如圖3

四、你的設計過程:(包括分析過程,推到過程,器件功能與選擇等)

1、全加器

兩位8421BCD碼相加,個位如果不需要進位則為其結果,個位如果需要進位則將個位的進位輸入到十位即完成。電路圖如下所示:

完整的Word格式文檔51黑下載地址:

數字電路基礎實驗.doc

(2.13 MB, 下載次數: 21)

數字電路基礎實驗.doc

(2.13 MB, 下載次數: 21)

2019-4-24 08:10 上傳

點擊文件名下載附件

下載積分: 黑幣 -5