含有文檔,PCB板,quartus程序。需要pcb程序請私聊。

目 錄

1 緒論 1

1.1 課題研究的背景 1

1.2 國內外研究現(xiàn)狀 1

1.3 超聲波的特性 2

2 FPGA介紹 2

2.1 FPGA對于設計的必要性 3

2.2 可編程邏輯器件 4

2.3 FPGA的結構 4

3 基于FPGA測距系統(tǒng)硬件結構平臺 5

3.1 FPGA核心板結構 5

3.2 超聲波測距傳感器 7

4 超聲波測距系統(tǒng)程序設計及仿真 9

4.1 程序流程圖 9

4.2 程序及仿真 10

4.3 頂層原理圖 18

結論 19

致謝 20

參考文獻 21

附錄 22

1 緒論 1.1 課題研究的背景 科技飛速發(fā)展時至今日,超聲波測距廣泛應用于工業(yè),農(nóng)業(yè),交通,環(huán)境,安全防護能源測量等科學領域,超聲波測距的測量精度、測量距離,可靠性等性能指標對于提高相關應用系統(tǒng)的測控精度、可靠性,提高生產(chǎn)效率、促進科學技術的發(fā)展都具有極為重要的作用。隨著經(jīng)濟的迅速發(fā)展,交通系統(tǒng)日益龐大,交通安全問題越來越被重視,安全防護現(xiàn)在變成為一個重要議題。近幾年,船舶運輸事故頻發(fā),復雜的水運環(huán)境,如大雨、大霧或夜間行駛常常導致航道的能見度降低,造成碰撞事故。由于超聲波測距技術具有在黑暗、灰塵、煙霧等惡劣的環(huán)境下正常工作的特性,將超聲波測距引入航運系統(tǒng)能切實可行的緩解這一問題。 超聲波測距系統(tǒng)的設計結構多種多樣,性能差異也各異。目前市面上主流的超聲波測距系統(tǒng)大多是以8位或者16位單片機為主空芯片,產(chǎn)生驅動信號,并負責接收處理回波,控制現(xiàn)實通訊。這樣處理成本固然降低了,但是測量精度,和測量距離,以及時序的控制能力有限。 超聲波測距的核心在于超聲波信號的收發(fā)部分,傳統(tǒng)單片機內部指令運行時存在較大延時誤差其精度無法滿足精密測量的要求,本設計將FPGA(現(xiàn)場可編程門陣列)引入超聲波測距系統(tǒng)的設計內,利用其較高的運行速度和豐富的片內資源,取代單片機,提高對超聲波工作頻率的控制精度以及對超聲波收發(fā)渡越時間的測量精度。 1.2國內外研究現(xiàn)狀 超聲波測距被大量應用于各種工業(yè)領域,諸如工業(yè)自動控制,建筑工程測量和機器人視覺識別等方面。和其他方法相比,比如激光測距、微波測距等,由于聲波在空氣中傳播速度遠遠小于光線和無線電波的傳播速度,對于時間側量精度 的要求遠小于激光測距、微波測距等系統(tǒng),因而超聲波測距系統(tǒng)電路易實現(xiàn)、結構簡單和造價低,且超聲波在傳播過程中不受煙霧、空氣能見度等因素的影響,在各種場合均得到廣泛應用。 超聲波測距作為一種典型的非接觸測量方法,在很多場合得以應用。然而超聲波測距在實際應用也有很多局限性。 超聲波在空氣中衰減極大,由于測量距離的不同,造成回波信號的起伏變化,不同幅度回波信號在通過固定門限比較器的整形過程中,回波到達時間的測t產(chǎn)生較大的誤差,另外就是構成超聲波傳感器的壓電陶瓷片在壓電的雙向轉換過程中,存在慣性、滯后等現(xiàn)象,以及超聲波脈沖在空氣中傳播本身及多重的反射路徑,均導致回波信號被展寬,也使測量產(chǎn)生較大的誤差,影響了測距的分辨率。其他還有一些因素,諸如環(huán)境溫度,風速等也會對測量造成一定的影響。 目前國內外對超聲波測距的研究主要集中在提高測距精度方面。由于超聲波測距其測量范圍與測量精度是相互矛盾的。要想得到較大的測量范圍,需降低超聲波的頻率,而此時波長增大,測量精度則會降低;要想提高測量精度,需使用高頻的超聲波,其在空氣中衰減很快,測量范圍則會縮小。 超聲波測距的精度主要取決于所測超聲波傳輸時間的測量精度和超聲波在介質中的傳輸速度這兩方面。國外在提高超聲波測距性能方面做了大量研究,國內相關學者也做了相關研究。提高傳輸時問的測量精度主要通過提高測距儀器的計時精度來實現(xiàn)。而對于超聲波的傳輸速度的提高,主要通過采用高頻的超聲波換能器實現(xiàn)。高頻的超聲波換能器的工作中心頻率,一般是幾到十幾MHz,由于換能器的工作頻率很高,超聲波衰減非常明顯,這就對測距儀器的驅動信號的 驅動效率提出了更高要求,如何使驅動信號的中心頻率精度提高成為了一個派生研究方向。 1.3超聲波的特性 當物體振動時會發(fā)出聲音。科學家們將每秒鐘振動的次數(shù)稱為聲音的頻率,它的單位是赫茲。我們人類耳朵能聽到的聲波頻率為20~20000赫茲。當聲波的振動頻率大于20000赫茲或小于20赫茲時,我們便聽不見了。因此,我們把頻率高于20000赫茲的聲波稱為“超聲波”。 超聲和可聞聲本質上是一致的,它們的共同點都是一種機械振動,通常以縱波的方式在彈性介質內會傳播,是一種能量的傳播形式,其不同點是超聲頻率高,波長短。 超聲波是一種在彈性介質中的機械振蕩,傳播速度僅為光波的百萬分之一,縱向分辨率較高。超聲波對色彩、光照度、外界光線和電磁場不敏感,對于被測物處于黑暗、有灰塵或煙霧、強電磁干擾、有毒等惡劣的環(huán)境下超聲波有很強的適應能力。 由于超聲波的能量消耗緩慢,在介質中傳播的距離較遠,聲波傳播速度在相當大范圍內與頻率無關等獨特優(yōu)點,超聲波被視為測距技術的一種良好選擇在軍事,工業(yè),交通上有很多的應用。 2FPGA介紹 2.1 FPGA對于設計的必要性 在這里我們比較一下單片機與FPGA的性能特點: 單片機:可采用C語言編程,靈活多變,可以方便的實現(xiàn)復雜的指令控制。但是對時序控制實現(xiàn)能力較弱,組合邏輯能力較弱,程序執(zhí)行采用順序執(zhí)行方式,外部自由使用I/O口數(shù)量有限,對于接口信號的頻率控制能力較弱,運行速率約為幾十兆赫茲,采用外部晶振的頻率不能超過40MHz。 FPGA:采用硬件語言編程,沒有指令控制系統(tǒng),控制能力較弱。但具有很強的時序控制能力和邏輯組合能力,對于通信接口特別是高速接口可以將不同速率不同協(xié)議的耦合和橋接。運行速率約為幾百兆赫茲,采用外部晶振的頻率可超過100MHz。 整個系統(tǒng)的核心部分是超聲波的收發(fā)控制端和信號處理部分,正是出于這種考慮現(xiàn)在主流的設計是采用單片機做為主控芯片負責產(chǎn)生超聲波驅動信號并對回波進行數(shù)據(jù)處理,控制現(xiàn)實輸出。 決定超聲波驅動信號的效果,同時對于回波信號的處理,和整個超聲波測距總計時,超聲波周期的精確時間是一個重要的參數(shù)。對于驅動信號頻率的嚴格控制,總計時的時間控制,是系統(tǒng)高性能保障重要條件。 現(xiàn)在主流的設計是采用單片機的中斷加定時計數(shù)器來處理,為方便計算定時器初值,采用12MHz晶振來計算,無論是采用是采用哪種位定時器/計數(shù)器方式,驅動信號的頻率精度都有限,與理論精度相差較大,隨著進入中斷之前執(zhí)行任務的不同,定時器的計時值存在著多達3us以上的不確定誤差;若采用定時器的對外部正脈沖自動計時的功能,將待測信號接入外部中斷引腳,自動實現(xiàn)信號寬度的測量,該方案的計時精度也只能達到lus。而且計時的精度受制于單片機的運行速度,可提高空間很小;若采用TTL分立元件(如8253/8254)來實現(xiàn)計數(shù)器電路,這樣計時的精度會有所提高,但計時頻率可提高空間不大,如8254最高計時頻率不超過10MHz。同時設計由于采用分立元件,體積也很大。 對回波到達時間的測量,對回波信號的辨識和綜合處理也是系統(tǒng)設計的關鍵任務。實際上超聲波換能器由于余震自身存在1到2us的不確定誤差,若計時器自身的計時誤差也是us級的,那么綜合起來之后,誤差又將增大。本設計中采用FPGA技術,利用其強大的時序處理能力,極高的運行速度(100MHz以上),同時,其豐富的內部資源又可以將前述的各種邏輯功能集中在一塊芯片內部實現(xiàn),體積也很小,F(xiàn)PGA(Field Programmable Gate Array)是可編程邏輯器件的一種。可編程邏輯器件是大規(guī)模集成電路技術發(fā)展的產(chǎn)物,是一種半定制的集成電路,結合計算機軟件技術可以快速、方便地構建數(shù)字系統(tǒng)。以下簡要介紹可編程邏輯器件及FPGA的發(fā)展、結構和功能特點。 2.2 可編程邏輯器件 隨著微電子設計技術與工藝的發(fā)展,數(shù)字集成電路從電子管、晶體管、中小規(guī)模集成電路、超大規(guī)模集成電路(VLSIC)逐步發(fā)展到今天的專用集成電路(ASIC)。ASIC的出現(xiàn)降低了產(chǎn)品的成本,提高了系統(tǒng)的可靠性,縮小了設計科的物理尺寸,推動了社會的數(shù)字化進程。但是ASIC因其設計周期長,改版投資大,靈活性差等缺陷制約著它的應用范圍。硬件工程師希望有一種更靈活的設計方法,根據(jù)需要,在實驗室就能設計、更改大規(guī)模數(shù)字邏輯,研制自己的ASIC并馬上投入使用,這是提出可編程邏輯器件的基本思想。 可編程邏輯器件隨著微電子制造工藝的發(fā)展取得了長足的進步。從早期的只能存儲少量數(shù)據(jù),完成簡單邏輯功能的可編程只讀存儲器(PROM)、紫外線可擦除只讀存儲器(EPROM)和電可擦除只讀存儲器,發(fā)展到成為可以完成超大規(guī)模的復雜組合邏輯與時序邏輯的可編程邏輯器件(CPLD)和現(xiàn)場可編程邏輯門陣列(FPGA)。隨著工藝技術的發(fā)展與市場的需要,超大規(guī)模、高速、低功耗的新型FPGA/CPLD不斷推陳出新。新一代的FPGA甚至集成了中央處理器(CPU) 或數(shù)字處理器(DSP)內核,在一片F(xiàn)PGA上進行軟硬件協(xié)同設計,為實現(xiàn)片上可編程系統(tǒng)(SOPC,System On Programmable Chip)提供了強大的硬件支持。 2.3 FPGA的結構 FPGA生產(chǎn)廠家有Altera、Xilinx、Actel、Lattice等四家公司,其中Altera 和Xilinx主要生產(chǎn)一般用途FPGA,其主要產(chǎn)品采用RAM工藝。Actel主要提供非易失性FPGA,產(chǎn)品主要基于反熔絲工藝和FLASH工藝。其中Altera公司一直都處于可編程芯片系統(tǒng)(SOPC)領域的前沿和領袖地位,為業(yè)界提供最先進的可編程器件和相關軟件工具、IP軟件模塊以及優(yōu)秀的設計方案。其主流FPGA系列包括FLEX6000、FLEXl0K、ACEX、Cyclone、CyclonelI、APEX20K、APEXII、Stratix、Mercury、Exclibur等。 簡化的FPGA基本由6部分組成,分別為可編程輸入/輸出單元,基本可編程邏輯單元,嵌入式RAM,豐富的布線資源,底層嵌入功能單元和內嵌專用硬核等,如圖:

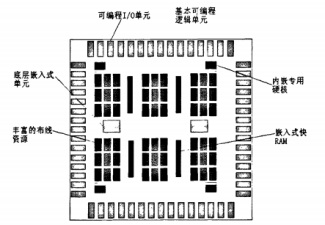

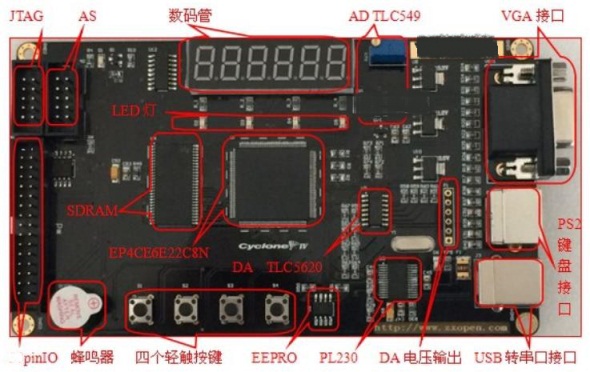

圖2.1 FPGA的內部邏輯結構 3 基于FPGA測距系統(tǒng)硬件結構平臺 3.1 FPGA核心板結構 該設計采用FPGA開發(fā)板,該開發(fā)板集成了多種功能,比如說像VGA接口、PS2 鍵盤接口、138譯碼的數(shù)碼管、32pin外接口I/O、間距為2.54mm的外接插件、jtag調試接口、AS下載接口、DA數(shù)模轉換芯片TLC5620、USB轉串口接口、蜂鳴器、四個輕觸按鍵。開發(fā)板的具體結構如下圖所示:

圖3.1 FPGA 開發(fā)板結構 從設計方面考慮要用到的部分是外接口I/O、138譯碼的數(shù)碼管、jtag調試接口、AS下載端口、蜂鳴器等。在最初的設計思路中運用到了LED燈,輕觸按鍵這些功能。運用這些功能的目的是對FPGA開發(fā)板進行一個初步的學習,從而實現(xiàn)一些簡單的功能,進而向較難的功能邁出一小步。 該FPGA開發(fā)板所用的核心芯片為ALTERA公司的cyclone IV E系列芯片,具體型號為EP4CE6E22C8N。cyclone IV E系列的芯片通過了最低的成本實現(xiàn)了較高的功能,并且cyclone IV E系列的器件上邊集成很多低成本的收發(fā)器。在不影響其整體功能的前提下,節(jié)省了很多成本。Cyclone IV E 系列在很多領域諸如像無線、通訊等都有著一些很有價值的應用。 cyclone IV E 器件系列具有以下特性: (1)6k到150k的邏輯單元。 (2)高達6.3Mb的嵌入式存儲器。 (3)高達360個18*18乘法器,實現(xiàn)DSP處理密集型的應用。 (4)協(xié)議橋接的應用,可以實現(xiàn)小于1.5W的總功率。 (5)低成本、低功耗的FPGA構架。

圖3.1 cyclone IV E EP4CE6E22C8N 型號芯片

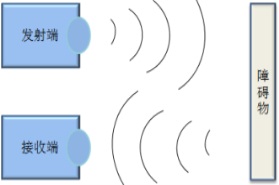

在選用該開發(fā)板之前,對實現(xiàn)一個具體系統(tǒng)應該有一個全方位的了解,針對系統(tǒng)的功能和需要的資源來具體選擇FPGA開發(fā)板。下面針對cyclone IV E系列的EP4CE6E22C8N 型號芯片的具體需用單元做出介紹: (1)具有可編程的輸入輸出端口 在該FPGA開發(fā)板中,I/O位于最左邊的部分,總共有32個。它們是FPGA芯片與外界電路的重要接口部分,同時它們也完成不同的電器特性對I/O信號的驅動和匹配需求,在編寫程序的時候,有時為了節(jié)省資源或為了程序的簡潔性,目前大多數(shù)FPGA 端口都設計成具有可編程性的I/O接口。FPGA針對外部設備的接口具有可以編寫程序并輸入芯片的功能,所以這樣就大大增加了FPGA的自由特性。 (2)較為豐富的布線資源 和cyclone系列的其他芯片一樣,F(xiàn)PGA本身就具有非常豐富的布線資源,它的這個特點可以給開發(fā)工程師們非常多的自我選擇,選擇最簡潔的布線方式和最簡便的算法。這些布線的結構和連線的長度對信號的傳輸速度起到了非常重要的影響,所以算法的優(yōu)先級和算法的優(yōu)化就顯的尤為重要了,它可能直接可以確定運算速度了。 (3)較低的功耗 Cyclone IV E系列芯片采用了經(jīng)過優(yōu)化后的60nm的工藝。它的內核電壓相對于前幾代的都有所降低。這在大規(guī)模集成電路的工程設計中既節(jié)省了資源,又降低了系統(tǒng)整體的功耗。這對于資源優(yōu)化與資源的合理分布有這非同尋常的價值所在。 (4)全面的設計資源 該系列FPGA核心芯片運行流暢,其IP庫也非常成熟,使用的是Quarters II開發(fā)軟件。不管是程序調試方面還是下載、電路圖仿真等方面都非常的便利。其嵌入式處理器采用的是NiosII處理,這是目前世界上最通用的嵌入式處理器。它可以使得綜合電路運行的更為流暢,時鐘頻率更加穩(wěn)定。 (5)全方位的時鐘網(wǎng)絡 該芯片時鐘網(wǎng)絡資源豐富,可以利用PLL進行分頻、倍頻;可以調用IP核對需要的時鐘頻率進行具體設定。并且在芯片處理系統(tǒng)中可以對不同的時鐘信號進行同時處理。 3.2 超聲波測距傳感器 首先介紹超聲波測量距離的原理,其次介紹超聲波測距模塊。超聲波測距的基本原理可以這樣認為,我們知道聲音在空氣里的傳播速度大約是0.34千米/秒。超聲波在空氣中的傳播速度大概也是0.34千米/秒,而這個速度受外界環(huán)境變化特別的小;況且超聲波的波長相對于空氣中的懸浮顆粒直徑較大,因而可以有效的繞射過空氣中的懸浮顆粒等直徑比較小的障礙物,所以可以認為它在空氣中的傳播速度基本可以維持在0.34千米/秒。基于這個基本不變的速度,只需測出其發(fā)出去以及反射回來的時間差,然后在通過一定的計算,就可以得到發(fā)射端到目標物體的距離了。 由以上的超聲波測量距離的原理圖就可以知道距離S可以被很簡潔的表達出來了。可以把聲速表示成V,超聲波從發(fā)射到接收的時間差為T,這樣距離就可以被表達成S=V*T/2。圖3.2中的方法可稱為間接測距法。還有一種直接測距的方法,直接測距就是將測距系統(tǒng)的發(fā)射端口和接收端口對準。發(fā)射的超聲波直接進入接收端,這樣就可以直接計算出其測量的距離了。這種測距系統(tǒng)并不僅僅局限于超聲波測距系統(tǒng),在一些激光測距、紅外測距等系統(tǒng)方面也有著一定價值的應用。

圖3.2 超聲波測量距離的原理圖 在本設計中利用超聲波在空氣中的傳播原理,按照S=V*T/2的關系計算出1毫米的時鐘高電平個數(shù)。利用距離單位的逐項疊加,逐個進位的方式計算出其距離。

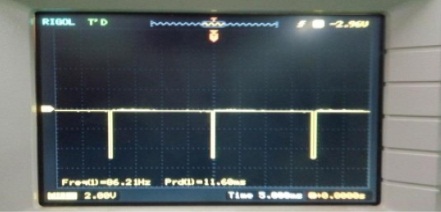

圖3.3 超聲波模塊 基于FPGA的超聲波測距系統(tǒng)利用的超聲波模塊型號為HC_SR04,它實際上采用的是給模塊上的trig端口一個觸發(fā)電平,讓其觸發(fā)超聲波的發(fā)出。 首先,在使用該模塊之前,對該超聲波模塊進行了簡單的端口測試。利用電壓源給該模塊接上5V的電壓。利用信號發(fā)生器產(chǎn)生一個10us的高電平脈沖信號,將此信號加到trig接口上,這樣就完成了對該超聲波模塊的觸發(fā)。然后將示波器探頭接在超聲波模塊的echo端口上,觀察示波器會顯示以下信號:

圖3.4 示波器觀測圖

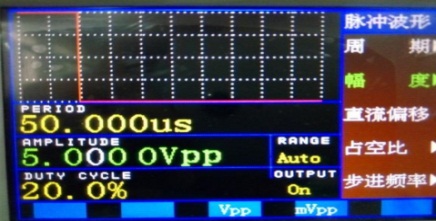

圖3.5 信號源信號圖 由圖3.5中的信號源可以看出,設置占空比為20%,脈沖電壓為5V,周期為50us。這樣信號源就可以產(chǎn)生一個10us的連續(xù)脈沖,將此脈沖信號送給trig端口,然后在超聲波模塊上的echo端口上加上示波器來測量echo上的信號變化。圖3.4所示,可以清楚的看到echo信號也呈現(xiàn)周期性變化,其原因就是給trig輸入的信號成周期性變化,每次經(jīng)過10us的連續(xù)高電平,超聲波就會發(fā)出一個調制的脈沖信號,該調制信號返回后,echo端的信號就會由高電平瞬間變回低電平了,所以echo信號的周期性變化是由trig信號的周期性變化引起的。還有一個值得注意的問題,觀察示波器的峰峰值可以看出echo反饋的高電平和給超聲波模塊的VCC端口所輸入的電壓信號的高電平值是一樣大的,因此就要考慮FPGA開發(fā)板的I/O接口所承受的最大耐壓值;比如像Xilinx的Basys系列的開發(fā)板I/O接口電壓承受值為3.3V,這種情況就要給echo接口加一個分壓電阻。以免返回電壓過大而對芯片造成一定程度的損傷。而ALTERA系列開發(fā)板的I/O接口一般情況可以承受5V的電壓值,因此可以直接將I/O接口與echo端口和trig端口接在一起。 4超聲波測距系統(tǒng)程序設計及仿真 4.1 程序流程圖 下圖給出了系統(tǒng)軟件設計的整體框架,實際上由于FPGA內的各個子進程都是并行執(zhí)行的,且每個子進程都是是獨立的模塊,因此程序設計并不是按照順序的方法設計的,而是分離成各個小的子模塊進行設計綜合的,需要嚴格控制時序。 超聲波收發(fā)部分負責產(chǎn)生超聲波驅動信號,要求頻率為50MHz,占空比為50的方波信號以驅動超聲波換能器,同時高速計數(shù)器開始計數(shù),檢測回波后,計數(shù)器停止計數(shù),計算后控制顯示輸出。

圖4.1 系統(tǒng)軟件設計框圖 4.2程序及仿真主控制模塊代碼: - <font style="font-size: 12pt">module temper(

- input CLOCK_50, // 板載時鐘50MHz

- input Q_KEY, // 板載按鍵RST

- input clk_1_sec,

- input echo, //回響信號輸出

- output reg trig, //超聲波模塊觸發(fā)信號輸入

- output [15:0]codeshow

- );

- //-------------------------------------

- //reg trig;

- reg [11:0]cnt; //計數(shù)器,計250個50ns,12.5us,為echo提供時序

- reg [13:0] cnt1; //計數(shù)器,計8000個12.5us,100ms

- reg [20:0]cnt3; //計數(shù)124個時鐘周期是1mm

- reg [19:0] dis ;

- reg

- echo_buf, //echo的上一個時鐘的狀態(tài)

- echo_rising, //捕捉echo的上升沿

- echo_falling, //捕捉echo的下降沿

- flag1; //echo為高電平時flag1會是1,低電平時會是0

- reg[3:0]beed1;

- reg[3:0]beed2;

- reg[3:0]beed3;

- reg[3:0]beed4;

- assign codeshow={beed4,beed3,beed2,beed1};

- //產(chǎn)生echo控制信號250*8000*50ns,echo高電平持續(xù)12.5us,即250個時鐘周期

- always@(posedge CLOCK_50)

- begin

- if(cnt == 2)//599

- cnt <= 1'b0;

- else

- cnt <= cnt +1;

- end

- always@(posedge CLOCK_50)

- begin

- if(cnt == 2)//599

- if(cnt1 == 20)//9999

- begin

- trig <= 1'b1;

- cnt1 <= 1'b0;

- end

- else

- begin

- trig <= 1'b0;

- cnt1 <= cnt1 + 1'b1;

- end

- end

- //捕捉trig上升沿與下降沿,并產(chǎn)生標志位

- always@(posedge CLOCK_50, negedge Q_KEY)

- begin

- if (!Q_KEY) echo_buf <= 1'b0;

- else

- begin

- echo_buf <= echo;

- echo_rising <= echo & (~echo_buf);

- echo_falling <= (~echo) & echo_buf;

- end

- end

- always@(posedge CLOCK_50)

- begin

- if(echo_rising == 1'b1)

- begin

- flag1 = 1'b1; //echo已經(jīng)變?yōu)楦唠娖?br />

- end

- else if(echo_falling == 1'b1)

- begin

- flag1 = 1'b0; //echo已經(jīng)變?yōu)榈碗娖?br />

- end

- end

- //在flag1 = 1 期間計時,即對時鐘進行計數(shù)。(4m的距離會是25ms,1mm是125個時鐘周期)

- always@(posedge CLOCK_50, negedge Q_KEY)

- begin

- if (!Q_KEY) dis<= 19'b0;

- else

- begin

- if(flag1 == 1'b1)

- begin

- if(cnt3 == 25) // 700000 //1mm

- cnt3 <= 1'b0;

- else

- cnt3 <= cnt3 + 1'b1;

- end

- else if(echo_rising == 1'b1)

- begin

- dis <=cnt3/1; //dis <=cnt3/290;

- cnt3 <= 1'b0;

- end

- end

- end

- always @ (posedge clk_1_sec, negedge Q_KEY)

- begin

- if (!Q_KEY)

- Begin

- beed <= 1'b0

- beed1 <= 4'b0;

- beed2 <= 4'b0;

- beed3 <= 4'b0;

- beed4 <= 4'b0;

- end

- else begin

- beed1 <=dis/1000;

- beed2 <=dis%1000/100;

- beed3 <=dis%100/10;

- beed4 <=dis%10;

- if(dis>16)begin beed<= 1'b0; end

- else begin beed<=1'b1; end

- end

- end

- endmodule</font>

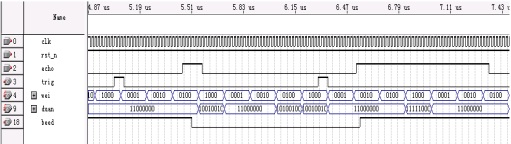

通過主控制程序,可以實現(xiàn)超聲波測距以及當測量距離小于一定長度時,蜂鳴器報警,報警距離可以通過改代碼,實現(xiàn)想要的報警的距離。下面是通過波形仿真的結果。如圖所示:

圖4.2 測距并報警 分頻模塊代碼: - <font style="font-size: 12pt">module div_50M(

- input clk,//50

- input rst_n,//

- output o_clk,//1HZ

- output o_clk1hz//1KHZ

- );

- // 分頻模塊開始

- reg [25:0] cnt; // 計數(shù)子

- reg [25:0] cntt; // 計數(shù)子

- reg regclk1hz;

- reg rego_clk;

- assign o_clk1hz=regclk1hz;

- assign o_clk=rego_clk;

- always @ (posedge clk, negedge rst_n)

- if (!rst_n)

- cntt <= 0;

- else

- if (cntt == 2)//cnt == 24_999_)//50M/1000=X,X/2-1=24999

- begin

- cntt <= 0;

- regclk1hz=(~regclk1hz);//1KHZ

- end

- else

- cntt <= cntt + 1'b1;

- always @ (posedge clk, negedge rst_n)

- if (!rst_n)

- cnt <= 0;

- else

- if (cnt == 1)//cnt == 24_999_999)

- begin

- cnt <= 0;

- rego_clk=(~rego_clk);//1KHZ

- end

- else

- cnt <= cnt + 1'b1;

- // 分頻模塊結束</font>

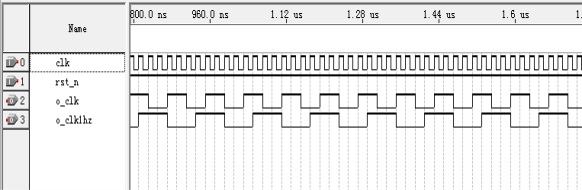

Endmodule 上述代碼中輸出的1KHZ時鐘,在之后進行譯碼器掃描。分頻模塊仿真如下圖示: 圖4.3 分頻模塊仿真 譯碼器模塊代碼: - <font style="font-size: 12pt">module yimaqi(clkshow ,codeshow,duan,wei);

- input clkshow;//1K的掃描時鐘輸入

- input [15:0]codeshow;//4個數(shù)碼管的顯示數(shù)據(jù)輸入,共16位,每4位一個密碼

- output [7:0]duan;//數(shù)據(jù)段選輸出

- output [3:0]wei;//動態(tài)掃描的位選輸出

- reg [3:0]dig1;

- reg [3:0]SEGAA;

- reg [3:0]countt;

- reg [7:0]LED;

- always @(posedge clkshow )

- begin

- countt=countt+1'b1;

- if(countt>3)begin countt=0;end

- case (countt)

- 0: SEGAA<=codeshow[3 : 0];

- 1: SEGAA<=codeshow[7 :4];

- 2: SEGAA<=codeshow[11 : 8];

- 3: SEGAA<=codeshow[15 : 12];

- default: countt=0;

- endcase

- case (countt)//動態(tài)掃描的位選輸出

- 0:dig1=4'b0001 ;

- 1:dig1=4'b0010 ;

- 2:dig1=4'b0100 ;

- 3:dig1=4'b1000 ;

- default: countt=0;

- endcase

- end

- assign wei=dig1;

- always @(SEGAA )//數(shù)據(jù)段選輸出

- begin

- case (SEGAA) //hgfedcba

- 4'h0:LED=8'b11000000;//--0

- 4'h1:LED=8'b11111001;//--1

- 4'h2:LED=8'b10100100;//--2

- 4'h3:LED=8'b10110000;//--3

- 4'h4:LED=8'b10011001;//--4

- 4'h5:LED=8'b10010010;//--5

- 4'h6:LED=8'b10000010;//--6

- 4'h7:LED=8'b11111000;//--7

- 4'h8:LED=8'b10000000;//--8

- 4'h9:LED=8'b10010000;//--9

- 4'ha:LED=8'b10001000;//--a

- 4'hb:LED=8'b10000011;//--b

- 4'hc:LED=8'b11000110;//--c

- 4'hd:LED=8'b10100001;//--d

- 4'he:LED=8'b10000110;//--e

- 4'hf:LED=8'b11111111;//--off

- endcase

- end

- assign duan=(dig1==4'b0001)?(LED&8'b01111111):LED;

- Endmodule</font>

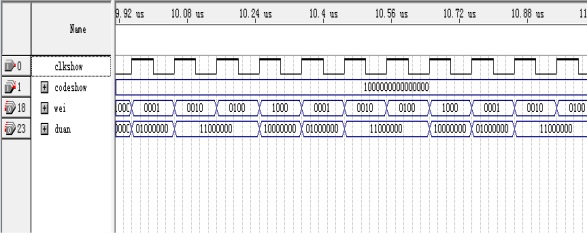

譯碼器模塊,通過掃描檢測到的1KHZ時鐘輸入,把測量到的距離顯示到數(shù)碼管上,譯碼器模塊仿真如下圖所示:

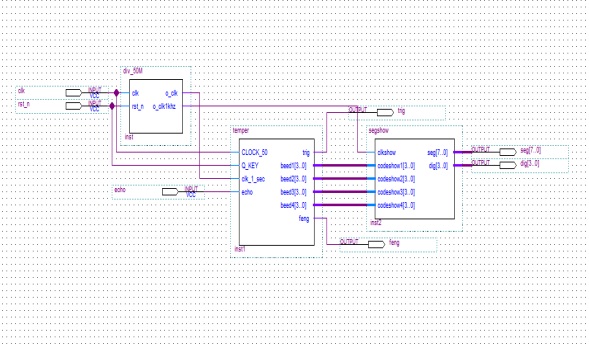

圖4.4 數(shù)碼管顯示仿真 4.3頂層原理圖頂層原理圖主要分為三個模塊,分別為分頻模塊,主控制模塊,譯碼器模塊。還有超聲波模塊接口,以及數(shù)碼管模塊接口。如下圖所示:

圖4.5 原理圖

結 論 此次的期末大作業(yè),雖然經(jīng)歷了一次次的困難,但積累了很多寶貴的經(jīng)驗。在整個設計的過程中遇到的問題主要有以下三點,第一:基礎知識掌握的不牢固,對書本上的內容理解不夠透徹,沒有掌握好編程相關知識。第二:超聲波測距這個模塊程序的編寫沒有思路、對VerilogHDL語言的不熟悉導致直接在程序中使用乘除法和取余等符號,雖然編譯器沒有報錯,但是運行完后根本沒有結果,也不能綜合出一個完整的電路。第三:相關知識掌握的不夠全面,缺少系統(tǒng)設計的經(jīng)驗。 這次大作業(yè)進一步端了我的學習態(tài)度,學會了實事求是,嚴謹?shù)淖黠L,對自己要嚴格要求,不能夠一知半解,要力求明明白白。急于求成是不好的,我有所感受。如果省略了那些必要的步驟,急于求成,不僅會浪費時間,還會適得其反。我覺得動手之前,頭腦里必須清楚該怎么做,這一點是很重要的。就目前來說,我的動手能力雖然差一點,但我想,通過我的不懈努力,在這方面,我總會得到提高。這一點,我堅信。因為別人能做到的,我也一定能做到。

0.png (9.46 KB, 下載次數(shù): 90)

下載附件

2019-3-3 22:34 上傳

全部資料51hei下載地址:

FPGA程序仿真.rar

(1.24 MB, 下載次數(shù): 160)

FPGA程序仿真.rar

(1.24 MB, 下載次數(shù): 160)

2019-3-3 18:35 上傳

點擊文件名下載附件

下載積分: 黑幣 -5

基于FPGA的超聲波測距.docx

(1.11 MB, 下載次數(shù): 116)

基于FPGA的超聲波測距.docx

(1.11 MB, 下載次數(shù): 116)

2019-3-3 18:35 上傳

點擊文件名下載附件

下載積分: 黑幣 -5

|