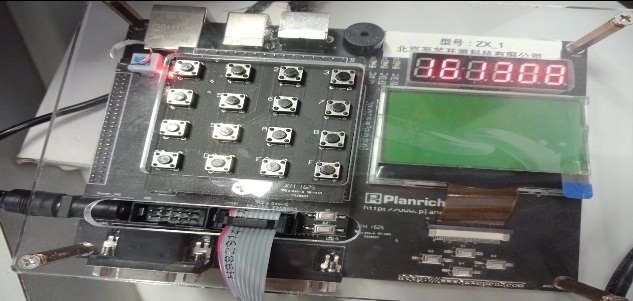

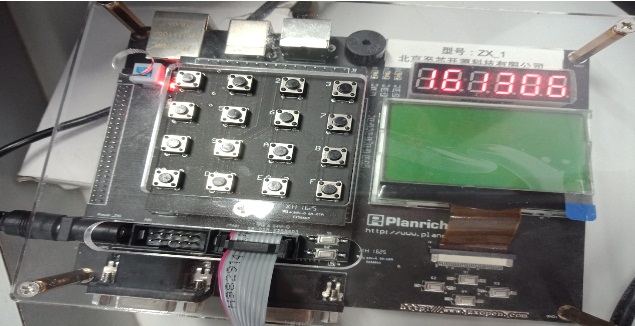

此設計是應用至芯科技開發板為硬件

Verilog源程序如下:

- //將50HZ分頻為1KHZ

- module freq(clk,rst_n,clk_1khz);

- input clk;

- input rst_n;//復位 低電平有效

- output reg clk_1khz;

- reg [14:0] cnt;//計數器(計數到2500,0,5ms)

-

- parameter cnt_num = 50_000_000 / 1000 /2 - 1 ;//0.5ms

-

- always @ (posedge clk or negedge rst_n) //異步復位

- begin

- if(!rst_n) //復位

- begin

- cnt <= 15'd0;//15代表位寬 '是形式,d代表十進制,0代表十進制的數值

- clk_1khz <= 1'b0;//賦初值

- end

- else

- begin

- if(cnt < cnt_num)//計數沒有到0.5

- begin

- cnt <= cnt + 1'd1;//計數器自動加一

- end

- else //計數到0.5

- begin

- cnt <= 15'd0; //計數器清0

- clk_1khz <= ~clk_1khz;//0.5ms高電平 0.5ms低電平

- end

- end

- end

- endmodule

所有資料51hei提供下載:

源代碼.rar

(4.33 MB, 下載次數: 96)

源代碼.rar

(4.33 MB, 下載次數: 96)

2019-1-26 16:29 上傳

點擊文件名下載附件

下載積分: 黑幣 -5

|