|

本文介紹了使用VHDL開發FPGA的一般流程,重點介紹了頻率計的基本原理和相應的測量方案,最終采用了一種基于FPGA的數字頻率的實現方法。該設計采用硬件描述語言VHDL,在軟件開發平臺ISE上完成,可以在較高速時鐘頻率(100MHz)下正常工作。該設計的頻率計能準確的測量頻率在1Hz到100MHz之間的信號。使用ModelSim仿真軟件對VHDL程序做了仿真,并完成了綜合布局布線,最終下載到芯片Spartan-II上取得良好測試效果。

原理框圖 測試結果 參考文獻 計數器級聯程序 鎖存器源程序 頂層原理圖 計數器的級聯圖 外文資料原文 翻譯文稿

第一章 引言

第二章 基于FPGA的VHDL設計流程

2.1 概述

2.2 VHDL語言介紹

2.2.1 VHDL的特點

2.2.2 基于VHDL的自頂向下設計方法

2.3 FPGA開發介紹

2.3.1 FPGA簡介

2.3.2 FPGA設計流程

2.3.3 Spartan-II芯片簡介

第三章 數字頻率計的軟件開發環境

3.1 開發環境

3.2 ModelSim介紹

3.2.1 ISE環境中ModelSim的使用

3.3 ISE介紹

3.3.1 建立項目工程

3.3.2 行為仿真

3.3.3 建立頂層原理圖

3.3.4 綜合

3.3.5 布局布線

3.3.6 下載及硬件仿真

第四章 數字頻率計的設計與實現

4.1 任務要求

4.2 測量原理

4.2.1 頻率或時間的原始基準

4.2.2 電子計數器測頻方法

4.2.3 誤差分析

4.2.4 測量周期的必要性和基本原理

4.2.5 等精度測量

4.3 原理框圖

4.4 各模塊的功能及實現

4.4.1 分頻器

4.4.2 閘門選擇器

4.4.3 測頻控制器

4.4.4 頻率計數器

4.4.5 鎖存器

4.4.6 掃描顯示控制譯碼系統

4.5 頂層原理圖

4.6 分配引腳和下載實現

4.7 測試結果

第五章 結論

參考文獻

致 謝

附 錄

附錄1. 計數器級聯程序

附錄2. 鎖存器源程序

附錄3. 頂層原理圖

附錄4. 計數器的級聯圖

外文資料原文

翻譯文稿

在電子技術領域內,頻率是一個最基本的參數,頻率與其它許多電參量的測量方案、測量結果都有十分密切的關系。如時間,速度等都涉及到或本身可轉化為頻率的測量。因此,頻率的測量就顯得更為重要。而且,目前在電子測量中,頻率的測量精確度是最高的.現在市場上有各種多功能,高精度,高頻率的數字頻率計,但價格不菲。而在實際工程中,不是對所有信號的頻率測量都要求達到非常高的精度。因此,本文提出了一種能滿足一般測量精度要求,但成本低廉的數字頻率計的設計方案。

本文主要任務是針對設計的要求,基于FPGA利用硬件描述語言VHDL完成數字頻率計的設計,通過仿真,分析,綜合并最終下載到FPGA里面去實現。除被測信號的整形部分、鍵輸入部分以外,其余全部在一片FPGA芯片上實現,整個系統非常精簡,而且具有靈活的現場可更改性。在不更改硬件電路的基礎上,對系統進行各種改進還可以進一步提高系統的性能。該數字頻率計具有高速、精確、可靠、抗干擾性強和現場可編程等優點。經實驗表明,其測量精度基本能達到,且系統成本非常低廉,可作為學生數字邏輯設計綜合實驗或自制數字頻率計的備選方案。

第二章 基于FPGA的VHDL設計流程2.1 概述數字頻率計是數字電路中的一個典型應用,實際的硬件設計用到的器件較多,連線比較復雜,而且會產生比較大的延時,造成測量誤差、可靠性差。頻率計的設計有傳統方法和現代方法,傳統的設計方法耗時耗功,設計強度大,且容易出錯,設計的質量不一定是最好的。自然我們考慮到現代方法,即二十世紀八十年代興起的電子設計自動化技術,英文為Electronic Design Auto,縮寫為EDA。在EDA設計工具中,用的最廣泛的是VHDL和VERILOG,當然還有其它的。比較VHDL和VERILOG,在頂層設計方面VHDL優于VERILOG,在門級電路設計方面VERILOG優于VHDL。隨著復雜可編程邏輯器件(CPLD)的廣泛應用,以EDA工具作為開發手段,運用VHDL語言,將使整個系統大大簡化,提高整體的性能和可靠性。本次的頻率計設計主要是頂層設計,目的是設計6位十進制頻率計,學習常用的數字系統設計方法。采用VDHL編程設計實現的數字頻率計,除被測信號的整形部分、鍵輸入部分以外,其余全部在一片FPGA芯片上實現,整個系統非常精簡,而且具有靈活的現場可更改性。在不更改硬件電路的基礎上,對系統進行各種改進還可以進一步提高系統的性能。該數字頻率計具有高速、精確、可靠、抗干擾性強和現場可編程等優點。 2.2 VHDL語言介紹VHDL(Very-high-speed Integrated Circuit Hardware Description Language)誕生于1982年。1987年底,VHDL被IEEE(The Institute of Electrical and Electronics Engineers)和美國國防部確認為標準硬件描述語言。自IEEE公布了VHDL的標準版本(IEEE-1076)之后,各EDA公司相繼推出了自己的VHDL設計環境,并宣布自己的設計工具可以和VHDL接口。此后VHDL在電子設計領域得到了廣泛的接受,并逐步取代了原有的非標準硬件描述語言。1993年,IEEE對VHDL進行了修訂,從更高的抽象層次和系統描述能力上擴展VHDL的內容,公布了新版本的VHDL,即IEEE標準的1076-1993版本。現在,VHDL和VERILOG作為IEEE的工業標準硬件描述語言,又得到眾多EDA公司的支持,在電子工程領域,已成為事實上的通用硬件描述語言。有專家認為,在新的世紀中,VHDL和VERILOG語言將承擔起幾乎全部的數字系統設計任務。 2.2.1 VHDL的特點VHDL主要用于描述數字系統的結構、行為、功能和接口。除了含有許多具有硬件特征的語句外,VHDL的語言形式,描述風格以及句法十分類似于一般的計算機高級語言。VHDL的程序結構特點是將一項工程設計,或稱為設計實體(可以是一個元件、一個電路模塊或一個系統)分成外部(又稱為可視部分,即端口)和內部(又稱為不可視部分),即設計實體的內部功能和算法完成部分。在對一個設計實體定義了外部界面后,一旦其內部開發完成后,其它的設計就可以直接調用這個實體。這種將設計實體分成內外部分的概念是VHDL系統設計的基本點。應用VHDL進行工程設計的優點是多方面的,具體如下: 1、與其它的硬件描述語言相比,VHDL具有更強的行為描述能力,從而決定了它成為系統設計領域最佳的硬件描述語言。強大的行為描述能力是避開具體的器件結構,從邏輯行為上描述和設計大規模電子系統的重要保證。就目前流行的EDA工具和VHDL綜合器而言,將基于抽象的行為描述風格的VHDL程序綜合成為具體的FPGA和CPLD等目標器件的網表文件已不成問題,只是在綜合與優化效率上略有差異。 2、VHDL最初是作為一種仿真標準格式出現的,因此VHDL既是一種硬件電路描述和設計語言,也是一種標準的網表格式,還是一種仿真語言。其豐富的仿真語句和庫函數,使得在任何大系統的設計早期(即尚未完成),就能用于查驗設計系統的功能可行性,隨時可對設計進行仿真模擬。即在遠離門級的高層次上進行模擬,使設計者對整個工程設計的結構和功能的可行性做出決策。 3、VHDL語句的行為描述能力和程序結構決定了它具有支持大規模設計的分解和已有設計的再利用功能,符合市場所需求的,大規模系統高效、高速的完成必須由多人甚至多個開發組共同并行工作才能實現的特點。VHDL中設計實體的概念、程序包的概念、設計庫的概念為設計的分解和并行工作提供了有力的支持。 4、對于用VHDL完成的一個確定的設計,可以利用EDA工具進行邏輯綜合和優化,并自動地把VHDL描述設計轉變成為門級網表。這種方式突破了門級電路設計的瓶頸,極大地減少了電路設計的時間和可能發生的錯誤,降低了開發成本。應用EDA工具的邏輯優化功能,可以自動地把一個綜合后的設計變成一個更高效、更高速的電路系統。反過來,設計者還可以容易地從綜合和優化后的電路獲得設計信息,返回去更新修改VHDL設計描述,使之更為完善。 5、VHDL對設計的描述具有相對獨立性,設計者可以不懂硬件的結構,也不必管最終設計實現的目標器件是什么,而進行獨立的設計。正因為VHDL硬件描述與具體的工藝技術和硬件結構無關,VHDL設計程序的硬件實現目標器件有廣闊的選擇范圍,其中包括各系列的CPLD、FPGA及各種門陣列實現目標。 6、由于VHDL具有類屬描述語句和子程序調用等功能,對于已完成的設計,在不改變源程序的條件下,只需要改變端口類屬參量或函數,就能輕易地改變設計的規模和結構。 2.2.2 基于VHDL的自頂向下設計方法2.2.2.1 自頂向下設計的步驟1、設計說明:用自然語言表達系統項目的功能特點和技術參數等。 2、建立VHDL行為模型,即將設計說明已轉化為VHDL行為模型。建立模型是為了通過VHDL仿真器對整個系統進行系統行為仿真和性能評估。 3、VHDL行為仿真。這一階段可以利用VHDL仿真器對頂層系統的行為模型進行仿真測試,檢查模擬結果,繼而進行修改和完善。 4、VHDL-RTL級建模。即將VHDL的行為模型表達為VHDL行為代碼。 5、前端功能仿真。即對VHDL-RTL級模型進行仿真,簡稱功能仿真。 6、邏輯綜合。使用邏輯綜合工具將VHDL行為代碼描述轉化為結構化的門級電路。 7、測試向量生成。 8、功能仿真。 9、結構綜合。 10、門級時序仿真。 11、硬件測試。 2.2.2.2 Top-down設計方法的優點1、完全符合設計人員的設計思路;從功能描述開始,到最后的物理實現。 2、功能設計可完全獨立于物理實現;采用Top-Down設計方法,功能輸入采用國際標準的HDL輸入方法,HDL可不含有任何器件的物理信息,因此工程師可以有更多的空間去集中精力進行功能描述。設計師可以在設計過程的最后階段任意選擇或更改物理器件,不會在設計一開始就受到最終所采用器件的約束。 3、設計可再利用;設計結果完全可以以一種知識產權(IP-Intellectual Property)的方式作為設計師或設計單位的設計成果,應用于不同的產品設計中,做到成果的再利用。 4、易于設計的更改;設計工程師可在極短的時間內修改設計,對各種FPGA/CPLD結構進行設計結果規模(門消耗)和速度(時序)的比較,選擇最優方案。 5、設計和處理大規模復雜電路;目前的FPGA/CPLD器件正向高集成度、深亞微米工藝發展。為設計系統的小型化,低功耗、高可靠性等提供了集成的手段。 6、設計周期縮短,生產率大大提高,產品上市時間提前,性能明顯提高,產品競爭力加強。據統計,采用Top-Down設計方法的生產率可達到傳統設計方法2到4倍。 2.3 FPGA開發介紹2.3.1 FPGA簡介現場可編程門陣列(FPGA)器件是八十年代中期出現的新產品,它的應用大大地方便了IC的設計,因而隨著數字技術日益廣泛的應用,以FPGA為代表的ASIC器件得到了迅速的普及和發展,器件集成度和速度都在高速增長。 傳統的電路設計過程是:先畫原理圖、把原理圖繪制成印制電路板圖、再制版、安裝、調試。有了FPGA,我們只需要在計算機上繪出原理圖,再運行相應的軟件,就可把所設計的邏輯電路在FPGA中實現。所有步驟均可自動完成。電子設計工程師自己設計專用集成電路成為了一件很容易的事情。 FPGA作為專用集成電路(ASIC)概念上的一個新型范疇和門類,以其高度靈活的用戶現場編程方式,現場定義高容量數字單片系統的能力,能夠重復定義、反復改寫的新穎功能,為復雜數字系統設計、研制以及產品開發提供了有效的技術手段。電子應用設計工程師應用FPGA技術不僅可避免通常ASIC單片系統設計周期長,前期投資風險大的弱點,而且克服了過去板級通用數字電路應用設計的落后,繁瑣和不可靠性。 目前FPGA的兩個重要發展與突破是,大多數廠商在其高端器件上都提供了片上的處理器(如CPU、DSP)等硬核(Hard Core)或固化核(Fixed Core)。比如Xilinx的Virtex II Pro芯片可以提供Power PC,而Altera的Stratix、Excalibur等系列芯片可以提供Nios、DSP和Arm等模塊。在FPGA上集成微處理器,使SOPC設計更加便利與強大。另一個發展是在不同器件商推出的高端芯片上大都集成了高速串行收發器,一般能夠達到3Gb/s以上的數據處理能力,在Xilinx、Altera、Lattice都有相應的器件型號提供該功能。這些新功能使FPGA的數據吞吐能力大幅度增強。 2.3.2 FPGA設計流程對于目標器件為FPGA和CPLD的HDL設計,其工程設計的基本流程如圖 2-1所示。現具體說明如下。 圖 2-1 EDA設計流程 1、文本編輯 用任何文本編輯器都可以進行,通常VHDL文件保存為vhd文件,Verilog文件保存為v文件。 2、使用編譯工具編譯源文件 HDL的編譯器有很多,ACTIVE公司,MODELSIM公司,SYNPLICITY公司,SYNOPSYS公司,VERIBEST公司等都有自己的編譯器。 3、邏輯綜合 將源文件調入邏輯綜合軟件進行綜合。綜合的目的是在于將設計的源文件由語言轉換為實際的電路。但是此時還沒有在芯片中形成真正的電路。這一步的最終目的是生成門電路級的網表(Netlist)。 4、布局、布線 將第3步生成的網表文件調入PLD廠家提供的軟件中進行布線,即把設計好的邏輯安放到CPLD/FPGA內。這一步的目的是生成用于下載(編程Programming)的編程文件。在這一步,將用到第3步生成的網表,并根據CPLD/FPGA廠商的器件容量,結構等進行布局、布線。這就好像在設計PCB時的布局布線一樣。先將各個設計中的門根據網表的內容和器件的結構放在器件的特定部位。然后,在根據網表中提供的各門的連接,把各個門的輸入輸出連接起來。最后,生成一個供編程的文件。這一步同時還會加一些時序信息(Timing)到你的設計項目中去,以便于你做后仿真。 5、后仿真 利用在布局布線中獲得的精確參數,用仿真軟件驗證電路的時序。(也叫布局布線仿真或時序仿真)。這一步主要是為了確定你的設計在經過布局布線之后,是不是還滿足你的設計要求。 6、編程,下載 如果前幾步都沒有發生錯誤,并且符合設計要求,這一步就可以將由適配器等產生的配置或下載文件通過編程器或下載電纜下載到目標芯片中。 7、硬件測試 硬件測試的目的是為了在更真實的環境中檢驗HDL設計的運行情況,特別是對于HDL程序設計上不是十分規范,語義上含有一定歧義的程序。 2.3.3 SPARTAN-II芯片簡介本設計用到的FPGA芯片是XILINX公司生產的SPARNTAN-II系列中的xc2s100-6。下面將對該系列做簡單的介紹。 2.3.3.1 Spartan-II系列的特點進入ASSP的領域FPGA正在極力將ASSP從電路板上擠出去,并使其失去設計人員的寵愛。但是任何舊式的FPGA器件都無法恰當地替代專用器件。只有Spartan-II FPGA可以做到這一點。Spartan-II系列為設計人員提供了完整的封裝。在密度、功能和性能以及運行速度方面都差不多。但是,Spartan-II為解決方案所提供的可編程能力有著巨大的價值,從而使其與ASSP/ASIC器件相比具有了很大的優勢。 1、現場升級的靈活性 Spartan-II FPGA的可編程能力為設計人員帶來很大優勢。采用的FPGA是標準器件后,您可更快地將產品標準化。因為Spartan器件可進行現場升級,升級就像下載軟件一樣簡單。 2、擁有豐富的邏輯門資源 Spartan-II系列有六款器件,密度高達20萬門。豐富的邏輯門資源能讓設計者更大限度的發揮。 3、告別ASIC和FPGA間的性能和功能差距 在性能和功能方面,大多數設計人員都會想到ASIC和FPGA間的巨大差距。但是SPARTAN-II消除了這一差距。 4、擁有最多的存儲器 片上帶存儲器是必須的,如果還具有很好的靈活性的話,那么就更為有用了。分布式存儲器和塊RAM可高效地實現最適合您要求的配置,現時還可采用與片上存儲器一樣快的外部存儲器。 5、方便的時鐘管理 如果您面臨時鐘管理問題,Spartan-II系列的四個高度靈活的DLL可解決您的問題。設計人員可在片上對輸入時鐘進行倍頻或分頻,還可驅動板上的多個時鐘。 6、提供高性能 今天的數字世界里有許多新的I/O標準要求很苛刻。通過Select I/O技術,Spartan-II器件支持所有這些新I/O標準。I/O速度超過200 MHz。Spartan-II系列豐富的功能、以及高性能和低成本,使其成為多種數據網絡應用HDLC控制器解決方案中的首選。Spartan-II也非常適于實現控制和接口邏輯,比如用于將CPU同QDR SRAM連接在一起。 7、器件密度擴展至20萬門 隨著大量產品的設計變得越來越復雜,對更高密度、更大存儲器資源以及更多I/O數量的需求也在增長。對于此類設計,Spartan-II系列的XC2S200非常適合,該器件能提供20多萬個門、14個RAM塊以及284個I/O,并有三種不同的低成本適合大批量生產的封裝PQ208、FG256和FG456可供選擇。利用XC2S200,可獲得比XC2S150多36%的邏輯單元,而且其密度是Spartan或Spartan-XL最大器件密度的五倍。XC2S200包括了支持Spartan-II解決方案獲得成功的所有特性。 2.3.3.2 Spartan-II的結構特點1、結構框圖 Spartan-II系列FPGA采用了常規的靈活可編程構架,包括可配置邏輯塊(CLB)和環繞在CLB四周的可編程輸入/輸出模塊(IOB),并通過多用途布線資源形成強大的互連體系。 圖2-2 Spartan-ii 的結構框圖 2、輸入/輸出模塊 Spartan-II的IOB的輸入和輸出支持16種I/O信號標準,包括LVCMOS、HSTL、SSTL和GTL。這些高速輸入和輸出可支持各種先進的存儲器和總線接口。三個IOB寄存器可作為邊沿觸發D型觸發器或作為電平敏感的鎖存器。 圖2-3 Spartan-ii 的輸入輸出模塊 3、邏輯單元 Spartan-II CLB的基本構造單元是邏輯單元(LC)。一個LC包括一個四輸入的函數發生器、一個進位邏輯和一個存儲單元。每個LC中函數發生器的輸出同時驅動CLB輸出端和觸發器的D輸入端。每個Spartan-II CLB包含四個LC,兩兩組合成兩個同樣的Slice。除了四個基本LC外,Spartan-II CLB還包含一些邏輯電路,結合函數發生器可提供五個或六個輸入的函數功能。因此當預計給定器件所能提供的系統門數量時,每個CLB可當作4.5個邏輯單元來計算。 Spartan-II函數發生器采用4輸入查找表(LUT)的方式來實現。除了作為函數發生器以外,每個LUT還可作為一個16*1位的同步RAM來使用。Spartan-II LUT還可作為一個16位移位寄存器使用,而且對于捕捉高速或猝發數據非常理想。這一模式還可在諸如數字信號處理等應用中用于數據的存儲。Spartan-II邏輯片中的存儲單元可通過配置成為邊沿觸發型D型觸發器或電平敏感鎖存器。

圖2-4 Spartan-ii的邏輯單元 4.塊RAM Spartan-II FPGA集成了幾塊大型的4K位容量Select RAM+ 存儲器塊。這與在CLB中能夠實現淺RAM結構的分布式Select RAM+資源互為補充。每個存儲器塊可配置為4K x 1 和256 x 16之間的多種不同配置。 圖2-5 Spartan-ii的塊RAM 5.延遲鎖相環 與每個全局時鐘輸入緩沖器相連的是一個完全數字的延遲鎖相環(DLL),它可消除時鐘輸入焊盤和器件內部時鐘輸入引腳間的畸變。每個DLL可驅動兩個全局時鐘網絡。首先監視輸入的時鐘信號,然后是分布式時鐘信號,并自動地調整時鐘延遲單元。通過引入額外的延遲來保證時鐘邊沿嚴格地在到達時鐘輸入端一個時鐘周期后到達內部觸發器。通過保證到達內部觸發器的時鐘邊沿與到達時鐘輸入端的時鐘邊沿嚴格同步,這一閉環系統有效地消除了時鐘傳輸延遲。

第三章 數字頻率計的軟件開發環境本章主要介紹項目中將要用到了一系列軟件,包括用于VHDL語言編寫和編譯的ISE軟件和用于程序仿真的仿真軟件ModelSim。 3.1 開發環境隨著可編程器件紛紛超越百萬門級,設計者面臨的產品性能與設計效率的挑戰也越來越大。設計者必須合理選擇各EDA廠家提供的加速設計的工具軟件,這樣才能在較短的時間內設計出高效穩定的產品。在本次設計中,由于選擇的FPGA芯片是由Xilinx公司生產的,所以我們主要使用ModelSim和ISE軟件進行仿真和綜合。 3.2 ModelSim介紹ModelSim支持PC和UNIX平臺,是單一內核支持VHDL和Verilog混合仿真的HDL語言仿真器。ModelSim不僅可以完成設計的功能驗證,也可實現邏輯綜合后的門級仿真以及布局布線后的功能與時序驗證。 ModelSim完全支持VHDL和Verilog標準;采用直接編輯技術,大大提高HDL編譯和仿真速度。還可以利用ModelSim調用設計文件進行仿真分析。在調試環境中,設計者可以通過ModelSim的快速調試步驟以及對各種信號的監控功能(無論信號處于VHDL層,還是處于混合語言層)使仿真的執行過程形象直觀化,幫助設計者及時發現漏洞,縮短設計周期。 ModelSim最大的特點是其強大的調試功能:先進的數據流窗口,可以迅速追蹤到生產不定或者錯誤狀態的原因;性能分析工具幫助分析性能瓶頸,加速仿真;代碼覆蓋率檢查確保測試的完備;多種模式的波形比較功能;先進的 SignalSpy功能,可以方便地訪問VHDL或者VHDL和Verilog混合設計中的底層信號;支持加密IP;可以實現與Matlab的Simulink的聯合仿真。 3.2.1 ISE環境中ModelSim的使用ModelSim是一個獨立的仿真工具,它在工作的時候并不需要其他軟件的協助,在Xilinx公司的ISE集成開發環境中給ModelSim仿真軟件預留了接口,通過這個接口可以從ISE集成環境中直接啟動ModelSim工具進行仿真。這個過程通常會給初學者一個錯覺,以為ISE集成環境和ModelSim工具是聯合工作的,其實ISE并沒有集成ModelSim工具,只是預留了軟件接口。為了說明ModelSim的用戶接口,將使用從ISE集成開發環境中直接啟動ModelSim仿真工具的方法。使用此種方法啟動ModelSim工具需要具備3個條件:第一,啟動ISE集成開發環境并建立了一個FPGA/CPLD的工程項目;第二,添加設計源代碼并且編譯通過;第三,使用ISE中的TestFixture或者TestBenchWaveform工具為當前的設計提供一個測試模板(Testbench),并且在測試模板中添加設計激勵。只有上述條件具備之后才可以從ISE的當前資源操作窗中直接啟動ModelSim工具并運行仿真,以下使用ISE自帶的一個例子加以說明。 在ISE中直接啟動ModelSim 1、在Windows操作系統中選擇[開始]/[程序]/[Xilinx ISE 6]/[Project Navigator]命令,啟動ISE集成開發環境。 2、在ISE主窗口中選擇[File]/[Open Example]命令,彈出[Open Example]對話框,如圖所示,然后在[Select an Example Project]欄目中選擇“goldcode-ver-217”,在[Destination Directory]中選擇項目存放的目錄,單擊OK按鈕打開例子程序。 圖3-1 打開例子程序 3、在資源管理窗口(Source in Project)中的模塊視圖(Model View)中選中的測試文件“testbench.tf”,在相應的當前資源操作窗口(Process for Current Source)中將會出現與Modelsim仿真器相關的行為仿真(Simulate Behavioral Verilog Model),翻譯后仿真(Simulate Post-Map Verilog Model)和布局布線后仿真(Simulate Post-Place & Route Verilog Model)等4個不同的操作選項,如圖所示: 圖 3-2 Modelsim 仿真 4、雙擊[Simulate Behavioral Model]操作選項,將啟動Modelsim仿真器。 5、在Modelsim主窗口中選擇[View]/[All]命令,將顯示所有的窗口。 在當前資源操作窗口中選擇任意一個操作選項都可以啟動相應階段的仿真操作,如果相應階段的仿真文件不存在,那么集成環境將自動生成仿真文件。例如,當雙擊資源操作窗口中的[Simulate Post-Place & Route Verilog Model]操作選項時將啟動時序仿真,而這一仿真過程所需要的布局布線后仿真文件以及時序標注文件都還沒有產生,那么ISE集成開發環境將自動開始對這個工程進行編譯,綜合,翻譯,映射和布局布線等操作,得到布局布線后仿真文件以及時序標注文件,然后再啟動ModelSim仿真器進行時序仿真。 3.3 ISE介紹本節主要介紹在XILINX的ISE集成軟件環境中,如何用VHDL和原理圖的方式進行設計輸入,如何用ModelSim仿真工具對設計進行功能仿真和時序仿真,如何實現設計。 3.3.1 建立項目工程建立新的項目工程,選擇【File】,再選擇【New Project】,如圖就可以了。 圖 3-3 ISE建立新工程 選擇使用的可編程器件類型device family-器件族名device-器件型號package-封裝speed grade-速度top-level module type-頂層文件類型synthesis tool-綜合工具simulator-仿真工具generated simulation language-生成的仿真模型語言。 圖 3-4 選擇器件 然后一路NEXT,最后點擊完成。剛生成的工程是沒有類型的,需要自己加入。方法是在 sources in project中右擊,選擇add sources,選擇你寫的文件加入即可。如果要新寫程序,用同樣的方法,選擇new sources即可,會彈出如下對話框,讓你選擇New Sources的類型。 圖 3-5 選擇New Sources的類型 選擇vhdl module,寫上文件名,在下一頁可以寫上輸入輸出口,也可以不寫。一路NEXT到完成就可以。這樣就可以開始寫代碼或繼續下一步綜合了。要打開或編輯新建的文件,直接在sources in project窗口中雙擊該文件即可。 3.3.2 行為仿真1、在工程項窗口Project Window的源文件中選中計數器(counter.vhd)。 2、選擇Project/New Source。 3、在新的對話框中選擇新文件類型為Test Bench Waveform。 4、鍵入文件名為counter_tbw。 5、點擊Next,在其他工程項中你可以將你的testbench波形與其他源文件關聯。 6、一直Next直到Finish,此時HDL Bencher 程序自動啟動并等候你輸入所需的時序需求,你現在可以指定仿真所需的時間參數、時鐘高電平時間和時鐘低電平時間一起定義了設計操作必須達到的時鐘周期,輸入建立時間定義了輸入在什么時候必須有效,輸出有效延時,定義了有效時鐘沿到達后多久必須輸出有效數據。 默認的初始化時間設置如下: 時鐘高電平時間: Clock high time: 50 ns 。 時鐘低電平時間: Clock low time: 50 ns 。 輸入建立時間: Input setup time: 10 ns 。 輸出有效時間: Output valid delay: 10 ns 。 7、點擊OK,接受默認的時間設定。Testbench waveform窗口如下。 圖 3-6 Testbench Waveform 在HDL Bencher 的波形中,初始化計數器輸入如下: 在每個單元的藍色區域輸入激勵。 a、在CLK第1周期下點擊RESET單元直到該單元變為。 b、在CLK第2周期下點擊RESET單元直到該單元變為低。 c、在CLK第3周期下點擊CE單元直到該單元變為高。 d、在CLK第2周期下點擊DIR單元直到該單元變為高。 圖 3-7 激勵輸入 e、將你的testbench文件存盤,選擇File/Save Waveform或點擊工具欄的存盤圖標,接下來HDL Bencher會提示你設置你希望仿真的時鐘周期數。 f、在End the testbench __ cycles after the last input assignment對話框中輸入8,默認值為1。 g、點擊OK.退出HDL Bencher新的testbench波形源文件counter_tbw.tbw自動加入到該工程項中。 8、生成預期的輸出響應: 我們進行行為仿真以驗證計數器模塊的功能。 a、在Sources in Project窗口中選擇counter_tbw.tbw文件。 b、在Processes for Current Source窗口中點擊 + 符號展開ModelSim仿真器的層次結構找到并雙擊Simulate Behavioral VHDL Model,此時ModelSim仿真器自動啟動。 c、對于第一次運行ModelSim的用戶會顯示一個對話框需要在其中做以下處理:選中Do not show this dialog again選項,點擊Run ModelSim此對話框在你重新安裝或重新配置ModelSim之前將不再顯示你的仿真結果現在顯示在ModelSim的波形窗口(wave window)。 d、點擊Zoom / Zoom Full;點擊Zoom / Zoom in。 e、拖動波形窗口下端的滾動條至窗口的最左端。 圖 3-8 仿真圖 3.3.3 建立頂層原理圖3.3.3.1 生成原理圖符號1、在Sources in Project窗口中選中計數器模塊counter.vhd。 2、在Processes for Current Source窗口中,點擊設計輸入實用程序(Design Entry Utilities)之前的“+”符號然后雙擊創建原理圖符號(CreateSchematic Symbol)經過以上步驟,名稱為“counter”的圖形化元件被放入到工程項庫中。 3.3.3.2 創建頂層原理圖1、在工程項導航器(Project Navigator)菜單中,選擇Project/New Source。 2、選擇原理圖(Schematic)為源類型。 3、輸入原理圖名為“top”。 4、先點擊“Next”再點擊“Finish”,此時原理圖編輯器(ECS)自動啟動并在其原理圖窗口中打開一張空圖。 3.3.3.3 例化VHDL模塊1、在菜單中選擇Add / Symbol或者在工具欄中點擊(Add Symbol)圖標。 2、從元件符號列表(在屏幕右側)中選擇計數器counter,注意不要在類別(Categories)窗口中作任何選擇。 3、點擊左鍵可將計數器counter放置在光標所在的位置出現。 4、按ESC鍵退出添加符號(Add Symbol)模式。 圖 3-9 例化VHDL模塊 3.3.3.4 原理圖連線1、首先激活劃線功能通過在菜單中選擇Add/Wire或者在工具欄中點擊 (Add Wire)圖標。 2、添加一根懸空線和延展連線,在計數器模塊的某一管腳單擊鼠標,然后將連線拉伸到需要的長度。再在連線端點處雙擊鼠標,給計數器模塊的每一管腳添加連線。 3、添加兩個元件符號之間的連線,在一個計數器模塊的管腳處單擊鼠標,在另一個計數器模塊的對應管腳處雙擊鼠標。連接好線后按ESC鍵退出添加連線(Add/Wire)模式。 圖 3-10 原理圖連線 3.3.3.5 添加輸入輸出管腳標記1、在菜單中選擇Add/ (I/O Marker)或在工具欄中點擊(Add I/O Marker)圖標,連接好的圖如下。 圖 3-11 添加輸入輸出管腳 2、連接步驟:首先為clock,reset,ce,load,dir1和dir2添加輸入標記,同時為總線din1(3:0)和din2(3:0)添加輸入標記。在工具欄右邊的參數單選框中選擇輸入(Input);將鼠標移動到輸入信號線的端點,此時光標處顯示出輸入標記的圖形;點擊鼠標左鍵,輸入標記會將網絡名或總線名包含在標記圖形的內部。 3、按如下步驟為count總線添加雙向信號標記。在工具欄右邊的參數單選框中選擇雙向(Bidirectional);將鼠標移動到輸出信號線的端點,此時光標處顯示出雙向信號標記的圖形;點擊鼠標左鍵。 4、在菜單中選擇File/Save,保存原理圖,退出原理圖編輯器(ECS)。 3.3.4 綜合3.3.4.1 Synthesize綜合當你編寫程序后,并把頂層原理圖連接好以后,就可以綜合了。選中你的頂層文件,雙擊Synthesize-Synplify Pro。 圖 3-12 綜合 如果出現上圖的小勾,表示綜合沒有問題。你可以雙擊View RTL Schematic來查看綜合后的RTL原理圖。 3.3.4.2 定義輸入輸出管腳約束選中頂層文件,雙擊下圖中的Assign Package Pins,該操作會提示系統將生成一個.ucf文件,選擇是,系統將自動啟動Xilinx Pace。 圖 3-13 分配引腳 圖 3-14 Xilinx Pace 現在就可以在LOC欄寫上管腳名,定義I/O電平類型,輸出電流大小等,需要注意的是一些I/O是有特殊用處的,不能胡亂分配。定義完后保存退出。 3.3.5 布局布線雙擊Implement Design,會依次執行Translate,Map,Place&Route。 圖 3-15 設計實現 3.3.6 下載及硬件仿真選中頂層文件,雙擊運行Generate Programming File,運行后生成相應的(.Bit)下載文件。該文件將下載到芯片中實現設計。 圖 3-16 生成下載文件 再雙擊上圖Configure Device。運行后跳出下載界面,選擇主從下載文式(Slave Serial Mode),點擊完成。 圖 3-17 下載方式 右鍵點擊元件,點擊Program,選擇相應的BIT文件開始下載。 圖 3-18 下載位文件 成功下載后就可以在FPGA板子上運行和測試了。

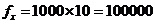

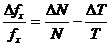

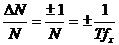

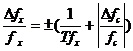

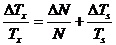

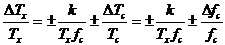

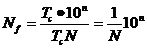

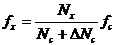

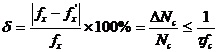

第四章 數字頻率計的設計與實現4.1 任務要求本課題核心任務是完成基于FPGA利用VHDL語言設計一個數字頻率計的設計,仿真,下載實現并實際測量效果,同時要熟悉和掌握Spartan-II這塊板子的各種性能。考慮到是首次接觸VHDL描述語言,并且以前沒有過基于FPGA設計的經驗,所以在完成課題的同時,也不斷的加深對VHDL描述語言的掌握,以及不斷總結由軟件來實現硬件的特點,為以后的工作和更進一步的學習學習打好基礎。除此以外,利用課余時間學習數字頻率計的硬件實現方法,即用MultiSim仿真,PROTEL作原理圖以及PCB板等。數字頻率計的相關技術指標如下: 1、位數:測量頻率通過LED數碼管為六位十進制數顯示。 2、測試頻率范圍為:1Hz~1MHz。擴展1MHz~100MHz。 3、量程分為三檔: 第一檔:最小量程檔,閘門時間為1S時,最大讀數為999.999KHz。 第二檔:閘門時間為0.1S時,最大讀數為9999.99KHz。 第三檔:閘門時間為0.01S時,最大讀數為99999.9KHz。 以上三檔,實際測得的頻率是1Hz~99999.9KHz。顯然完全涵蓋了1Hz~100MHz的范圍。 4、顯示工作方式: a、用BCD七段共陽極數碼管顯示讀數,只有在讀數不發生跳變時才是正確的結果。 b、采用記憶顯示方法,即在一次測試結束時,顯示測試結果,此顯示值一直保留到下次測量顯示數到來,才將上次顯示沖刷更新。用第二次測試結果,更新顯示值。 c、實現對高位無意義零的消隱。 5、要求被測輸入信號應是符合數字電路要求的脈沖波或正弦波。 4.2 測量原理在電子技術領域內,頻率是一個最基本的參數,頻率與其它許多電參量的測量方案、測量結果都有十分密切的關系。因此,頻率的測量就顯得更為重要.而且,目前在電子測量中,頻率的測量精確度是最高的。 4.2.1 頻率或時間的原始基準時間是某一時刻與另一時刻之間的時間長度,這里指的時刻是連續流逝的時間中的一個時點。為了使大家能夠確定出同一時刻,就需要使用共同的時刻標尺來衡量,用這個時刻標尺上的標度來客觀地認識時刻。要計量時間需要有固定不變的時間單位,用秒作為時間的基本單位。如果一秒內的振動數即頻率為已知,則可由此振動數的倒數得到秒的間隔,這就是說單位秒和標準頻率數是互相依存的事物。時刻和時間發展的歷史,集中反映在秒的定義在不斷變遷,秒的準確度不斷提高。 采用天文觀測方法,求得的太陽出現于天頂的平均周期為平均太陽日。將太陽日分為24×60×60份,得到的秒為零類世界時(記作 ),其準確度在 ),其準確度在 量級。地球自轉受到極運動(極移引起的經度變化)的影響,校正了這個偏差而得到的地球自轉的周期,稱為第一世界時(記作 量級。地球自轉受到極運動(極移引起的經度變化)的影響,校正了這個偏差而得到的地球自轉的周期,稱為第一世界時(記作 )。再把地球自轉的季度性、年度性的變化(最大可達0.03秒)校正,就引出了第二世界時(記作 )。再把地球自轉的季度性、年度性的變化(最大可達0.03秒)校正,就引出了第二世界時(記作 )。世界時 )。世界時 經過五十年的觀測,發現其穩定度為 經過五十年的觀測,發現其穩定度為 。這樣,以 。這樣,以 為標準其計時準確度很難優于 為標準其計時準確度很難優于 。 。 為了得到更準確的均勻不變的時間標準,人們以1.900回歸年的31 556 925 9747分之一作為歷書時的秒(記作ET),其準確度可達  左右。  、ET為宏觀計時標準,它需要精密的天文觀測,手續煩雜,準確度有限。 近年來引進了微觀計時標準,這就是利用原子或分子內部能級躍遷所輻射或吸收的電磁波的頻率作為基準來計量時間。采用 ( ( )原子基態的兩個超精細能級之間躍遷所對應的9 192 631 770個周期的持續時間為一秒,以此為標準定出的時間標準稱為原子時(記作AT),其準確度可達 )原子基態的兩個超精細能級之間躍遷所對應的9 192 631 770個周期的持續時間為一秒,以此為標準定出的時間標準稱為原子時(記作AT),其準確度可達 。 。 目前,國際上已經應用經過原子標準修正過的時間來發送時間標準,用原子時來對天文時(  、ET)進行修正。另外,由于頻率是時間的倒數,因此,有了時間標準也就有了頻率標準。 由于數字電路的飛速發展和數字集成電路的普及,電子計數器的應用已十分普及,利用電子計數器測量頻率具有精確度高、使用方便、測量迅速,以及便于實現測量過程自動化等一系列突出優點,故已發展成為近代頻率測量的重要手段。 4.2.2 電子計數器測頻方法目前,絕大多數實驗室用電子計數器都具有測量頻率(測頻)和測量周期(測周)等兩種以上的測量功能,故統稱“通用計數器".各種測量功能可利用《功能選擇》開關加以選擇。 4.2.2.1 電子計數器的測頻原理所謂“頻率”,就是周期性信號在單位時間(一秒)內變化的次數。若在一定時間內計得這個周期信號變化的次數為N,則其頻率可表達:  (4-1) 電子計數器可以嚴格按照公式(4-1)所表達的頻率的定義進行測頻,其原理方框圖如圖 4-1 示: 圖 4-1 測頻原理圖 首先,把被測信號①(以正弦波為例)通過脈沖形成電路轉變成脈沖②(實際上變成方波即可)其重復頻率等于被測頻率 ,然后將它加到閘門的一個輸入端。閘門出門控信號④來控制開、閉時間,只有在閘門開通時間T內,被計數的脈沖⑤才能通過閘門,被送到十進制電子計數器進行計數。門控信號的作用時間T是非常準確的,以它作為時間基準(時基),它由時基發生器提供。時基信號發生一個高穩定的石英振蕩器和一系列數字分頻器組成,由它輸出的標準時間脈沖(時標)去控制門控電路形成門控信號。比如,時標信號的重復周期為1S,則加到閘門的門控信號作用時間T即閘門時間亦準確地等于1s,即閘門開通時間為1s,這時若計得10 000個數,則按式(4-1),被測頻率 ,然后將它加到閘門的一個輸入端。閘門出門控信號④來控制開、閉時間,只有在閘門開通時間T內,被計數的脈沖⑤才能通過閘門,被送到十進制電子計數器進行計數。門控信號的作用時間T是非常準確的,以它作為時間基準(時基),它由時基發生器提供。時基信號發生一個高穩定的石英振蕩器和一系列數字分頻器組成,由它輸出的標準時間脈沖(時標)去控制門控電路形成門控信號。比如,時標信號的重復周期為1S,則加到閘門的門控信號作用時間T即閘門時間亦準確地等于1s,即閘門開通時間為1s,這時若計得10 000個數,則按式(4-1),被測頻率 =10.000Hz,若計數器上單位顯示為“kHz”,則顯示10.000kHz,即小數點定位在第三位。不難設想,若閘門時間改為T=0.1s,則計數值為1 000,這個數乘以10就等于1s的計數值,即 =10.000Hz,若計數器上單位顯示為“kHz”,則顯示10.000kHz,即小數點定位在第三位。不難設想,若閘門時間改為T=0.1s,則計數值為1 000,這個數乘以10就等于1s的計數值,即 Hz。實際上,當改變閘門時間T時,顯示器上的小數點也隨著往右移一位(自動定位),即顯示10.000kHz。 Hz。實際上,當改變閘門時間T時,顯示器上的小數點也隨著往右移一位(自動定位),即顯示10.000kHz。 從以上討論可知,電子計數器的測頻原理實質上以比較法為基礎,它將 和時基信號頻率相比,兩個頻率相比的結果以數字的形式顯示出來。 和時基信號頻率相比,兩個頻率相比的結果以數字的形式顯示出來。 4.2.3 誤差分析下面我們來分析計數器測頻的測量誤差。從公式(4-1)可知,上述測頻方法的測量誤差,一方面決定于閘門時間T準不準,另一方面決定于計數器計得的數準不準。根據誤差合成方法,從公式(4-1)可得:  (4-2) 公式(4-2)中第一項 是數字化儀器所特有的誤差,而第二項 是數字化儀器所特有的誤差,而第二項 是閘門時間的相對誤差,這項誤差決定于石英振蕩器所提供的標準頻率的準確度。現分述如下。 是閘門時間的相對誤差,這項誤差決定于石英振蕩器所提供的標準頻率的準確度。現分述如下。 4.2.3.1 ±1誤差在測頻時,主門的開啟時刻與計數脈沖之間的時間關系是不相關的,所以它們在時間軸上的相對位置是隨機的。這樣,在相同的主門開啟時間內,計數器所計得的數卻不一定相同,當主門開啟時間T接近甚至等于被測信號周期 的整數倍N倍時,此項誤差為最大,圖 4-2 畫出的就是這種情況。 的整數倍N倍時,此項誤差為最大,圖 4-2 畫出的就是這種情況。 圖 4-2 正負1誤差 若主門開啟時刻為 ,而第1個計數脈沖出現在 ,而第1個計數脈沖出現在 ,圖 4-2 (a)中示出了 ,圖 4-2 (a)中示出了 > > >0的情況( >0的情況( ),這時計數器計得N個數(圖中N=6);現在再來看圖 4-2 (b)情況,即 ),這時計數器計得N個數(圖中N=6);現在再來看圖 4-2 (b)情況,即 趨近于0,這就有兩種可能的計數結果:若第1個計數脈沖和第7個計數脈沖都能通過主門,則可計得N+1=7個數;也可能這兩個脈沖都沒有能進入主門,則只能計得N-1=5個數。由此可知,最大的計數誤差為 趨近于0,這就有兩種可能的計數結果:若第1個計數脈沖和第7個計數脈沖都能通過主門,則可計得N+1=7個數;也可能這兩個脈沖都沒有能進入主門,則只能計得N-1=5個數。由此可知,最大的計數誤差為 個數。所以考慮到公式(4-1),可寫成 個數。所以考慮到公式(4-1),可寫成  (4-3) 式中T為閘門時間, 為被測頻率。從公式(4-3)可知,不管計數值N多少,其最大誤差總是±1個計數單位,故稱“±1個字誤差”,簡稱“±1誤差”。而且 為被測頻率。從公式(4-3)可知,不管計數值N多少,其最大誤差總是±1個計數單位,故稱“±1個字誤差”,簡稱“±1誤差”。而且 一定時,增大閘門時間T,可減小±1誤差對測頻誤差的影響。當T選定后, 一定時,增大閘門時間T,可減小±1誤差對測頻誤差的影響。當T選定后, 越低,則由±1誤差產生的測頻誤差越大。 越低,則由±1誤差產生的測頻誤差越大。 4.2.3.2 標準頻率誤差閘門時間T準不準,主要決定于由石英振蕩器提供的標準頻率的準確度,若石英振蕩器的頻率為 ,分頻系數為k,則 ,分頻系數為k,則 而 所以  (4-4) 可見,閘門時間的準確度在數值上等于標準頻率的準確度,式中負號表示由 引起的閘門時間的誤差為 引起的閘門時間的誤差為 。 。 通常,對標準頻率準確度 的要求是根據所要求的測頻準確度提出來的,例如,當測量方案的最小計數單位為1Hz,而 的要求是根據所要求的測頻準確度提出來的,例如,當測量方案的最小計數單位為1Hz,而 = = Hz,在T=1s時的測量準確度為 Hz,在T=1s時的測量準確度為 (只考慮 (只考慮 誤差),為了使標準頻率誤差不對測量結果表明產生影響,石英振蕩器的輸出頻率準確度 誤差),為了使標準頻率誤差不對測量結果表明產生影響,石英振蕩器的輸出頻率準確度 應優于 應優于 ,即比 ,即比 誤差引起的測頻誤差小一個量級。 誤差引起的測頻誤差小一個量級。 4.2.3.3 結論綜上所述,可得如下結論: 1、計數器直接測頻的誤差主要有兩項:即 誤差和標準頻率誤差。一般,總誤差可采用分項誤差絕對值合成,即 誤差和標準頻率誤差。一般,總誤差可采用分項誤差絕對值合成,即  (4-5) 可把公式(4-5)畫成圖 4-3 所示的曲線,即 與T, 與T, 以及 以及 的關系曲線。 的關系曲線。 圖 4-3 誤差曲線 從圖可知, 一定時,閘門時間T選得越長,測量準確度就越高。而當T選定后, 一定時,閘門時間T選得越長,測量準確度就越高。而當T選定后, 越高,則由于 越高,則由于 誤差對測量結果的影響越小,測量準確度就越高。但是,隨著 誤差對測量結果的影響越小,測量準確度就越高。但是,隨著 誤差的減小,標準頻率誤差 誤差的減小,標準頻率誤差 將對測量結果產生影響,并以 將對測量結果產生影響,并以 (圖中以 (圖中以 為例)為極限,即測量準確度不可能優于 為例)為極限,即測量準確度不可能優于 。 。 2、測量低頻時,由于 誤差產生的測頻誤差大得驚人,例如, 誤差產生的測頻誤差大得驚人,例如, 為10Hz,T=1s,則由 為10Hz,T=1s,則由 誤差引起的測頻誤差可達到10%,所以,測量低頻時不宜采用直接測頻方法。 誤差引起的測頻誤差可達到10%,所以,測量低頻時不宜采用直接測頻方法。 4.2.4 測量周期的必要性和基本原理4.2.4.1 測量周期的必要性正如前述,當 較低時,利用計數測器直接測頻,由 較低時,利用計數測器直接測頻,由 誤差所引起的測頻誤差將會大到不可允許的程度。所以,為了提高測量低頻時的準確度,即減小 誤差所引起的測頻誤差將會大到不可允許的程度。所以,為了提高測量低頻時的準確度,即減小 誤差的影響,可改成先測量周期 誤差的影響,可改成先測量周期 ,然后計算 ,然后計算 因為 因為 越低,則越大,計數器計得的數N也越大, 越低,則越大,計數器計得的數N也越大, 誤差對測量結果的影響自然減小。 誤差對測量結果的影響自然減小。 4.2.4.2 測量周期的基本原理計數器測量周期的原理方框圖如圖 4-4 所示。 圖 4-4 測周原理圖 被測信號(正弦)從B輸入端輸入,經脈沖形成電路變成方波,加到門控電路,比如 =10ms則主門打開10ms,在此期間時標脈沖通過主門計數,若選擇時標為 =10ms則主門打開10ms,在此期間時標脈沖通過主門計數,若選擇時標為 則計數器計得的脈沖數等于 則計數器計得的脈沖數等于 / / =10000個,如以ms為單位,則從計數器顯示上可讀得10.000(ms)。 =10000個,如以ms為單位,則從計數器顯示上可讀得10.000(ms)。 從以上討論可知,計數器測周的基本原理剛好與測頻相反,即由被測信號控制主門開門,而用時標脈沖進行計數,所以實質上也是一種比較測量方法。 4.2.4.3 誤差分析與分析電子計數器測頻時的誤差類似,根據誤差傳遞公式,并結合圖 4-4可得:  (4-6) 根據圖 4-4 測周原理  =  所以,公式(4-6)可寫成  (4-7) 從公式(4-7)可見,測量周期時的誤差表達式與測頻的表達式形式相似,很明顯 愈大(即被測頻率愈低), 愈大(即被測頻率愈低), 誤差對測周精確度的影響就愈小。 誤差對測周精確度的影響就愈小。 圖 4-5 示出了測周時的誤差曲線,圖中三條曲線,其中10 和100 和100 兩條線是采用多周期測量(詳后)時的誤差曲線。 兩條線是采用多周期測量(詳后)時的誤差曲線。 圖 4-5 測周時的誤差曲線 4.2.4.4 倒數計數器測量低頻時,首選測量周期,然后求倒數得到被測頻率值,這是減小由 誤差產生頻率誤差的一種有效方法。但是,這種方法不能直接讀出頻率值,而需要通過1/ 誤差產生頻率誤差的一種有效方法。但是,這種方法不能直接讀出頻率值,而需要通過1/ 求倒數才得到頻率值。 求倒數才得到頻率值。 眾所周知,數字電路也可以完成數字運算,所謂倒數計數器,就是這種計數器:首先測量周期,然后自動計算并顯示被測頻率。圖 4-6 示出了一種倒數計數器的簡化方框圖。 圖 4-6 倒數計數器 主門I和計數器I工作在測周模式,即輸入頻率 經觸發器加工,形成門控信號 經觸發器加工,形成門控信號 ,在 ,在 時間內主門開啟,時鐘通過主門I計數,計得 時間內主門開啟,時鐘通過主門I計數,計得 ( ( 被測信號的周期,而 被測信號的周期,而 為時鐘周期)。N作為定標器的預置值,即將定標器預置到 為時鐘周期)。N作為定標器的預置值,即將定標器預置到  。定標器實質上起分頻作用,時鐘通過門Ⅲ由定標器計數,當計完N個時鐘后,計數器溢出并輸出一個進位脈沖,即每計完N個時鐘輸出一個脈沖,故定標器輸出頻率為 。定標器實質上起分頻作用,時鐘通過門Ⅲ由定標器計數,當計完N個時鐘后,計數器溢出并輸出一個進位脈沖,即每計完N個時鐘輸出一個脈沖,故定標器輸出頻率為 或周期為 或周期為 ,后者通過主門Ⅱ計數,主門Ⅱ的閘門時間為 ,后者通過主門Ⅱ計數,主門Ⅱ的閘門時間為 ,計數器計得的數為 ,計數器計得的數為  (4-8) 測周模式計得的數為  (4-9) 從公式(4-8)和公式(4-9)可見,計數器II計得的數 正比于N的倒數,從而完成了倒數的運算,也就是說,可從計數器II上直接讀被測頻率 正比于N的倒數,從而完成了倒數的運算,也就是說,可從計數器II上直接讀被測頻率 ,其顯示的位數由分頻系數 ,其顯示的位數由分頻系數 而定。將公式(4-9)代入公式(4-8)可得 而定。將公式(4-9)代入公式(4-8)可得  (4-10) 從公式(4-10)可見,主門II和計數器II實際上工作在測頻模式,其輸入頻率就是 (注意:由于測周期模式計得的數N本身存在 (注意:由于測周期模式計得的數N本身存在 誤差,故嚴格來講輸入頻率并非準確地等于 誤差,故嚴格來講輸入頻率并非準確地等于 ),且工作在同步計數方式,即加到主門II的 ),且工作在同步計數方式,即加到主門II的 和 和 同步。由于同步計數不會產生 同步。由于同步計數不會產生 誤差,所以,倒數計數器的誤差與測周模式誤差相同。 誤差,所以,倒數計數器的誤差與測周模式誤差相同。 4.2.5 等精度測量目前,有三種常用的數字頻率的測量方法:直接測頻法(以下簡稱M法),直接測周法(以下簡稱T法)和綜合測量法(即相結合的方法,以下簡稱為M/T法)。前兩種測量法的原理,在上面的實驗原理里面已經詳細的討論了,不再累述。這兩種方法由誤差分析可知,其精度都與被測信號的有關,因而它們是非等精度測量法。而M/T法它通過測量被測信號數個周期的時間,然后換算得出被測信號的頻率,克服了測量精度對被測信號的依賴性。 M/T法的核心思想是通過閘門信號與被測信號同步,將閘門時間τ控制為被測信號周期長度的整數倍。測量時,先打開預置閘門,當檢測到被測信號脈沖沿到達時,標準信號時鐘開始計數。預置閘門關閉時,標準信號并不立即停止計數,而是等檢測到被測信號脈沖沿到達時才停止,完成被測信號整數個周期的測量。測量的實際閘門時間可能會與預置閘門時間不完全相同,但最大差值不會超過被測信號的一個周期。M/T法測量原理如下圖所示。 圖 4-7 同步計數 不如令實際閘門時間為τ,被測信號周期數為 ,標準信號頻率為 ,標準信號頻率為 ,計數值為 ,計數值為 ,則被測信號的頻率值為: ,則被測信號的頻率值為:  (4-11) 由于實際閘門時間τ是由被測信號同步過的,因此在此期間測得的被測信號周期的整數倍 是準確的,不存在 是準確的,不存在 誤差。而標準信號的計數值 誤差。而標準信號的計數值 則存在 則存在 誤差。用 誤差。用 來表則標準信號計數的真實值為 來表則標準信號計數的真實值為 + + 。由此可知被測信號的頻率真實值為: 。由此可知被測信號的頻率真實值為:  (4-12) 若不計標準信號時鐘的誤差,則測量的相對誤差為:  (4-15) 可以看出,在M/T法中,相對誤差與被測信號本身的頻率特性無關,即對整個測量域而言,測量精度相等,因而稱之為“等精度測量”。標準信號的計數值 越大則測量相對誤差越小,即提高門限時間τ和標準信號頻率 越大則測量相對誤差越小,即提高門限時間τ和標準信號頻率 可以提高測量精度。在精度不變的情況下,提高標準信號頻率可以縮短門限時間,提高測量速度。原理圖如下: 可以提高測量精度。在精度不變的情況下,提高標準信號頻率可以縮短門限時間,提高測量速度。原理圖如下: 圖 4-8 同等度測量的原理圖 計數控制器將標準信號分頻為預置信號,預置閘門信號與被測信號作用同步之后輸出實際閘門信號,作為周期計數器和脈沖計數器的計數使能信號。同時在實際閘門信號關斷的時間里,計數控制器產生一個清數脈沖,用以清除計數器內的計數值,以備下一次計數,該清零脈沖同時還作為一次計數結束后,將計數值進行計算,譯碼顯示的鎖存信號,不然,數碼管的顯示將因為數值的不停跳動而無法看清楚。 運算器則通過不停地做除法運算實現被測信號頻率值的計算,顯示譯碼器在收到被測信號頻率值后,將該值轉換為七段碼數據顯示的形式,并按照動態掃描方式依次定時先通各個顯示管,將顯示數值送出,由于人眼的暫留效應,就可以看到穩定的輸出值了。 4.3 原理框圖圖 4-9 原理框圖 4.4 各模塊的功能及實現4.4.1 分頻器分頻器的功能是提供標準閘門時間控制信號以精確控制計數器的開閉。由于閘門時間只有1S,0.1S,0.01S三檔,由于本設計將下載到Spartan-II上,其提供的標準時間是32MHz,為此,我們想到了計數器。對一個兩位的二進制計數器,當輸入兩個脈沖時,其輸出進位脈沖為1個,即入/出之比為2比1。如此下推,對輸出為2位、3位、4位、5位的二進制計數則其輸入/輸出為1﹕4,1﹕8,1﹕16,1﹕32……。但十進制例外,輸出雖為四位,但輸入/輸出比為1﹕10。這是因為在此,計數器到9時,但產生了進位。 如果我們采用一個32進制的計數器和六個十進制計數器串行連接,那么,我們在最后的三級上,可分別獲得100Hz,10Hz、1Hz、其閘門時間分別為0.01s、0.1s、1s的控制信號。生成的分頻器模塊如下圖所示: 圖 4-10 分頻器模塊 程序中使用了隸屬函數generic, Generic ( rate : integer :=10 );定義了一個整形變量rate,通過修改這個整形變量rate的值,可以實現分頻器分頻數的改變。這樣做可以實現程序的調用,只需要修改少量的地方就可以實現不同的分頻需要。 源程序如下: library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity fdiv is Generic ( rate : integer :=10 ); Port ( f_in : In std_logic; f_out : Out std_logic ); end; architecture behavioral of fdiv is signal cnt : integer range 0 to rate := 0; signal clk : std_logic:='0'; begin process (f_in) begin if f_in'event and f_in = '1' then if cnt /= rate then cnt <= cnt + 1; else cnt <= 1; clk<=not clk; end if; end if; end process; f_out <= clk; end behavioral; 仿真圖如下所示: 圖 4-11 分頻器模塊仿真圖 運用component函數對上面程序的調用,即可很輕松的實現幾個分頻器,而不用再寫類似的程序。生成的模塊如圖所示: 圖 4-12 多輸出的分頻器 這個模塊即實現了把32MHz的時基信號分成了我們需要的四個信號1Hz,10Hz,100Hz,1KHz。其源程序如下: library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity Fdiv3 is Port ( clkin : in std_logic; clkout1 : out std_logic; clkout10 : out std_logic; clkout100 : out std_logic; clkout1k : out std_logic); end Fdiv3; architecture structure of Fdiv3 is component fdiv is Generic ( rate : integer :=10 ); Port ( f_in : In std_logic; f_out : Out std_logic ); end component fdiv; signal carry1,carry2,carry3:std_logic; begin U1:fdiv generic map(rate=>16000) port map (f_in=>clkin,f_out=>carry1); U2:fdiv generic map(rate=>5) port map (f_in=>carry1,f_out=>carry2); U3:fdiv generic map(rate=>5) port map (f_in=>carry2,f_out=>carry3); U4:fdiv generic map(rate=>5) port map (f_in=>carry3,f_out=>clkout1); clkout1K <= carry1; clkout100 <= carry2; clkout10<=carry3; end structure; 4.4.2 閘門選擇器該模塊的功能是實現對輸入的幾個閘門信號的手動選擇,并輸出被選中的閘門信號以及小數點的控制信號DP1,DP2,DP3。生成的模塊如下圖所示: 圖 4-13 閘門選擇器 該模塊有六個輸入端口,其中se1,se10,se100為選擇使能端,f1hz,f10hz,f100hz為被選時基信號輸入端。當se1為1時,f1hz的輸入時基信號被選中,被賦值給輸出端口fref輸出,此時DP1有效,DP2和DP3無效,點亮DP1連接的小數點;當se1為0,se10為1時,f10hz時基信號被選中,DP2有效,DP1和DP3無效,點亮由DP2連接的小數點;最后當se1和se10都無效時,即都為0時,se100為1時,f100hz端口的輸入信號被選中作為輸出,DP3有效,DP1和DP2無效,點亮由DP3連接的小數點。 本模塊的源程序如下: library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity sele is port(se1,se10,se100: in std_logic; f1hz,f10hz,f100hz: in std_logic; fref: out std_logic; dp1,dp2,dp3: out std_logic); end sele; architecture Behavioral of sele is begin process (se1,se10,se100,f1hz,f10hz,f100hz) begin fref <= '0'; dp1 <= '0';dp2 <= '0';dp3 <= '0'; if se1 = '1' then fref <= f1hz; dp1<= '1'; elsif se10 = '1' then fref <= f10hz; dp2 <= '1'; elsif se100 = '1' then fref <= f100hz; dp3 <='1'; end if; end process; end Behavioral; 1

第四章 數字頻率計的設計與實現 仿真圖如下所示: 圖 4-14 閘門選擇器仿真圖 4.4.3 測頻控制器測頻控制器是控制整個頻率計各模塊進行時序工作的控制裝置,它對輸入的標準時鐘信號進行變換,產生我們所需要的三個信號閘門信號GATE,鎖存信號LATCH以及清零信號CLEAR。如使用一個低觸發器處理1Hz的時鐘信號,其Q端輸出,即是脈寬1S計數器使能端的控制信號,而 輸出即為脈寬1S的鎖存器使能信號。計數清零信號也由測頻控制器變換后輸出,控制整個電路。其生成的元件符號如下圖所示: 輸出即為脈寬1S的鎖存器使能信號。計數清零信號也由測頻控制器變換后輸出,控制整個電路。其生成的元件符號如下圖所示: 圖 4-15 測頻控制器 測頻控制信號發生器設計要求:頻率測量的基本原理是計算每秒鐘內待測信號的脈沖個數。這就要求Control的計數使能信號Gate能產生一個周期信號,并對頻率計的每一計數器Counter6的Carry_in使能端進行同步控制。當Gate為高電平時,允許計數,為低電平時停止計數,并保持其所計的脈沖數。在停止計數期間,首先需要一個鎖存信號latch的上跳沿將計數器在前1秒鐘的計數值鎖存進24位鎖存器Latch中,并由外部的7段譯碼器譯出,并穩定顯示。設置鎖存器的好處是,顯示的數據穩定,不會由于周期性的清零信號而不斷閃爍。鎖存信號之后,必須有一清零信號Reset對計數器進行清零,為下1秒鐘的計數操作準備。源程序如下: library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity control is Port ( Bsignal : in std_logic; Gate : out std_logic; Reset : out std_logic; latch : out std_logic); end control; architecture Behavioral of control is signal G1,G2: std_logic:='0'; begin process(Bsignal,G1) begin if rising_edge(Bsignal) then G1<=not G1; end if; if falling_edge(bsignal) then G2<=not G1; end if; end process; gate<=G1; latch<=G2; reset<=(not bsignal)and(not G1)and (G2); end Behavioral; 測頻控制信號發生器的仿真工作時序如圖所示。 圖 4-16 測頻控制器的仿真圖 如果閘門信號Gate的頻率取1Hz,那么信號Gate的脈寬恰好為1S,可以用作計數閘門信號。然后根據測頻的時序要求,可得出信號latch和Reset的邏輯描述。由圖可見,在計數完成后,即計數使能信號Gate在1S的高電平后,利用其反相值產生一個鎖存信號latch,由于反相器的器件延時,鎖存信號的上升沿是在計數使能信號即閘門信號Gate的下降沿之后,即是計數完了才鎖存的,符合我們的設計要求。而清零信號Reset的上升沿的產生是在下一個Gate信號上升沿來臨之前,也就是說是清了零才開始計數的,不是計了一會兒數再被清零了繼續計數,這也是與我們的設計要求相符合的。高質量的測頻控制信號發生器的設計十分重要,設計中要對其進行仔細的實時仿真,防止可能產生的毛刺。 4.4.4 頻率計數器由于要求頻率計的顯示為十進制六位,所示我們設計的是使能端的十進制計數器,所生成的模塊如圖所示:其中RST是清零端,CLK是計數信號輸入端,Carry_in是計數保持端,即為高電平時計數,低電平時停止計數保持計數不變。Count_out是計數結果輸出,carry_out是進位信號。 圖形 4-17 單個計數器模塊 其源程序為: library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity counter is port (rst,clk : in std_logic; carry_in : in std_logic; carry_out : out std_logic; count_out : out std_logic_vector(3 downto 0)); end counter; architecture Behavioral of counter is signal count: std_logic_vector(3 downto 0):="0000"; begin process(rst,clk) begin if rst='1' then count <= "0000"; elsif clk'event and clk= '1' then if carry_in = '1' then if count < "1001" then count <= count+1; else count <= "0000"; end if; else null; end if; end if; end process; count_out<=count; carry_out <= '1' when carry_in = '1' and count = "1001" else '0'; end Behavioral; 仿真圖如下圖所示: 圖 4-18 單個計數器的仿真圖 由仿真圖可以看出,程序的綜合出來的這個計數器的確實現我們預定的要求。有清零端和保持端,通過對計數器的級聯就可以實現十進制六位數的計數。 被測信號接至此計數器的Csignal。清零端clear和保持端count_en分別與測頻控制器Reset端和閘門信號Gate相對接。計數器輸出端與鎖存器輸入端對接,而進位輸出端則依次接到下一位計數器的保持端cout_en,惟第六位即最高位的進位輸出作為溢出標志用over來表示,用以顯示計數器計數是否溢出,溢出了就更換大一級的檔位。這樣的級聯形成了同步計數,是一種計數較快的級聯方式,生成的原理模塊如下: 圖 4-19 級聯后的計數器 計數器模塊級聯的程序跟頻率計級聯程序雷同,這里不再貼出,有興趣的朋友可以參考附錄。級聯成六位計數器的仿真圖如下: 圖 4-20 六位計數器的仿真圖 4.4.5 鎖存器如果計數器輸出直接與譯碼器相連接,那么在計數過程中輸出端則隨輸入脈沖數的增加而不斷跳變,那么顯示數碼管則也會不斷閃爍跳變,讓人不能看到穩定的輸出,設鎖存器后,則不再跳變,便可清晰讀出計數結果。由control控制模塊產生的latch信號來提供鎖存脈沖。其生成的功能模塊如圖所示: 圖 4-21 鎖存器模塊 這模塊實現了對六位計數結果和溢出信號over的鎖存功能。程序很簡單,即鎖存信號的上升沿來時送數,其它時候則保持不變。具體程序參考附錄。 4.4.6 掃描顯示控制譯碼系統本模塊通過用一個頻率1KHz的信號來掃描一個多路選擇器,實現對六位已經鎖存的計數結果的掃描輸出,由于1KHz相對了人眼的暫留效應已經很高了,所以顯示結果不會讓人感覺到閃爍。這樣就可以用一個譯碼器來實現對六個4位二進制數的譯碼。譯碼結果再連接到一個多路選擇器的輸入端,同樣由1KHz的信號來同步掃描選通。同時本模塊還實現了無意義零的消隱。最出的輸出全部通過下載前的固定引腳連接到LED顯示管上。實現最終結果的數字顯示。輸入端包括掃描信號1KHz,由前面產生在本模塊起控制作用的溢出信號Q_over,小數點指示信號Dp1,Dp2以及鎖存器的輸出結果。

其生成模塊如下: 圖 4-22 顯示譯碼控制模塊 其源程序如下: - library IEEE;

- use IEEE.STD_LOGIC_1164.ALL;

- use IEEE.STD_LOGIC_ARITH.ALL;

- use IEEE.STD_LOGIC_UNSIGNED.ALL;

- entity multi is

- port(f1khz,q_over : in std_logic;

- dp1,dp2 : in std_logic;

- freq_value0,freq_value1 : in std_logic_vector(3 downto 0);

- freq_value2,freq_value3 : in std_logic_vector(3 downto 0);

- freq_value4,freq_value5 : in std_logic_vector(3 downto 0);

- out0,out1,out2,out3,out4,out5: out std_logic_vector(6 downto 0));

- end multi;

- architecture Behavioral of multi is

- signal sel : std_logic_vector(2 downto 0):="000";

- signal hide : std_logic;

- signal data : std_logic_vector(3 downto 0);

- signal led : std_logic_vector(6 downto 0);

- begin

- scan : process (f1khz)

- begin

- if rising_edge(f1khz) then

- if sel = "101" then

- sel <= "000";

- else

- sel <= sel + 1;

- end if;

- end if;

- end process;

- mux:process(sel,freq_value0,freq_value1,freq_value2,freq_value3,freq_value4,freq_value5)

- begin

- case sel is

- when "000" => data <= freq_value0;

- when "001" => data <= freq_value1;

- when "010" => data <= freq_value2;

- when "011" => data <= freq_value3;

- when "100" => data <= freq_value4;

- when others => data <= freq_value5;

- end case;

- end process;

- bcd2led : process (hide,data)

- begin

- led <= "1111111";

- if hide /= '1' then

- case data is

- when "0000" => led <= "0000001";

- when "0001" => led <= "1001111";

- when "0010" => led <= "0010010";

- when "0011" => led <= "0000110";

- when "0100" => led <= "1001100";

- when "0101" => led <= "0100100";

- when "0110" => led <= "0100000";

- when "0111" => led <= "0001111";

- when "1000" => led <= "0000000";

- when "1001" => led <= "0000100";

- when others => null;

- end case;

- end if;

- end process;

- fenpei:process(sel,led)

- begin

- out0<="1111111";

- out1<="1111111";

- out2<="1111111";

- out3<="1111111";

- out4<="1111111";

- out5<="1111111";

- case sel is

- when "000" => out0 <= led;

- when "001" => out1 <= led;

- when "010" => out2 <= led;

- when "011" => out3 <= led;

- when "100" => out4 <= led;

- when "101" => out5 <= led;

- when others => null;

- end case;

- end process;

- hide_zero:process (sel,q_over,dp1,dp2,freq_value5,freq_value4,freq_value3,freq_value2)

- begin

- hide <= '0';

- case sel is

- when "101" =>

- if q_over = '0' and freq_value5 = "0000"

- then hide <= '1';

- end if;

- when "100" =>

- if q_over = '0' and freq_value5 = "0000"

- and freq_value4 = "0000"

- then hide <= '1';

- end if;

- when "011" =>

- if q_over = '0' and freq_value5 = "0000"

- and freq_value4 = "0000"

- and freq_value3 = "0000"

- and dp1 /= '1'

- then hide <= '1';

- end if;

- when "010" =>

- if q_over = '0' and freq_value5 = "0000"

- and freq_value4 = "0000"

- and freq_value3 = "0000"

- and freq_value2 = "0000"

- and dp1 /= '1'

- and dp2 /= '1'

- then hide <= '1';

- end if;

- when others =>

- null;

- end case;

- end process;

- end Behavioral;

仿真結果如下: 圖 4-23 顯示譯碼控制模塊的仿真圖 4.5 頂層原理圖將各程序生成的模塊按我們的要求連接就形成了頂層原理圖。再定義好輸入輸出引腳,就可以做最后的綜合和設計實現了。原理圖過大,可參考附錄。 以下是最后的仿真,第一個是局部的放大,第二個仿真結果的整體。在仿真圖上可以看出程序的綜合的確達到了我們的要求。能清零,小數點隨著閘門的變化而變化,正確顯示是否溢出,以及成功的計數和譯碼顯示。 圖 4-24 頂層原理圖仿真的局部放大 圖 4-25 頂層原理圖仿真圖整體 4.6 分配引腳和下載實現全部仿真通過后,就運行ISE的設計實現,然后再打開XILINX PACE,在里面分配引腳,即實現設計的輸入輸出端口與實際芯片的輸入輸出端口的對應連接。比如七段LED管的控制信號就連接到實際電路的七個引腳。需要注意的是一些端口是固定的,不能胡亂的連接。比如時基信號即石英振蕩器所提供的信號就只能由P181輸入。同時還要考慮內部的可配制邏輯塊CLB的數量是否夠滿足程序的綜合要求。一切都準備就緒后就可以運行Configure Device,選擇要下載的位文件(.bit)便可開始下載了。 4.7 測試結果在成功下載并運行后,為評估該設計系統的實際測量效果,做了一次對比實驗,選用頻率可調的函數發生器SP1641B,同時用示波器TDS210 Tektronix做同步的跟蹤。測得的數據很精確,跟函數發生器以及示波器的顯示全吻合。最低頻率可以測到1Hz,不過要求輸入信號很穩定且為方波,因為芯片輸入端口自帶的整形電路能力畢竟有限。在做高頻的對比測量時,波形發生器換成了Agilent公司生產的4410做信號源。結果表明該設計的確能測量到100MHz,測量結果表明該設計達到了最初的提出的所有設計要求。

第五章 結論本文主要介紹了利用VHDL語言完成基于FPGA的數字頻率計的設計與實現。詳細介紹了測量原理,設計方案以及各模塊的設計過程及其實現的功能,并對設計中遇到的問題作了分析和處理;利用ISE和ModelSim對設計進行了仿真,分析,綜合,并最終下載到Spartan-II系列芯片中,實現了對頻率的測量。 傳統數字頻率計由于在高頻段受基準時鐘頻率的限制,其測頻精度受到很大的限制.本設計應用EDA技術,很好的解決了這一問題.在設計完成后,為評估系統的實際測量效果,做了一次對比實驗,測量結果表明測量精度基本能達到 ,可滿足一般測量精度的要求。但當被測信號頻率較低時,測試精度較低,誤差變大。究其原因,除了數字測量本身的正負 ,可滿足一般測量精度的要求。但當被測信號頻率較低時,測試精度較低,誤差變大。究其原因,除了數字測量本身的正負 誤差和標準信號引起的誤差外,還發現低頻信號的上升沿和下降沿的變化較緩慢,影響了計數器的計數值,造成了測量精度的下降。 誤差和標準信號引起的誤差外,還發現低頻信號的上升沿和下降沿的變化較緩慢,影響了計數器的計數值,造成了測量精度的下降。 這是第一次利用HDL語言來實現基于FPGA的實際工程項目,所以在實踐過程中不可避免的遇到了很多問題以及設計中一些不足的地方。理論和實踐沒有有機的聯系起來,理論沒有起到應有的指導作用。如本來可以實現測量檔位的自動切換。同時受到FPGA板子本身的限制(小數點不受控于芯片I/O的輸出信號),小數點的變化只能由另外的LED來體現。

附錄1. 計數器級聯程序 - library IEEE;

- use IEEE.STD_LOGIC_1164.ALL;

- use IEEE.STD_LOGIC_ARITH.ALL;

- use IEEE.STD_LOGIC_UNSIGNED.ALL;

- entity counter6 is

- port(Csignal : in std_logic;

- clear : in std_logic;

- count_en : in std_logic;

- over : out std_logic;

- result1 : out std_logic_vector(3 downto 0);

- result2 : out std_logic_vector(3 downto 0);

- result3 : out std_logic_vector(3 downto 0);

- result4 : out std_logic_vector(3 downto 0);

- result5 : out std_logic_vector(3 downto 0);

- result6 : out std_logic_vector(3 downto 0));

- end counter6;

- architecture structure of counter6 is

- component counter is

- port(rst,clk : in std_logic;

- carry_in : in std_logic;

- carry_out : out std_logic;

- count_out : out std_logic_vector(3 downto 0));

- end component counter;

-

- signal carry1,carry2,carry3,carry4,carry5,carry6: std_logic;

- signal over1 :std_logic;

- begin

- U1 : counter Port map ( rst => clear,

- clk => Csignal,

- carry_in => count_en,

- carry_out => carry1,

- count_out => result1 );

- U2 : counter Port map ( rst => clear,

- clk => Csignal,

- carry_in => carry1,

- carry_out => carry2,

- count_out => result2 );

- U3 : counter Port map ( rst => clear,

- clk => Csignal,

- carry_in => carry2,

- carry_out => carry3,

- count_out => result3 );

- U4 : counter Port map ( rst => clear,

- clk => Csignal,

- carry_in => carry3,

- carry_out => carry4,

- count_out => result4 );

- U5 : counter Port map ( rst => clear,

- clk => Csignal,

- carry_in => carry4,

- carry_out => carry5,

- count_out => result5 );

- U6 : counter Port map ( rst => clear,

- clk => Csignal,

- carry_in => carry5,

- carry_out => carry6,

- count_out => result6 );

- process (clear,csignal)

- begin

- if clear = '1' then

- over1<= '0';

- elsif rising_edge(csignal) then

- over1 <= carry6 or over1;

- end if;

- end process;

- over<=over1;

- end structure;

附錄2. 鎖存器源程序- library IEEE;

- use IEEE.STD_LOGIC_1164.ALL;

- use IEEE.STD_LOGIC_ARITH.ALL;

- use IEEE.STD_LOGIC_UNSIGNED.ALL;

- entity latch is

- port ( latchin : in std_logic;

- overin : in std_logic;

- numin1 : in std_logic_vector(3 downto 0);

- numin2 : in std_logic_vector(3 downto 0);

- numin3 : in std_logic_vector(3 downto 0);

- numin4 : in std_logic_vector(3 downto 0);

- numin5 : in std_logic_vector(3 downto 0);

- numin6 : in std_logic_vector(3 downto 0);

- overout : out std_logic;

- numout1 : out std_logic_vector(3 downto 0);

- numout2 : out std_logic_vector(3 downto 0);

- numout3 : out std_logic_vector(3 downto 0);

- numout4 : out std_logic_vector(3 downto 0);

- numout5 : out std_logic_vector(3 downto 0);

- numout6 : out std_logic_vector(3 downto 0));

- end latch;

- rchitecture Behavioral of latch is

- begin

- process(latchin)

- begin

- if rising_edge(latchin) then

- overout<=overin;

- numout1<=numin1;

- numout2<=numin2;

- numout3<=numin3;

- numout4<=numin4;

- numout5<=numin5;

- numout6<=numin6;

- end if;

- end process;

- end Behavioral;

附錄3. 頂層原理圖

附錄4. 計數器的級聯圖

完整的Word格式文檔51黑下載地址:

數字式頻率計的設計過程,其中包含了所用到的VHDl語言的源代碼,和仿真圖型.rar

(1.77 MB, 下載次數: 41)

數字式頻率計的設計過程,其中包含了所用到的VHDl語言的源代碼,和仿真圖型.rar

(1.77 MB, 下載次數: 41)

2019-1-22 16:08 上傳

點擊文件名下載附件

|