Ŀ�

һ�� �O(sh��)Ӌ(j��)�΄�(w��)�cҪ�� 3

�����O(sh��)Ӌ(j��)˼· 4

1.1�O(sh��)Ӌ(j��)���� 4

1.2�O(sh��)Ӌ(j��)Ҫ�c(di��n) 4

1.3����ԭ�� 4

���������\(y��n)��Y(ji��)�� 5

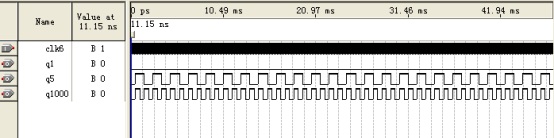

��1�����lģ�K 5

��2����ģ�K 6

��3����ģ�K��minute�� 8

��4���r(sh��)ģ�K��hour�� 10

��5����(sh��)�a�@ʾ�(q��)��(d��ng)ģ�K 12

(6)Ƭ�xģ�K��sell�� 13

(7)�g�a�@ʾģ�K(display) 14

��8����(b��o)�r(sh��)ģ�K��alart�� 15

��9�����M(j��n)��Ӌ(j��)��(sh��)��ģ�K��cnt6�� 16

��10����ݔ���cģ�K��and2a�� 17

��11����ݔ���ģ�K(or2a) 18

�ġ�플��·�O(sh��)Ӌ(j��)������Y(ji��)���c���� 19

�塢�ĵ��w��(hu��) 22

���������īI(xi��n) 23

�ߡ� Դ���� 23

ժҪ�������(l��i)�S����(sh��)�ּ��g(sh��)��Ѹ�ٰl(f��)չ�����N�С���Ҏ(gu��)ģ�����·�ڔ�(sh��)��ϵ�y(t��ng)������ϵ�y(t��ng)����̖(h��o)̎���ȷ��涼�õ��ˏV���đ�(y��ng)�á��@������Ҫ�������ƴ�W(xu��)����Ϥ�����ճ����С���Ҏ(gu��)ģ�����·���ܼ����ڌ�(sh��)�H�еđ�(y��ng)�÷�������ͨ�^(gu��)��(sh��)�(y��n)�̌W(xu��)���B(y��ng)��(sh��)���·�Ļ�����(sh��)�(y��n)������������(w��n)�}���ϙz�鷽���Լ��pۙʾ�����ȳ��Ãx��ʹ�÷����Ȼ����·�Ļ�����(sh��)�(y��n)�����⣬߀������B(y��ng)��W(xu��)�������O(sh��)Ӌ(j��)�ͽM����(sh��)�(y��n)?z��i)����?/font>

�����O(sh��)Ӌ(j��)��Ŀ���������B(y��ng)�W(xu��)����(du��)�����·�đ�(y��ng)�ú����գ�ʹ�W(xu��)���ڌ�(sh��)�(y��n)ԭ����ָ��(d��o)�£������߂�����·�ķ������O(sh��)Ӌ(j��)�������������䑪(y��ng)�÷��������ДM����(sh��)�(y��n)���E���z����ų����� ��������̎�팍(sh��)�(y��n)�Y(ji��)������(xi��)��(sh��)�(y��n)��(b��o)����������C�ό�(sh��)�(y��n)���O(sh��)Ӌ(j��)Ŀ�������B(y��ng)�W(xu��)����������С�͔�(sh��)��ϵ�y(t��ng)���O(sh��)Ӌ(j��)�����������x���O(sh��)Ӌ(j��)�������M(j��n)���·�O(sh��)Ӌ(j��)�����b���{(di��o)ԇ�ȭh(hu��n)��(ji��)���\(y��n)�����W(xu��)֪�R(sh��)�M(j��n)�й����O(sh��)Ӌ(j��)����ߌ�(sh��)�(y��n)���ܵČ�(sh��)�`����(sh��)��������һ�NӋ(j��)�r(sh��)�b�ã������Еr(sh��)���֡���Ӌ(j��)�r(sh��)���ܺ��@ʾ�r(sh��)�g���ܣ��������c(di��n)��(b��o)�r(sh��)���ܡ� �����O(sh��)Ӌ(j��)�Ҳ���˴������īI(xi��n)�Y�ϣ��W(xu��)���˺ܶ��P(gu��n)�ڔ�(sh��)���·�����֪�R(sh��)�����Ҹ���얹̺��������n�������W(xu��)���n��֪�R(sh��)��ʹ�Լ���(du��)��(sh��)����Ӽ��g(sh��)���˸��M(j��n)һ�����J(r��n)�R(sh��)���˽⡣ - �O(sh��)Ӌ(j��)�΄�(w��)�cҪ��

�������ܣ����M(j��n)�������ĕr(sh��)���֡���Ӌ(j��)�r(sh��)���ܣ��քe��6��(g��)��(sh��)�a���@ʾ24С�r(sh��)��60��犣�60��犵�Ӌ(j��)��(sh��)���@ʾ�� ���ӹ��ܣ�1��������Ӳ�����ְ��I��(sh��)�F(xi��n)��У�r(sh��)����У�֡������㡱���ܣ� 2�������÷��Q�������c(di��n)��(b��o)�r(sh��)����(d��ng)Ӌ(j��)�r(sh��)���_(d��)59��59�����r(sh��)�_(k��i)ʼ��(b��o)�r(sh��)���Q�Еr(sh��)�g1��犣� 3�����r(sh��)�[⏣����O(sh��)Ӌ(j��)���O(sh��)�õ��������c(di��n)�r(sh��)�M(j��n)���[犹��ܣ��Q���^(gu��)���У��܉��M(j��n)���Д��[⏹����� �����O(sh��)Ӌ(j��)˼· 1.1�O(sh��)Ӌ(j��)���� 1���r(sh��)犹��ܣ������@ʾ�r(sh��)���֡���Ĺ��ܣ� 2���������c(di��n)��(b��o)�r(sh��)���ܣ������c(di��n)�r(sh��)ʹ�÷��Q���M(j��n)�Ј�(b��o)�r(sh��)�������[犹��ܣ��Q���^(gu��)���У������Д��[⏹��ܡ� 1.2�O(sh��)Ӌ(j��)Ҫ�c(di��n) ��(sh��)���һ��������ʎ�������l����Ӌ(j��)��(sh��)�����g�a�����@ʾ���Ȏײ��ֽM�ɡ��@Щ���ǔ�(sh��)���·�Б�(y��ng)����V���Ļ����·�����O(sh��)Ӌ(j��)��ģ�K�O(sh��)Ӌ(j��)��(sh��)�F(xi��n)�����ֹ��ܣ�����ܛ�����̿���FPGAоƬ��(n��i)���a(ch��n)�����(d��ng)���ڞ�1s���}�_��������̖(h��o)����Ӌ(j��)��(sh��)���M(j��n)��Ӌ(j��)�㣬�����ۼӵĽY(ji��)���ԡ��r(sh��)�������֡������롱�Ĕ�(sh��)���@ʾ����(l��i)�����롱���@ʾ�Ƀɼ�(j��)Ӌ(j��)��(sh��)�����g�a���M�ɵ���ʮ�M(j��n)��Ӌ(j��)��(sh��)�·��(sh��)�F(xi��n)�����֡����@ʾ�·���롱��ͬ�����r(sh��)�����@ʾ�Ƀɼ�(j��)Ӌ(j��)��(sh��)�����g�a���M�ɵĶ�ʮ���M(j��n)���·��(l��i)��(sh��)�F(xi��n)������Ӌ(j��)�r(sh��)�Y(ji��)������λ��(sh��)�a���@ʾ�� 1.3����ԭ�� ��(sh��)����������ʎ�������l�� Ӌ(j��)��(sh��)�����g�a�@ʾ����(b��o)�r(sh��)���·�M�ɡ���ʎ���a(ch��n)����(w��n)���ĸ��l�}�_��̖(h��o)�����锵(sh��)��犵ĕr(sh��)�g����(zh��n)��Ȼ��(j��ng)�^(gu��)���l��ݔ����(bi��o)��(zh��n)���}�_����Ӌ(j��)��(sh��)���M60�����Ӌ(j��)��(sh��)���M(j��n)λ����Ӌ(j��)��(sh��)���M60����С�r(sh��)Ӌ(j��)��(sh��)���M(j��n)λ��С�r(sh��)Ӌ(j��)��(sh��)�����ա�24��1��Ҏ(gu��)��Ӌ(j��)��(sh��)��Ӌ(j��)�M���Ӌ(j��)��(sh��)�����㣬����Ӌ(j��)��(sh��)��Ӌ(j��)��(sh��)����ݔ���քe��(j��ng)�g�a���͔�(sh��)�a���@ʾ��Ӌ(j��)�r(sh��)���F(xi��n)�`��r(sh��)��������У�r(sh��)�·��У�r(sh��)����У�֡������㡱�����}�_����ͨ�^(gu��)���l�·�õ���ͨ�^(gu��)��(b��o)�r(sh��)�O(sh��)Ӌ(j��)ģ�K���Ԍ�(sh��)�F(xi��n)���c(di��n)��(b��o)�r(sh��)�����r(sh��)�[⏣��g�a�@ʾ���߶��g�a����ɣ��@ʾ�ɔ�(sh��)�a�ܘ�(g��u)�ɣ����õ��DŽ�(d��ng)�B(t��i)�@ʾ��ʽ����(sh��)�a�܄�(d��ng)�B(t��i)�@ʾ����(d��ng)�B(t��i)�����·��Ӌ(j��)��(sh��)��ݔ����8421BGD�a�D(zhu��n)�Q�锵(sh��)�a����Ҫ��߉��B(t��i)������ݔ����(sh��)�a�ܵ�Ƭ�x��̖(h��o)�͞��x��̖(h��o)�����^��(d��ng)�B(t��i)�����@ʾ��ʽ�����@ʾijһλLED �@ʾ�K�Ĕ�(sh��)��(j��)�ĕr(sh��)������λ���@ʾ��Ȼ�����@ʾ��һλ�Ĕ�(sh��)��(j��)��ֻҪ���Cÿһλ�@ʾ�ĕr(sh��)�g�g����Ҫ̫���������۵�ҕ�X(ju��)�����ĬF(xi��n)�Ϳ�����ɸ�λ��(sh��)��(j��)ͬ�r(sh��)�@ʾ�ļ���һ��ÿһλ���@ʾ�r(sh��)�g��1~10ms�� ���������\(y��n)�м��Y(ji��)�� ��1�����lģ�K��fenpin�� 1������ library ieee; use ieee.std_logic_1164.all; entity fenpin is port(clk6:in std_logic; q1000,q5,q1:out std_logic); end fenpin; architecture ccc_arc of fenpin is signal x:std_logic; begin process(clk6) variable cnt:integer range 0 to 24999; begin if clk6'event and clk6='1' then if cnt<24999 then cnt:=cnt+1; else cnt:=0; x<=not x; end if; end if; end process; q1000<=x; process(x) variable cnt2:integer range 0 to 999; variable y:std_logic; begin if x'event and x='1' then if cnt2<999 then cnt2:=cnt2+1; q1<='0'; else cnt2:=0; q1<='1'; end if; end if; if x'event and x='1' then y:=not y; end if; q5<=y; end process; end ccc_arc; 2�����沨�Σ�

- ����Y(ji��)���������a(ch��n)������Ӌ(j��)�r(sh��)������ݔ�룬�����@ʾ���Լ����Q������ĸ���(g��)�l�ʵ���̖(h��o)��

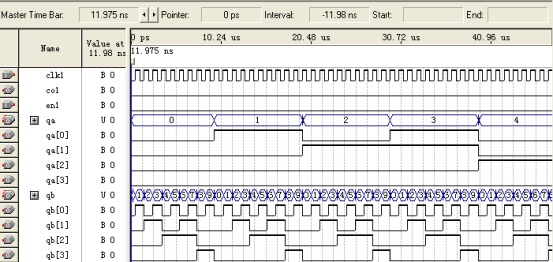

��2����ģ�K��second�� 1������ library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity second is port (clk1,en1:in std_logic; qa:out std_logic_vector(3 downto 0); co1:out std_logic; qb:out std_logic_vector(3 downto 0)); end second; architecture cc of second is signal cout2,cout1:std_logic_vector(3 downto 0); signal mm: std_logic; begin process(clk1,en1) begin if en1='1' then cout2<="0000";cout1<="0000"; elsif (clk1'event and clk1='1')then if (cout2=5 and cout1=8) then cout2<=cout2;cout1<=cout1+1;mm<='1'; elsif (cout2=5 and cout1=9) then cout2<="0000";cout1<="0000";mm<='0'; else if (cout1=9) then cout2<=cout2+1;cout1<="0000";mm<='0'; else cout2<=cout2;cout1<=cout1+1;mm<='0'; end if; end if; end if; end process; co1<=mm; qa<=cout2; qb<=cout1; end cc; 2�����沨�Σ�

- ����Y(ji��)��������ԓģ�K��(sh��)�H��һ��(g��)��ʮ�M(j��n)��Ӌ(j��)��(sh��)��������ʮ���һ��犣����ô�ģ�K���������벿���O(sh��)Ӌ(j��)��ͨ�^(gu��)�^���֪�����沨�������_���еġ�

��3����ģ�K��minute�� 1������ library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity minute is port (clk2,en2:in std_logic; qc:out std_logic_vector(3 downto 0); co2:out std_logic; qd:out std_logic_vector(3 downto 0)); end minute; architecture bb of minute is signal cout2,cout1:std_logic_vector(3 downto 0); signal cc:std_logic; begin process(clk2,en2) begin if en2='1' then if (clk2'event and clk2='1')then if (cout2=5 and cout1=8) then cout2<=cout2;cout1<=cout1+1;cc<='1'; elsif (cout2=5 and cout1=9) then cout2<="0000";cout1<="0000";cc<='0'; else if (cout1=9) then cout2<=cout2+1;cout1<="0000";cc<='0'; else cout2<=cout2;cout1<=cout1+1;cc<='0'; end if; end if; end if; end if; end process; co2<=cc; qc<=cout2; qd<=cout1; end bb 2�����沨�Σ�

- ����Y(ji��)����������ģ�K��(sh��)�HҲ��һ��(g��)��ʮ�M(j��n)�Ƶ�Ӌ(j��)��(sh��)��ģ�K����ʮ��犼���һ��(g��)С�r(sh��)���ô�ģ�K�ͳɹ���Q�˷��O(sh��)Ӌ(j��)ģ�K�@��(g��)�y�}���ķ��沨�ο�֪��ԓ�O(sh��)Ӌ(j��)�r(sh��)���_�ġ�

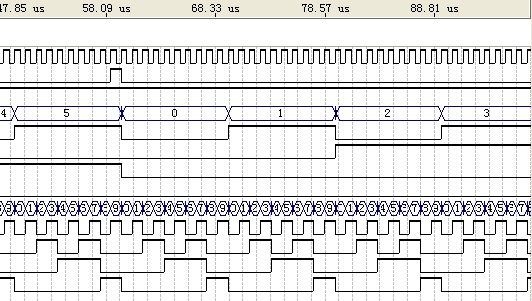

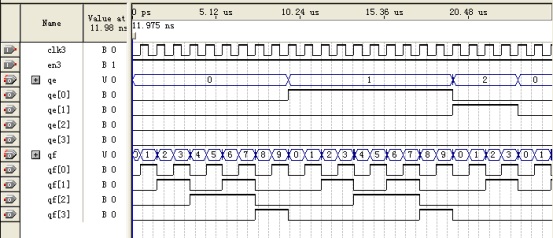

��4���r(sh��)ģ�K��hour�� 1������ library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity hour is port (clk3,en3:in std_logic; qe:out std_logic_vector(3 downto 0); qf:out std_logic_vector(3 downto 0)); end hour; architecture aa of hour is signal cout2,cout1:std_logic_vector(3 downto 0); begin process(clk3,en3) begin if en3='1' then if (clk3'event and clk3='1')then if (cout2=2 and cout1=3) then cout2<="0000";cout1<="0000"; else if (cout1=9) then cout2<=cout2+1;cout1<="0000"; else cout2<=cout2;cout1<=cout1+1; end if; end if; end if; end if; end process; qe<=cout2; qf<=cout1; end aa; 2�����沨�Σ�

- ����Y(ji��)���������@��һ��(g��)24Ӌ(j��)��(sh��)�����Á�(l��i)��ʾ24С�r(sh��)��ͨ�^(gu��)���ο�֪�������O(sh��)Ӌ(j��)���_������Ӌ(j��)�r(sh��)��ÿ��������00:00:00�_(k��i)ʼӋ(j��)�r(sh��)�ģ���Ҫ���A(y��)�Õr(sh��)�g�_(k��i)ʼ������ͨ�^(gu��)��У�r(sh��)����У�֡������㡱����(g��)���I�{(di��o)���r(sh��)�g��

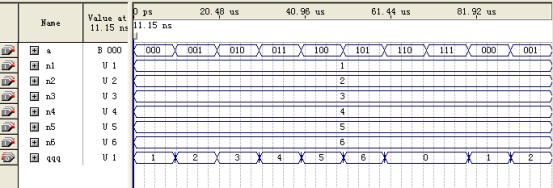

��5����(sh��)�a�@ʾ�(q��)��(d��ng)ģ�K 1������ library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity hhh is port(n1,n2,n3,n4,n5,n6:in std_logic_vector(3 downto 0); a:in std_logic_vector(2 downto 0); qqq:out std_logic_vector(3 downto 0)); end hhh; architecture dd of hhh is begin with a select qqq<=n1 when "000", n2 when "001", n3 when "010", n4 when "011", n5 when "100", n6 when "101", "0000" when others; end dd; 2�����沨�Σ�

- ����Y(ji��)���������䌍(sh��)�@��һ��(g��)�x�������IJ��ΈD���Ժ���������(l��i)�������Á�(l��i)�x����Ҫ�@ʾ�Ĕ�(sh��)�֣��������ʮλ���͕�(hu��)�x��n1���g�a�@ʾ���@ʾ����(l��i)���߂��(q��)��(d��ng)��(sh��)�a�ܵ�����!

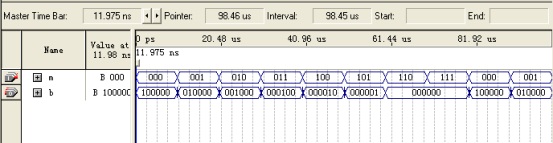

(6)Ƭ�xģ�K��sell�� 1������ library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity ggg is port(m:in std_logic_vector(2 downto 0); b:out std_logic_vector(5 downto 0)); end ggg; architecture ee of ggg is begin with m select b<="100000" when "000", "010000" when "001", "001000" when "010", "000100" when "011", "000010" when "100", "000001" when "101", "000000" when others; end ee; 2�����沨�Σ�

- ����Y(ji��)���������O(sh��)�Õr(sh��)�g�r(sh��)������Ĕ�(sh��)��(j��)���o�@ʾģ�K����(d��ng)�O(sh��)���[⏕r(sh��)����(sh��)��(j��)���o�[犺��@ʾģ�K��

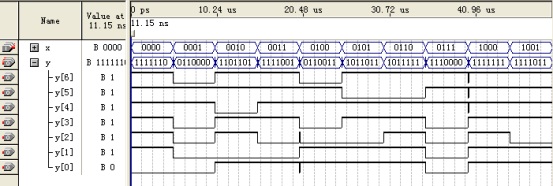

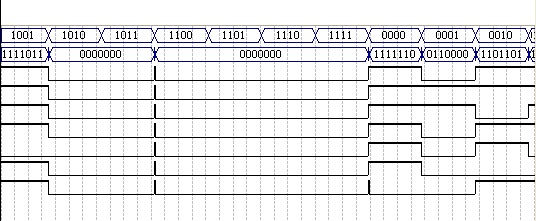

(7)�g�a�@ʾģ�K(display) 1������ library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity decoder is port(x:in std_logic_vector(3 downto 0); y:out std_logic_vector(6 downto 0)); end decoder; architecture one of decoder is begin with x select y<="1111110" when "0000", "0110000" when "0001", "1101101" when "0010", "1111001" when "0011", "0110011" when "0100", "1011011" when "0101", "1011111" when "0110", "1110000" when "0111", "1111111" when "1000", "1111011" when "1001", "0000000" when others; end one; 2�����沨�Σ�

- ����Y(ji��)����������ģ�K���Á�(l��i)�@ʾ�r(sh��)�g�ģ����Ä�(d��ng)�B(t��i)�@ʾ��ʽ��

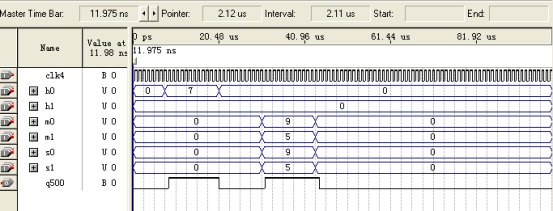

��8����(b��o)�r(sh��)ģ�K��alart�� 1) ���� library ieee; use ieee.std_logic_1164.all; entity sst is port(h1,h0,m1,m0,s1,s0:in std_logic_vector(3 downto 0); clk4:in std_logic; q500:out std_logic); end sst; architecture sss of sst is begin process(clk4,m1,m0,s1,s0) begin if (clk4'event and clk4='1') then if ((h1="0000" and h0="0111" and m1="0000" and m0="0000") or (m1="0101" and m0="1001" and s1="0101" and s0="1001"))then q500<='1'; else q500<='0'; end if; end if; end process; end sss; 2) ���沨�Σ�

- ����Y(ji��)��������ͨ�^(gu��)�^�첨�ο�֪����(d��ng)�r(sh��)犕r(sh��)�g�c���c(di��n)���[��A(y��)�O(sh��)�r(sh��)�g��ͬ�r(sh��)���o��һ��(g��)�}�_��̖(h��o)��ʹ���Q���Q�У���(sh��)�F(xi��n)���c(di��n)��(b��o)�r(sh��)�Ͷ��r(sh��)�[⏹��ܡ�

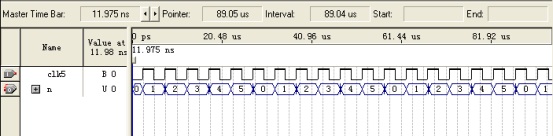

��9�����M(j��n)��Ӌ(j��)��(sh��)��ģ�K��cnt6�� 1������ library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity cnt6 is port (clk5:in std_logic; n:out std_logic_vector(2 downto 0)); end cnt6; architecture behav of cnt6 is signal q1:std_logic_vector(2 downto 0); begin process(clk5) begin if clk5'event and clk5='1' then if q1<5 then q1<=q1+1; else q1<=(others=>'0'); end if; end if; end process; n<=q1; end behav; 2�����沨�Σ�

- ����Y(ji��)�������������@���Կ����@��һ��(g��)��(ji��n)�ε����M(j��n)��Ӌ(j��)��(sh��)�������c3-6�g�a��������îa(ch��n)��Ƭ�x��̖(h��o)��

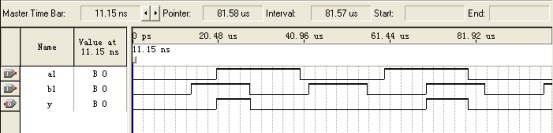

��10����ݔ���cģ�K��and2a�� 1������ library ieee; use ieee.std_logic_1164.all; entity anda is port (a1,b1:in std_logic; y:out std_logic); end anda; architecture an of anda is begin y<=a1 and b1; end an; 2�����沨�Σ�

3) ����Y(ji��)����������(j��ng)�^�첨�Σ��������_��ԓ�c�T(m��n)�ăɂ�(g��)ݔ��˷քe����ģ�K�ͷ�ģ�K���M(j��n)λݔ����̖(h��o)����(d��ng)����������ƽ�r(sh��)���r(sh��)ģ�Kʹ�ܶ˼�����ƽ���r(sh��)ģ�K������ ��11����ݔ���ģ�K(or2a) 1������ library ieee; use ieee.std_logic_1164.all; entity or_1 is port (a1,b1:in std_logic; y:out std_logic); end or_1; architecture oo of or_1 is begin y<=a1 or b1; end oo; 2�����沨�Σ�

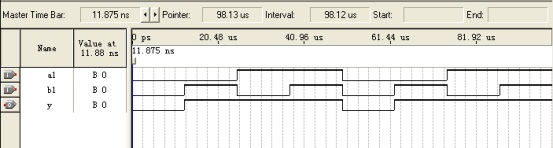

3) ����Y(ji��)��������������(g��)��(sh��)��犳����O(sh��)Ӌ(j��)�У���̎�õ���ݔ����T(m��n)��һ̎�Ƿ�ģ�K�����T(m��n)��ݔ��քe����ģ�K���M(j��n)λݔ����̖(h��o)���ⲿУ����̖(h��o)����һһ��(g��)��̖(h��o)����ƽ����ģ�Kʹ�ܶ˾͞���ƽ����ģ�K��������һ̎���ڕr(sh��)ģ�K��ʹ�ܶˣ����ܷ�ģ�K�M(j��n)λݔ�����ⲿУ�r(sh��)��̖(h��o)ݔ��Ŀ��ƣ�ֻҪ��һλ���ƽ���r(sh��)ģ�K���������� �ġ�플��·�O(sh��)Ӌ(j��)������Y(ji��)���c���� - library ieee;

- use ieee.std_logic_1164.all;

- entity digital_clock is

- port(clk,sa,sb,sc:in std_logic;

- q1:out std_logic;

- r:out std_logic_vector(5 downto 0);

- q0:out std_logic_vector(6 downto 0));

- end digital_clock;

- architecture main of digital_clock is

- component anda

- port(a1,b1:in std_logic;

- y:out std_logic);

- end component;

- component or_1

- port(a1,b1:in std_logic;

- y:out std_logic);

- end component;

- component fenpin

- port(clk6:in std_logic;

- q1000,q1,q5:out std_logic);

- end component;

- component hour

- port (clk3,en3:in std_logic;

- qe:out std_logic_vector(3 downto 0);

- qf:out std_logic_vector(3 downto 0));

- end component;

- component minute

- port (clk2,en2:in std_logic;

- qc:out std_logic_vector(3 downto 0);

- co2:out std_logic;

- qd:out std_logic_vector(3 downto 0));

- end component;

- component second

- port (clk1,en1:in std_logic;

- qa:out std_logic_vector(3 downto 0);

- co1:out std_logic;

- qb:out std_logic_vector(3 downto 0));

- end component;

- component sst is

- port(h1,h0,m1,m0,s1,s0:in std_logic_vector(3 downto 0);

- clk4:in std_logic;

- q500:out std_logic);

- end component;

- component hhh

- port(n1,n2,n3,n4,n5,n6:in std_logic_vector(3 downto 0);

- a:in std_logic_vector(2 downto 0);

- qqq:out std_logic_vector(3 downto 0));

- end component;

- component ggg

- port(m:in std_logic_vector(2 downto 0);

- b:out std_logic_vector(5 downto 0));

- end component;

- component cnt6 is

- port (clk5:in std_logic;

- n:out std_logic_vector(2 downto 0));

- end component;

- component decoder

- port(x:in std_logic_vector(3 downto 0);

- y:out std_logic_vector(6 downto 0));

- end component;

- signal a,b,c,h, i,j,z:std_logic;

- signal k,l,e,f,u,v,t:std_logic_vector(3 downto 0);

- signal s: std_logic_vector(2 downto 0);

- begin

- u1:fenpin port map(clk6=>clk,q1=>h,q1000=>z);

- u2:second port map(clk1=>h,en1=>sc,qa=>k,qb=>l,co1=>I);

- u0:or_1 port map(a1=>i,b1=>sb,y=>a);

- u3:minute port map(clk2=>h,en2=>a,qc=>e,qd=>f,co2=>j);

- u30:anda port map(a1=>i,b1=>j,y=>b);

- u31:or_1 port map(a1=>b,b1=>sa,y=>c);

- u4:hour port map(clk3=>h,en3=>c,qe=>u,qf=>v);

- u5:sst port map(h1=>u,h0=>v,m1=>e,m0=>f,s1=>k,s0=>l,clk4=>h,q500=>q1);

- u6:hhh port map(n1=>k,n2=>l,n3=>e,n4=>f,n5=>u,n6=>v,qqq=>t,a=>s);

- u7:ggg port map(b=>r,m=>s);

- u8:cnt6 port map(n=>s,clk5=>z);

- u9:decoder port map(x=>t,y=>q0);

- end architecture main;

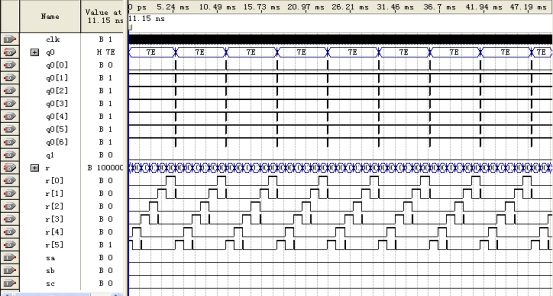

3������Y(ji��)������������ԇ�(y��n)�o�����l����50MHZ����QUARTUS-2ܛ���є�(sh��)��犵�ȫ�������^(gu��)��ӛ���(l��i)�����ף����@���Dֻ���乤����һС���֡����������d��FPGAоƬ�У����cӲ������(du��)��(y��ng)�B�Ӻã������(y��n)�C���҂����A(y��)�ڵ����й��ܣ��ʿ�֪ԓ플��ļ������_�ģ�ÿһ��(g��)ģ�K�Ĺ���Ҳ�������_�ģ�ģ�K֮�g���B��Ҳ�������_�ġ� ��ܛ���{(di��o)ԇ�����^(gu��)���У��҂��ԅ����Y���ϵij���?y��n)�ģ�壬���?j��)��(g��)�˵���Ҫ�����ĸ���(g��)����ģ�K���M����ģ�����酢���������^(gu��)����߀�dz��˺ܶ�Ć�(w��n)�}������������(sh��)�a�܄�(d��ng)�B(t��i)�@ʾ�У��҂�������NPN��9013���w���O�����锵(sh��)�a�ܵĽӵ��(q��)��(d��ng)���@���Ƭ�x��̖(h��o)��(y��ng)ԓ�Ǹ��ƽ��Ч���҂�?c��)������ǵ��ƽ���?j��ng)�^(gu��)��εĺ������M�ČW(xu��)��(x��)�����У��ҵ����@��(g��)�e(cu��)�`����Q���l��(w��n)�}�У��҂�Ҳ�ڷ��lģ�K�������ģ��õ��҂�����Ҫ���l�ʡ� �塢�ĵ��w��(hu��) ��(j��ng)�^(gu��)�@�εĔ�(sh��)���·�n���O(sh��)Ӌ(j��),�҂�(g��)�˵õ��˲��ٵ��ի@,һ����������Ҍ�(du��)�n����Փ���J(r��n)�R(sh��),��һ����Ҳ����ˌ�(sh��)�(y��n)�����������F(xi��n)���ҿ��Y(ji��)�����µ��w��(hu��)�ͽ�(j��ng)�(y��n)�� �@�ε��n���O(sh��)Ӌ(j��)���҂���ǰ���IJ�ͬ����?y��n)����X(ju��)���@�����������������Լ��H��ȥ��ɡ����������X(ju��)���@�Ό�(sh��)�(y��n)��F������̵ġ������O(sh��)Ӌ(j��)���^(gu��)��ȫ���҂��W(xu��)���Լ���(d��ng)�ց�(l��i)��ɵģ��@�ӣ��҂��ͱ��ҪŪ��һ��(g��)�·��ԭ�������@���������w��(hu��)���܌W(xu��)����Փ��(du��)��(sh��)�`��ָ��(d��o)���ã�Ū����(sh��)�(y��n)ԭ���������w��(hu��)���ˌ�(sh��)�(y��n)�IJ��������ǿ��Լ��H�Ԅ�(d��ng)�֣��H���_(k��i)��(d��ng)�X��H��ȥՈ(q��ng)�̄e�˲��ܵõ���ߵġ� �҂�����(sh��)�(y��n)�^��(du��)�����������ƣ�Ҫ���Լ��Ŀ������@���҂���Ҫ�г�ֵĜ�(zh��n)�䣬��������Ҳ��֪���ǂ�(g��)ʲô��(sh��)�(y��n)����ô����Ҳ�ǰ�������(sh��)�(y��n)�����c�n��֪�R(sh��)���P(gu��n)�ģ������n����֪�R(sh��)���҂����ܾ���(xi��)���Լ���Ҫ�ij���(sh��)�F(xi��n)�Լ��A(y��)�ڵĹ��ܡ� �҂�����(sh��)�(y��n)��Ҫһ�ɲ�׃��ī�س�Ҏ(gu��)����(y��ng)ԓ�и�����(chu��ng)�µľ���(sh��)�H�ϣ���Ū���ˌ�(sh��)�(y��n)ԭ���Ļ��A(ch��)�ϣ��҂��ĕr(sh��)�g�dz�ֵģ�����(sh��)�(y��n)��(y��ng)ԓ����������ģ�����f(shu��)��(chu��ng)��(du��)���҂���(l��i)�f(shu��)�Ǽ��y�£��Ǹ��������п��ܵġ���(sh��)�֕r(sh��)犴��w����ȥ�ܺ�(ji��n)�Σ������еĿ�׃�ĵط�߀���кܶ�ģ�Ʃ���f(shu��)���c(di��n)��(b��o)�r(sh��)���ܣ���(b��o)�r(sh��)���m(x��)�ĕr(sh��)�g�L(zh��ng)�̾���һ��(g��)��׃�ĵط��� �ڌ�(sh��)�(y��n)���^(gu��)�����҂�Ҫ���B(y��ng)�Լ��Ī�(d��)��������(w��n)�}���ͽ�Q��(w��n)�}���������ھ����^(gu��)���У��҂�Ҳ�����˺ܶ�Ć�(w��n)�}����֮ǰ�ᵽ�Ą�(d��ng)�B(t��i)�����(q��)��(d��ng)��(w��n)�}�����һζ��ȥ��ѭ�Y���ϵij����Ԓ��������(g��)�O(sh��)Ӌ(j��)����(hu��)ʧ����ֻ�в���ČW(xu��)��(x��)�о������ܽ�Q��(w��n)�}�� �@�ε��n���O(sh��)Ӌ(j��)���ҵ��ի@�ܶ࣬���ұ����(l��i)�f(shu��)��������(du��)��Փ֪�R(sh��)���˸���������⣬��(du��)�ڌ�(sh��)�H�IJ�����Ҳ�����|(zh��)���w�S����(j��ng)�^(gu��)�@�εČ�(sh��)�(y��n)���҂����w��(du��)����(g��)���涼�õ��˲��ٵ���ߣ��F(tu��n)�(du��)�ĺ������R(sh��)Ҳ����(qi��ng)�˺ܶࡣ ���������Y�ϣ� ���Ҳ� .�� EDA���̌�(sh��)�`���g(sh��) ��.���W(xu��)���I(y��)������.2004��12�� ���ƽ .�� ����Quartus II��FPGA/CPLD�O(sh��)Ӌ(j��)�c��(sh��)�` ��.������ӹ��I(y��)������.2010��4�� - library ieee;

- use ieee.std_logic_1164.all;

- entity fenpin is

- port(clk6:in std_logic;

- q1000,q5,q1:out std_logic);

- end fenpin;

- architecture ccc_arc of fenpin is

- signal x:std_logic;

- begin

- process(clk6)

- variable cnt:integer range 0 to 24999;

- begin

- if clk6'event and clk6='1' then

- if cnt<24999 then

- cnt:=cnt+1;

- else

- cnt:=0;

- x<=not x;

- end if;

- end if;

- end process;

- q1000<=x;

- process(x)

- variable cnt2:integer range 0 to 999;

- variable y:std_logic;

- begin

- if x'event and x='1' then

- if cnt2<999 then

- cnt2:=cnt2+1;

- q1<='0';

- else

- cnt2:=0;

- q1<='1';

- end if;

- end if;

- if x'event and x='1' then

- y:=not y;

- end if;

- q5<=y;

- end process;

- end ccc_arc;

- library ieee;

- use ieee.std_logic_1164.all;

- use ieee.std_logic_unsigned.all;

- entity second is

- port (clk1,en1:in std_logic;

- qa:out std_logic_vector(3 downto 0);

- co1:out std_logic;

- qb:out std_logic_vector(3 downto 0));

- end second;

- architecture cc of second is

- signal cout2,cout1:std_logic_vector(3 downto 0);

- signal mm: std_logic;

- begin

- process(clk1,en1)

- begin

- if en1='1' then

- cout2<="0000";cout1<="0000";

- elsif (clk1'event and clk1='1')then

- if (cout2=5 and cout1=8) then cout2<=cout2;cout1<=cout1+1;mm<='1';

- elsif (cout2=5 and cout1=9) then cout2<="0000";cout1<="0000";mm<='0';

- else if (cout1=9) then cout2<=cout2+1;cout1<="0000";mm<='0';

- else cout2<=cout2;cout1<=cout1+1;mm<='0';

- end if;

- end if;

- end if;

- end process;

- co1<=mm;

- qa<=cout2;

- qb<=cout1;

- end cc;

- library ieee;

- use ieee.std_logic_1164.all;

- use ieee.std_logic_unsigned.all;

- entity minute is

- port (clk2,en2:in std_logic;

- qc:out std_logic_vector(3 downto 0);

- co2:out std_logic;

- qd:out std_logic_vector(3 downto 0));

- end minute;

- architecture bb of minute is

- signal cout2,cout1:std_logic_vector(3 downto 0);

- signal cc:std_logic;

- begin

- process(clk2,en2)

- begin

- if en2='1' then

- if (clk2'event and clk2='1')then

- if (cout2=5 and cout1=8) then cout2<=cout2;cout1<=cout1+1;cc<='1';

- elsif (cout2=5 and cout1=9) then cout2<="0000";cout1<="0000";cc<='0';

- else if (cout1=9) then cout2<=cout2+1;cout1<="0000";cc<='0';

- else cout2<=cout2;cout1<=cout1+1;cc<='0';

- end if;

- end if;

- end if;

- end if;

- end process;

- co2<=cc;

- qc<=cout2;

- qd<=cout1;

- end bb

- library ieee;

- use ieee.std_logic_1164.all;

- use ieee.std_logic_unsigned.all;

- entity hour is

- port (clk3,en3:in std_logic;

- qe:out std_logic_vector(3 downto 0);

- qf:out std_logic_vector(3 downto 0));

- end hour;

- architecture aa of hour is

- signal cout2,cout1:std_logic_vector(3 downto 0);

- begin

- process(clk3,en3)

- begin

- if en3='1' then

- if (clk3'event and clk3='1')then

- if (cout2=2 and cout1=3) then cout2<="0000";cout1<="0000";

- else if (cout1=9) then cout2<=cout2+1;cout1<="0000";

- else cout2<=cout2;cout1<=cout1+1;

- end if;

- end if;

- end if;

- end if;

- end process;

- qe<=cout2;

- qf<=cout1;

- end aa;

- library ieee;

- use ieee.std_logic_1164.all;

- use ieee.std_logic_unsigned.all;

- entity hhh is

- port(n1,n2,n3,n4,n5,n6:in std_logic_vector(3 downto 0);

- a:in std_logic_vector(2 downto 0);

- qqq:out std_logic_vector(3 downto 0));

- end hhh;

- architecture dd of hhh is

- begin

- with a select

- qqq<=n1 when "000",

- n2 when "001",

- n3 when "010",

- n4 when "011",

- n5 when "100",

- n6 when "101",

- "0000" when others;

- end dd;

- library ieee;

- use ieee.std_logic_1164.all;

- use ieee.std_logic_unsigned.all;

- entity ggg is

- port(m:in std_logic_vector(2 downto 0);

- b:out std_logic_vector(5 downto 0));

- end ggg;

- architecture ee of ggg is

- begin

- with m select

- b<="100000" when "000",

- "010000" when "001",

- "001000" when "010",

- "000100" when "011",

- "000010" when "100",

- "000001" when "101",

- "000000" when others;

- end ee;

- library ieee;

- use ieee.std_logic_1164.all;

- use ieee.std_logic_unsigned.all;

- entity decoder is

- port(x:in std_logic_vector(3 downto 0);

- y:out std_logic_vector(6 downto 0));

- end decoder;

- architecture one of decoder is

- begin

- with x select

- y<="1111110" when "0000",

- "0110000" when "0001",

- "1101101" when "0010",

- "1111001" when "0011",

- "0110011" when "0100",

- "1011011" when "0101",

- "1011111" when "0110",

- "1110000" when "0111",

- "1111111" when "1000",

- "1111011" when "1001",

- "0000000" when others;

- end one;

- library ieee;

- use ieee.std_logic_1164.all;

- entity sst is

- port(h1,h0,m1,m0,s1,s0:in std_logic_vector(3 downto 0);

- clk4:in std_logic;

- q500:out std_logic);

- end sst;

- architecture sss of sst is

- begin

- process(clk4,m1,m0,s1,s0)

- begin

- if (clk4'event and clk4='1') then

- if ((h1="0000" and h0="0111" and m1="0000" and m0="0000")

- or (m1="0101" and m0="1001" and s1="0101" and s0="1001"))then

- q500<='1';

- else

- q500<='0';

- end if;

- end if;

- end process;

- end sss;

- library ieee;

- use ieee.std_logic_1164.all;

- use ieee.std_logic_unsigned.all;

- entity cnt6 is

- port (clk5:in std_logic;

- n:out std_logic_vector(2 downto 0));

- end cnt6;

- architecture behav of cnt6 is

- signal q1:std_logic_vector(2 downto 0);

- begin

- process(clk5)

- begin

- if clk5'event and clk5='1' then

- if q1<5 then q1<=q1+1;

- else q1<=(others=>'0');

- end if;

- end if;

- end process;

- n<=q1;

- end behav;

- library ieee;

- use ieee.std_logic_1164.all;

- entity anda is

- port (a1,b1:in std_logic;

- y:out std_logic);

- end anda;

- architecture an of anda is

- begin

- y<=a1 and b1;

- end an;

- library ieee;

- use ieee.std_logic_1164.all;

- entity or_1 is

- port (a1,b1:in std_logic;

- y:out std_logic);

- end or_1;

- architecture oo of or_1 is

- begin

- y<=a1 or b1;

- end oo;

- library ieee;

- use ieee.std_logic_1164.all;

- entity digital_clock is

- port(clk,sa,sb,sc:in std_logic;

- q1:out std_logic;

- r:out std_logic_vector(5 downto 0);

- q0:out std_logic_vector(6 downto 0));

- end digital_clock;

- architecture main of digital_clock is

- component anda

- port(a1,b1:in std_logic;

- y:out std_logic);

- end component;

- component or_1

- port(a1,b1:in std_logic;

- y:out std_logic);

- end component;

- component fenpin

- port(clk6:in std_logic;

- q1000,q1,q5:out std_logic);

- end component;

- component hour

- port (clk3,en3:in std_logic;

- qe:out std_logic_vector(3 downto 0);

- qf:out std_logic_vector(3 downto 0));

- end component;

- component minute

- port (clk2,en2:in std_logic;

- qc:out std_logic_vector(3 downto 0);

- co2:out std_logic;

- qd:out std_logic_vector(3 downto 0));

- end component;

- component second

- port (clk1,en1:in std_logic;

- qa:out std_logic_vector(3 downto 0);

- co1:out std_logic;

- qb:out std_logic_vector(3 downto 0));

- end component;

- component sst is

- port(h1,h0,m1,m0,s1,s0:in std_logic_vector(3 downto 0);

- clk4:in std_logic;

- q500:out std_logic);

- end component;

- component hhh

- port(n1,n2,n3,n4,n5,n6:in std_logic_vector(3 downto 0);

- a:in std_logic_vector(2 downto 0);

- qqq:out std_logic_vector(3 downto 0));

- end component;

- component ggg

- port(m:in std_logic_vector(2 downto 0);

- b:out std_logic_vector(5 downto 0));

- end component;

- component cnt6 is

- port (clk5:in std_logic;

- n:out std_logic_vector(2 downto 0));

- end component;

- component decoder

- port(x:in std_logic_vector(3 downto 0);

- y:out std_logic_vector(6 downto 0));

- end component;

- signal a,b,c,h, i,j,z:std_logic;

- signal k,l,e,f,u,v,t:std_logic_vector(3 downto 0);

- signal s: std_logic_vector(2 downto 0);

- begin

- u1:fenpin port map(clk6=>clk,q1=>h,q1000=>z);

- u2:second port map(clk1=>h,en1=>sc,qa=>k,qb=>l,co1=>I);

- u0:or_1 port map(a1=>i,b1=>sb,y=>a);

- u3:minute port map(clk2=>h,en2=>a,qc=>e,qd=>f,co2=>j);

- u30:anda port map(a1=>i,b1=>j,y=>b);

- u31:or_1 port map(a1=>b,b1=>sa,y=>c);

- u4:hour port map(clk3=>h,en3=>c,qe=>u,qf=>v);

- u5:sst port map(h1=>u,h0=>v,m1=>e,m0=>f,s1=>k,s0=>l,clk4=>h,q500=>q1);

- u6:hhh port map(n1=>k,n2=>l,n3=>e,n4=>f,n5=>u,n6=>v,qqq=>t,a=>s);

- u7:ggg port map(b=>r,m=>s);

- u8:cnt6 port map(n=>s,clk5=>z);

- u9:decoder port map(x=>t,y=>q0);

- end architecture main;

���ϵ�Word��ʽ�ęn51�����d��ַ��

��(sh��)��n���O(sh��)Ӌ(j��)��������fpga�Ĕ�(sh��)�֕r(sh��)犵��O(sh��)Ӌ(j��).doc

(364.62 KB, ���d��(sh��): 81)

��(sh��)��n���O(sh��)Ӌ(j��)��������fpga�Ĕ�(sh��)�֕r(sh��)犵��O(sh��)Ӌ(j��).doc

(364.62 KB, ���d��(sh��): 81)

2019-1-10 13:57 �ς�

�c(di��n)���ļ������d����

���d�e��: �ڎ� -5

|

����TQQ:125739409;���g(sh��)����QQȺ281945664

����TQQ:125739409;���g(sh��)����QQȺ281945664