在《阿莫電子論壇》上找到了代碼,鏈接如下:

www點amobbs點com/thread-840211-1-1.html

CPLD應用:光柵旋轉編碼器的4倍頻解碼

發表于 2007-10-27 10:22:55 | 只看該作者 回帖獎勵

CPLD應用:增量式光柵旋轉編碼器的4倍頻解碼

剛學了幾天的CPLD,上傳我的第一個應用,不知道實際工作情況如何,希望高手指點指點,謝謝

如果CLK時鐘頻率為25Mhz,則至少可以對輸出頻率2.5Mhz以下增量式光柵旋轉編碼器的進行4倍頻解碼

概念如下:

增量式光柵旋轉編碼器分辨率:2500p/r (常用伺服系統的編碼器)

按工作時最大的輸出頻率為2.5Mhz計算,編碼器可以工作到60000r/m,當然這樣的旋轉速度實際上是很難達到的,實際上的常用的伺服電機最大工作到5000r/m

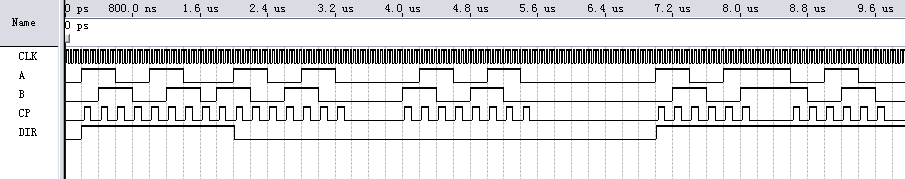

CLK:倍頻用時鐘頻率

A:編碼器A相

B:編碼器B相

CP:解碼后的脈沖

DIR:旋轉方向

仿真圖片如下:

仿真圖片

Verilog hdl代碼:

module decoder(CLK, A, B, CP, DIR);

input CLK;

input A;

input B;

output CP;

output DIR;

reg CP;

reg DIR;

wire a_xor_b;

reg a_xor_b_temp;

reg[3:0] a_xor_b_counter;

xor (a_xor_b, A, B);

always @(posedge CLK)

begin

if(a_xor_b_temp != a_xor_b)

begin

CP = 1'b1;

a_xor_b_temp = a_xor_b;

a_xor_b_counter = 4'b0000;

end

else

begin

a_xor_b_counter = a_xor_b_counter + 4'b0001;

if(a_xor_b_counter >= 4'b0010) // 根據實際應用,可以改變a_xor_b_counter上限值來改變輸出脈寬

begin

CP = 1'b0;

end

end

end

always @(posedge A) begin

DIR = ~B;

end

endmodule

不明白,為什么編碼器還要外接時鐘?

|