|

摘 要 傳統的搶答器分立元件使用較多,造成電路的成本偏高,設計出數字化全集成電路的多路搶答器是現代電子技術發展的要求,因此向讀者介紹筆者用74 系列常用集成電路設計的數碼顯示四路搶答器,并詳細分析了電路工作原理。其功能為供四人用的智力競賽搶答器裝置線路。,本電路分為兩部分:一是基本搶答部分,二是倒計時部分。搶答有效有聲音提示并顯示組別,由主持人手動復位。此搶答操作方便,在很多的場所都可以使用,并且給人的視覺效果非常好.

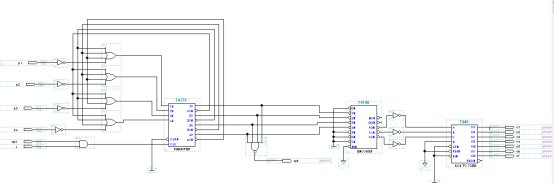

一、完成課題的工作基礎和實驗條件 1.工作基礎 搶答器作為一種電子產品,早已廣泛應用于各種智力和知識競賽場合,但目前所使用的搶答器存在分立元件使用較多,造成電路的成本偏高,而現代電子技術的發展要求電子電路朝數字化、集成化方向發展,因此設計出數字化全集成電路的多路搶答器是現代電子技術發展的要求,故筆者按照這一要求,并根據74175D觸發器的功能特點,用74192和其它幾塊常用的74系列數字集成電路設計出了一數碼顯示四路搶答器電路,該電路具有成本低、元器件容易得到、路數多、數碼直觀顯示、性能穩定等諸多優點,而且該電路也可作數字集成電路應用的一個范例,來作為學習使用數字集成電路之用。 2.實驗條件 (1)GW48系列EDA/SOC實驗開發系統(提供有目標芯片FPGA-型號EP1K30TC144-3、數碼顯示器、二極管、三極管、鈕子開關、晶振等資源); (2)電路設計采用下列器件: 74175、74148、74192、7448、ANDX、ORX、NOT,OR8,NAND等。 二、設計任務和要求 1. 基本要求 (1)有4路搶答; (2)數字顯示搶答組別; (3)由主持人復位后方可搶答; (4)聲音(D)提示已有人搶答。 2. 附加功能 (1)主持人復位前有人搶答聲音提示 (2)有倒計時功能,倒計時為30秒 ,數字顯示倒計時間,如果計時到零還未有人搶答則聲音提示且之后的搶答無效。 (3)在倒計時未到達零之前如果有人搶答則計時停止。 三、電路基本原理 1.數字搶答器總體方框圖  如圖1所示為總體方框圖。其工作原理為:接通電源后,主持人將開關撥到“準備”(低電平)狀態,定時器顯示設定時間,計時器處于禁止狀態,此時如果有人搶答,則聲音提示搶答無效。主持人將開關置“開始”(高電平)狀態,宣布開始,搶答器工作。定時器倒計時,選手在預定時間內搶答時,搶答器完成: 優先判斷、編號鎖存、編號顯示、揚聲器提示。當一輪搶答之后,定時器停止、禁止二次搶答、定時器顯示剩余時間。如果再次搶答必須由主持人再次操作"準備"和"開始"狀態開關。如果在 規定時間內沒有人搶答,則聲音提示,之后搶答無效。 2.單元電路設計 (1) 搶答器電路  圖 2搶答器電路 圖 2搶答器電路 參考電路如圖2所示。該電路完成兩個功能:一是分辨出選手按鍵的先后,并鎖存優先搶答者的編號,同時譯碼顯示電路顯示編號;二是有選手搶答后其他選手按鍵操作無效。工作過程:剛開始選手開關p1、p2、p3、p4全為低電平,開關S置于0(低電平)時,D觸發器的無時鐘脈沖,觸發器處于禁止狀態。觸發器4個輸出保持為1(高電平),使74148的輸入端1N、2N、3N、4N為高電平,經74148優先編碼器編碼后輸出端全為高電平, A2N,A1N,A0N經反相器后接到7448的A、B、C輸入端,經BCD—7段譯碼器7448譯碼后全為低電平,共陰極七段碼電路沒有顯示。將當開關S置于1(高電平)時,搶答器處于等待工作狀態,當有選手將鍵按下時(如按下P3,P3為高電平),74148的輸出經鎖存電路后后,3Q=0, 1Q、2Q、4Q=0,74LS48處于工作狀態,4Q3Q2Q1Q=1011,經譯碼顯示為"3"。此外,3Q=1,使觸發器其他輸入端為保持為1,處于禁止狀態,封鎖其他按鍵的輸入,從而保證了搶答者的優先性。此時SPK輸出脈沖信號,聲音提示有人搶答。如有再次搶答需由主持人將S開關重新置“0”,然后再進行下一輪搶答。74175、74148、7448分別為為D觸發器、10線—4線BCD編碼器和BCD-to-7-Segment Decoder BCD—7段譯碼器,表1、2、3為其功能表。

表1 74175功能表 表2 74148功能表

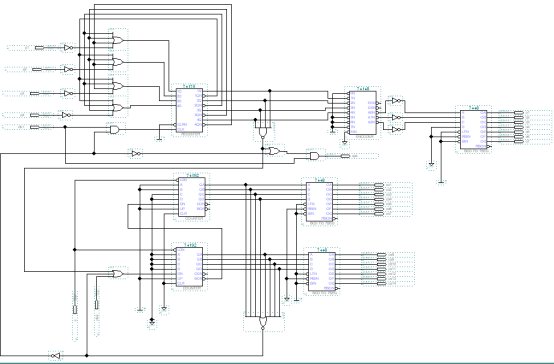

表3 7448功能表 (2)定時電路 表 3定時器電路 通過預置時間30秒電路對計數器進行預置,計數器的時鐘脈沖由秒脈沖電路提供。可預置時間的電路選用十進制同步加減計數器74LS192進行設計,具體電路如圖3所示。當開關S為低電平時,對兩片74192進行預置數,當開關為高電平且QD為低電平時倒計時開始,此時如果QD變為高電平,則停止計數,譯碼顯示電路上顯示剩余時間。若計時到零時QD還未低電平,這SPK輸出脈沖信號,聲音提示時間到。表4為74192的功能表。 表4 74192功能表 (3)電路總體設計 實驗原理圖見圖4.將搶答電路和計時電路的輸出用或門相連,從而使有人搶答或計時到零都有聲音提示;將計時電路的輸出端MANGER接到搶答電路的輸入端QD,從而保證計時到零后搶答無效;將搶答電路的的輸出端SPK接到計時電路的輸入端SPKIN,從而保證有選手搶答后計時停止。此外如果在計時未開時時有選手摁下,則聲音提示搶答無效。 本搶答器使用方法非常簡單,從上述工作原理可知,搶答前只需先將開關S置于“0”,然后再置于“1”,即可進行搶答。  圖 4實驗原理圖

四、實驗與調試 實驗調試時選用GW48系列EDA/SOC實驗開發系統(提供有目標芯片FPGA-型號EP1K30TC144-3、數碼顯示器、二極管、三極管、鈕子開關、晶振等資源),實驗選用實驗電路結構圖NO.0,選用數碼8、數碼7顯示倒計時,選用數碼1顯示搶答選手號,選用鍵8代表主持人控制端S,選用鍵7、鍵6、鍵5、鍵4表示選手號P1、P2、P3、P4.按照結構圖對管腳號進行封裝。實驗調試圖見圖5。 剛開始調試時發現一個問題:如果未有選手搶答則計時到零后數碼1顯示選手號為4,經過分析原因是計時到零后觸發器自動清零,經過優先編碼器后就輸出4,之后對電路進行了改進,將計時電路的輸出端manger和搶答電路的時鐘信號相“與”后接到觸發器的時鐘輸入端,將觸發器的清零端接高電平。第一個問題解決后引起的第二個問題是計時到零后無聲音提示,且計時到零后減法計數器繼續減,之后將計時電路的聲音輸出和搶答電路的聲音輸出相“或”后,再將計數器計時到零后的74192的所有輸出端“或非”后與74192的DN輸入端相“與”,這樣計時到零后74192的DN輸入端就為1,輸出就可以保持了。至此,電路的功能就全部可以實現了。 圖5 實驗調試圖 五、 體會 經過近兩周的努力,在老師和同學的幫助下,我完成了設計任務。通過這次課程設計,加深了自己對理論知識的理解,同時也鍛煉了自己把理論知識應用到實際問題的能力,更鍛煉了自己自學的能力,能夠根據需要去讀一些相關文獻,學會如何去使用一個軟件(學會一個軟件用好里面的幫助是最重要的)等,而這些正是以后工作學習生活所必需的。以前做實驗總是很單一,要不就是按課本上步驟一步一步走,要不就是設計簡單的如加法器,減法器之類的電路,或是用各種門電路設計簡單的報警電路,密碼鎖等。而這次實驗則是所有實驗的綜合,需要有一定理論基礎和積淀。 剛開始老師布置任務的時候覺得很難,經過兩天左右的思考初步設計把電路分成兩個模塊,一是基本的搶答電路,二是定時電路,各部分設計好了再整合在一起,這樣就不難設計了。搶答電路可以用D觸發器來完成,設計的關鍵是如何鎖存最先搶答的選手號,定時電路可以用秒脈沖加減法計數器來完成,為了更接近于實際,我用兩片74192分別代表十位和個位。初步設計后MAX+PLUSSII進行仿真無誤后再進行附加功能的添加,如計時前搶答的報警,計時到零的聲音提示及有選手搶答后計時的停止與聲音的提示等。 設計電路時收獲最大的是不管以后干什么,都要從大處著眼,小處著手,先將任務分成幾個部分,再一部分一部分的去完成,最終再完成總體的設計,不然直接設計一個整體的模型,不方便調試,出了錯也不知道是哪部分出了問題。 通過這次實驗,還有一個收獲就是感受到同學之間的溫暖和相互協作的力量。盡管我們各自設計的電路不盡相同,思路也可能迥然不同,但我們能夠互相幫助,遇到問題一起探討,一起解決,別人有什么不懂的也盡量幫忙 。相互學習,共同進步,這種團結協作的精神正是我們新一代大學生所要求的基本素質與修養。 由于知識水平的局限,設計中可能會存在著一些不足,我真誠的接受老師和同學的批評和指正.最后衷心感謝老師的悉心指導和同學們的熱心幫助!

以上圖文的Word格式文檔下載(內容和本網頁上的一模一樣,方便大家保存):

電子技術課程設計之智力搶答器.doc

(220.5 KB, 下載次數: 16)

電子技術課程設計之智力搶答器.doc

(220.5 KB, 下載次數: 16)

2018-12-24 10:54 上傳

點擊文件名下載附件

|