TD303導航協議

TD1030是一款高性能、高集成度的BDS/GPS/GLONASS/QZSS/SBAS衛星定位導航授時芯片。該芯片采用了射頻基帶一體化設計,單片集成了DC-DC、 LDO、電源管理、 POR、射頻處理、衛星定位導航授時數字基帶處理、 32位RISC CPU、RAM、FLASH存儲、Watchdog、Timer、RTC、天線狀態檢測與短路保護電路等。 TD1030芯片可通過不同的硬件外圍配置:采用內部集成DCDC供電、使用內部ROM來提供低功耗解決方案;同樣也可通過不同的硬件外圍配置:內部集成DCDC旁路、使用內部ROM、無源天線、單時鐘的設置來提供低成本解決方案。

最小BOM應用可以選擇DCDC、LDO、LNA內部集成及內部ROM方案,該解決方案不支持firmware升級能力。 如需要組合導航功能、輸出原始觀測量等功能的需求請選擇flash解決方案,該解決方案支持firmware升級功能。 應用上TD1030芯片支持多種選擇方式:

可選擇是否使用芯片內部集成 DCDC給TD1030芯片供電

可選擇RTC 晶振或內部時鐘

可選擇內部集成天線檢測電路

可選擇外部SQI flash或SIP集成flash,推薦優先考慮SIP集成flash方案,成本更低,空間尺寸更小。

3.1.4 工作模式

TD1030芯片支持持續定位模式、睡眠模式和待機模式。

持續定位模式是捕獲引擎全程打開,當搜索到所有衛星信息和星歷數據后,將自動切換到跟蹤模式,以減少工作電流,也就是當獲取到有效的位置信息、獲取全部的歷書數據、有效的衛星位置信息后開始進入跟蹤模式。 睡眠模式是保留 RTC 備份區正常工作外,內核電路有電,但是內核部分時鐘關閉,其他功能模塊電源和時鐘全部關閉。進入睡眠模式后,可以通過外部喚醒管腳(詳細見“3.5.8喚醒管腳”章節)和定時器喚醒,為支持熱啟動和溫啟動功能,要求主電掉電后必須備份區一直有電。

待機模式是只保留 RTC備份區正常工作,其他功能模塊電源和時鐘全部關閉,只支持上電恢復工作。為支持熱啟動和溫啟動功能,要求主電掉電后必須備份區一直有電,若需快速定位,建議接備份電。

3.2 時鐘

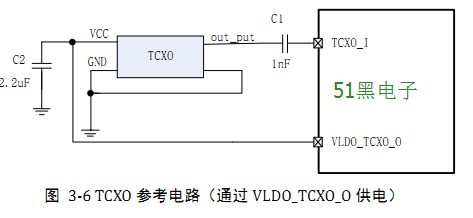

一個干凈和穩定的時鐘源是保證 GNSS定位導航性能的關鍵,因此方案設計時請考慮高穩定度的參考時鐘源。 為了保證能得到更好系統時鐘質量,穩定的電源供電無疑是基本需求。TCXO支持由外部供電和芯片VLDO_TCXO_O供電兩種方式。若通過外部直接給 TCXO供電,需考慮給 TCXO供電能力要達到4mA以上,紋波在輸入電壓的5%之內為佳;若通過芯片 VLDO_TCXO_O輸出給時鐘源供電,則需要注意在VLDO_TCXO_O 輸出加不小于2.2uF的濾波電容,且在應用中請確認選用的 TCXO器件工作功耗不可過高,需在VLDO_TCXO_O 的供電能力范圍。 時鐘源是個溫度敏感器件,PCB layout布局時,需考慮將TCXO盡量遠離發熱源端,如遠離片外DCDC。為了避免引入噪聲,TCXO的時鐘輸出到T3芯片的參考時鐘輸入端信號走線盡可能的短,并盡可能有地包圍,更詳細的描述請見本文檔PCB layout注意事項“3.8.2布線”章節。

3.2.1 TCXO

TCXO指標要求見“應用外圍器件選擇”說明。

3.2.1.1 TCXO 應用電路

TCXO支持由外部供電和芯片內部的 VLDO_TCXO_O供電兩種方式:

方式一:如果外部條件允許,支持由外部直接給 TCXO供電,如與 VDD_IO_IN相同的供電,此時需考慮TCXO的工作電壓和 VDD_IO_IN的工作電壓要相匹配,避免出現兩者電壓不一致(例如 VDD_IO_IN為 3.3V 而TCXO器件為

2.8V)的情況。

方式二:為了提供更好的電給 TCXO,一般采用VLDO_TCXO_O輸出給TCXO器件供電,供電電壓可由軟件配置

輸出。

除了可以通過 VLDO_TCXO_O端給 TCXO供電外,也可以通過該管腳控制TCXO的使能或禁能(要求 TCXO帶有使能端口),如圖3-7所示。此時,要考慮 VLDO_TCXO_O端口的電壓要低于 TCXO的供電電壓,一般推薦配置的電壓值為 TCXO供電電壓的 80%~90%。

方案應用中,為提高 TCXO的兼容性,參考電路在 TCXO的輸出端增加1nF的隔直電容。

3.2.1.2 TCXO 選用型號推薦

選擇 TCXO的時候,必須首先考慮基本指標,詳細見“應用外圍器件選擇”說明,一般建議使用0.5PPM初始頻率誤差的 TCXO,對于選取的TCXO, 需要小心留意它在需要的最高最低工作溫度下是否穩定。

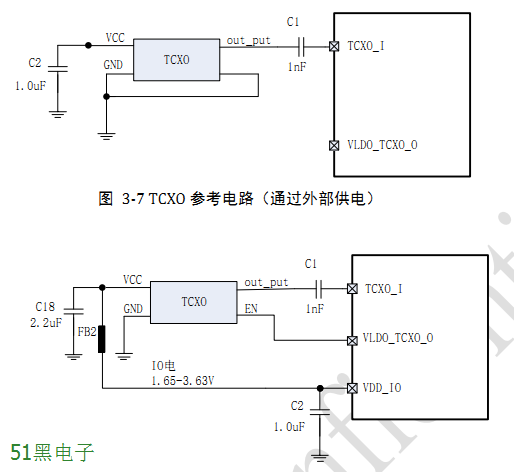

3.2.2 RTC

為了支持熱啟動、溫啟動、星歷推算等功能,當主電源掉電后為保存系統數據、星歷數據等,此時需要 RTC 域保持有電源及時鐘。RTC時鐘支持外部接 32.768KHz 晶體方案、單時鐘支持 RTC 方案和RTC使用外部時鐘方案。 TCXO指標要求見“應用外圍器件選擇”說明。

為更低成本考慮,該方案的 RTC 時鐘從內部電路的TCXO進行分頻得到 26KHz,此時只支持 TCXO參考時鐘為26MHz 的情況,其他頻率的TCXO不支持。當使用“單時鐘支持 RTC”方案時,RTC_I管腳必須接地,RTC_O管腳懸空。

為保證系統能支持熱啟動、溫啟動功能,得到 26KHz 相關的分頻電路必須保持供電,當VDD_IO_IN掉電時,該供電部分由 V_BACKUP_IN(備份電源)供電,此時,睡眠、待機功耗會加大。

3.2.2.3 RTC使用外部時鐘

本芯片支持使用外部時鐘,輸入給 RTC_I端口,頻率為32.768KHz。信號幅度大于100mV,最大為 990mV,方波輸入,duty約50%。

3.2.2.4 RTC 晶體選用型號推薦

詳細見“應用外圍器件選擇”說明。

3.3 復位

3.3.1 硬件復位

RESETn管腳為硬件復位管腳,內部集成上拉電阻,電平標準為 VDD_IO電平,當該管腳為低時,復位有效,最小復位脈沖為4uS。當不使用時,將該管腳懸空。

3.3.2 軟件及WatchDog復位

芯片還支持軟件復位、WatchDog復位,硬件端口不可見。

通常在 GPS波段,單級LNA 較難達到 20dB以上的增益,高于20dB 的增益通常需要用兩級或多級 LNA級聯得到。一般而言,前級的 LNA 增益越大, 后級的放大器噪聲系數對整個系統的影響越小,所以選取前級 LNA 時基本原則是增益越大越好,噪聲系數越小越好。需要注意的是芯片外部的 LNA總增益不得大于一個門限值,超過這個門限值,將可能導致后級的電路工作性能變差。

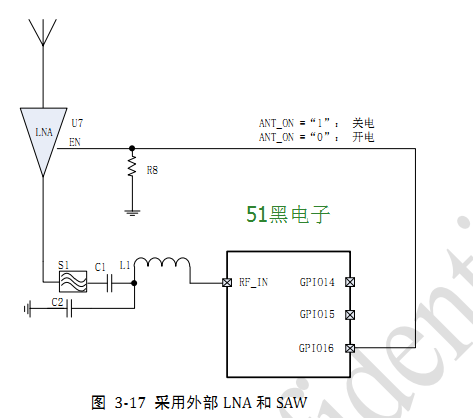

一般來說,為改善射頻鏈路前端噪聲系數、抑制帶外噪聲,提升GNSS的性能,通常在前端增加外部 LNA 和 SAW濾波器,如圖3-17所示。

SAW在前還是LNA 在前的優缺點對比見表格3-8 所示。

對于LNA而言,前級如果加入SAW濾波器, 插損會對信號有所衰減,但對噪聲影響不大,所以,會造成整體載噪比下降。但這種方案的好處在于對于輸入的強烈帶外干擾,效果比較好,常用于使用環境比較嚴苛的條件下。 如果LNA在前, 信號經過放大以后,再經過SAW濾波器, 則插損帶來的影響可以忽略, 但LNA通常是寬帶的, 對衛星信號帶外的噪音也會一并放大,噪聲經過LNA放大后,SAW只有提供-40dB左右的帶外抑制能力, 對于較強的帶外干擾信號,LNA輸出可能飽和導致后級無法正常工作。假設LNA對于-18dBm強度的帶外干擾信號會飽和, 前面加一個帶外抑制-40dB的SAW,就能確保LNA在22dBm強度的帶外干擾信號下不會飽和。 相比較而言,SAW在前級對于帶外干擾的抑制效果沒有SAW在LNA前級的效果好。

3.5 IO 接口

總共有 20個 GPIO,由VDD_IO_IN 供電,即GPIO的電平標準直接與 VDD_IO_IN 關聯,即支持 3.3V的GPIO,使用時需注意提供相對應電壓(即VDD_IO_IN 電壓)值。所有GPIO默認為input,且內部上拉;上拉功能可以通過軟件配置進行設置。

由于芯片管腳限制,GPIO功能結合系統軟件設計,GPIO與 SQI flash 接口、通信接口、配置接口、外部中斷輸入、授時信號、天線檢測、外部管腳喚醒、車速檢測脈沖功能等進行復用。

由于選用的數字 IO不支持防倒灌功能,在實際方案開發和應用中,需要明確與本芯片 UART、SPI、I2C通信的主機端口掉電后的信號狀態,當上位機要控制本芯片的主電源掉電時,應先把這些與本芯片有連接的端口設置為高阻態,以防止本芯片在關閉后還一直消耗上位機的電。

3.5.1 特殊定義管腳

包含三類特殊定義:

1. GPIO[5:0] 配置管腳功能;

2. GPIO[10] 通信切換功能;

3. GPIO[12] safeboot使能功能。

GPIO[5:0]為配置管腳功能。GPIO[5]為配置使能,GPIO[4:2]為 TCXO的類型配置,GPIO[1]為 DCDC 的使用配置。

3.8 PCB Layout注意事項

3.8.1 焊盤設計

QFN40/QFN36 的元器件封裝,封裝底面金屬為整個芯片的大地,layout時建議在元器件封裝的地端位置上加入過孔,并 PCB 板其他層上增加一層地,有利于增加散熱效果。PCB上焊接芯片管腳的器件封裝 pin要稍微大于芯片管腳實際面積,以確保焊接時有足夠的接觸面積。 QFN40 封裝的機械特性,詳細見《TD1030芯片手冊》。

3.8.2 布線

為達到 GNSS最佳性能,PCB layout的布局布線方面需要考慮以下方面:

電源:

內部集成DCDC旁路時要求:當不使用 DCDC時(即 DCDC 旁路),需將DCDC_IN 和 DCDC_OUT 短接。由于DCDC_IN與DCDC_OUT 短路,DCDC_IN 流過的電流比較大,PCB layout時需要注意該走線阻抗要盡量短。

V_CORE 要求:該電源連接LDO_CORE和 LDO_RF的輸入端,是整個芯片的主要耗電端,其中 LDO_CORE供電給內核電源,LDO_RF供電給RF 域供電。為能提供一個低噪聲的電源,V_CORE 輸入端 PCB layout走線要確保阻抗小于0.2歐姆。

時鐘:

TCXO是溫度敏感器件,注意避免高溫區。在 PCB layout時要特別注意接地、屏蔽和信號干擾方面,以確保鏈路上的干凈,為減少干擾,走線時要靠近芯片輸入端,時鐘輸入信號建議有地包圍,且 PCB其他層盡量不要有信號穿過。

如果通過VLDO_TCXO_O給TCXO供電,其濾波電容(C2)應靠近TCXO器件。

射頻前端:

很重要的一點是為達到GNSS最佳性能,PCB layout的布局方面需要注意在接收信號鏈路相關的地方,關鍵包含RF信號、LNA、天線本身等,在layout時要特別注意接地、屏蔽和信號干擾方面,以確保鏈路上的干凈,為減少干擾,走線時RF連接天線到RF_IN 輸入端要盡可能的短,以避免帶來更多的干擾。

走線50 歐姆的阻抗必須優先保證,其次包地線要有連續。

需要確保RF環路電路遠離系統板上的數字電路區域,要遠離 TCXO和32.768KHz晶體,在RF走線區其他層面上不能有其他信號走線穿過,同時需要有地包圍減少從數字地串擾進來的干擾,并確保做好明確的阻抗要求。

同時需要注意,RF接收部分對溫度變化引起的性能破壞非常敏感,RF鏈路盡可能遠離系統的熱發生

外加LNA器件走線要求:為了得到干凈的信號,減少板內信號輻射和其他地方竄進來的干擾,走線盡

量短且走直線,如圖3-23所示。如果因為PCB 布局的限制,走線無法走直線,則不能走“U”型甚“回”型走線,必須“L”型走線,如圖3-24所示。匹配電路器件擺放,要靠近芯片,串聯網絡必須無分叉。

完整的pdf格式文檔51黑下載地址:

N303-3雙模導航定位軟件協議.pdf

(3.44 MB, 下載次數: 57)

N303-3雙模導航定位軟件協議.pdf

(3.44 MB, 下載次數: 57)

2018-11-13 08:04 上傳

點擊文件名下載附件

|