|

|

HR7P153��Ƭ�Cpdf��ʽ��(sh��)��(j��)�փ��Y�Ϻ��\�ùPӛ�����o���

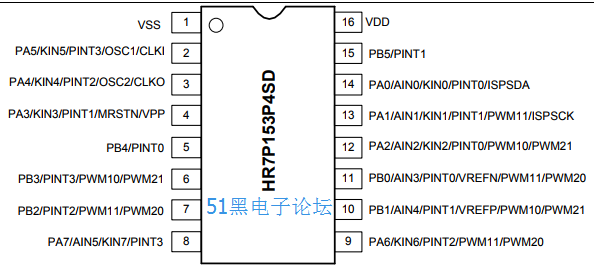

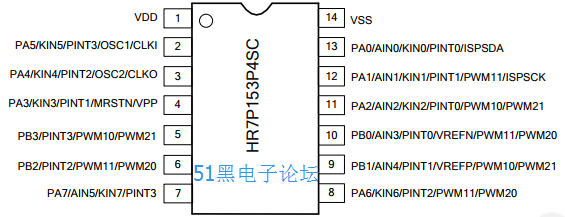

HR7P153���_�D��

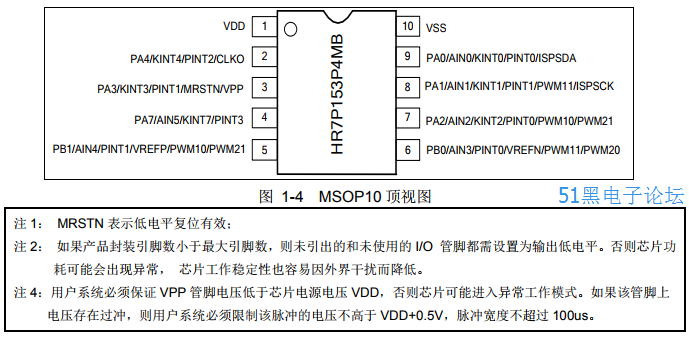

ע 1�� MRSTN ��ʾ���ƽ��λ��Ч��

ע 2�� ����a(ch��n)Ʒ���b���_��(sh��)С��������_��(sh��)���tδ�����ĺ�δʹ�õ� I/O ���_�����O�Þ�ݔ�����ƽ����tоƬ��

�Ŀ��ܕ����F(xi��n)������ оƬ������(w��n)����Ҳ���������ɔ_�����͡�

ע 4���Ñ�ϵ�y(t��ng)��횱��C VPP ���_늉�����оƬ�Դ늉� VDD����tоƬ�����M�뮐������ģʽ�����ԓ���_��

늉������^�_���t�Ñ�ϵ�y(t��ng)�������ԓ�}�_��늉������� VDD+0.5V���}�_���Ȳ����^ 100us��

2. 1 CPU��(n��i)�˸���

��(n��i)������

- �����ܹ����� RISC CPU ��(n��i)��

- 79 �l����ָ��

- ϵ�y(t��ng)�r犹����l����ߞ� 20MHz

- �C�����ڞ� 2 ��ϵ�y(t��ng)�r�����

- ֧���Д�̎������ 12 ���Д�Դ

2. 2 ϵ�y(t��ng)�r犺͙C������

ϵ�y(t��ng)�r��l�ʣ�Fosc�����֧�� 20MHz���ɂ�ϵ�y(t��ng)�r�����ͨ�^Ƭ��(n��i)�r��������a(ch��n)���ɂ����دB�������r� phase1��p1����phase2��p2�����ɂ����دB�������r����ڽM��һ���C�����ڡ���ϵ�y(t��ng)�r��l�ʞ� 4MHz��һ���C�����ڵĕr

�g�� 500ns��

2. 3 ָ�����

���� HR7P ϵ�� 79 �l����ָ�ϵ�y(t��ng)��

�����֗l�����D(zhu��n)�c���Ƴ������̵�ָ����p���C��������ָ���⣬����ָ�����Σ��C��������ָ����wָ�Ո��������� 1 ָ�����

2. 4 ����ܼĴ���

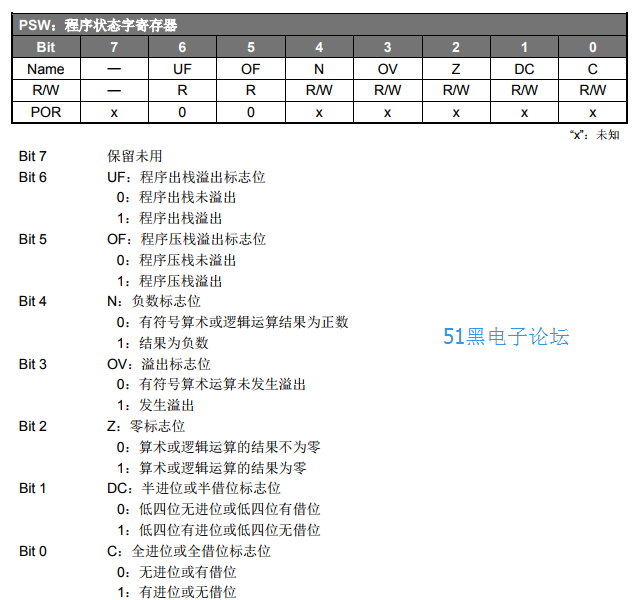

CPU ���P�Ĵ������� 11-bit ����Ӌ��(sh��)�� PCRL/PCRH�������B(t��i)�ּĴ��� PSW ���ۼ��� A �Ĵ��� AREG�����г����B(t��i)�Ĵ��� PSW ���ڴ�Ÿ�����B(t��i)��־λ�������������/���������ؓ��(sh��)��־λ�������־λ�����־λ�����Mλ/���λ��־λ���Լ�ȫ�Mλ��ȫ��λ��־λ�ȡ�

ע 1���H����ָ��Ɍ� PSW �Ĵ����M�Ќ����������� JDEC��JINC��SWAP��BCC��BSS��BTT��MOVA �� SETR������ָ� PSW �Ĵ����Č�������ֻ����(j��)�\�нY��Ӱ�������B(t��i)��־λ��

ע 2��OF �� UF λ��ֻ�x��־λ���H��늏�λ����λָ��� MRSTN ��λ���������㣬������λ��Ӱ�ԓ��λ��־λ��

3. 1 ����

��оƬ���ù����ܘ�������?q��)�ַ���g�͔�(sh��)��(j��)��ַ���g�������

Ƭ��(n��i)�惦���YԴ������

2K Words OTP ����惦����

64 �ֹ�(ji��) SRAM

���� OTP ����惦����ӳ�䵽����?q��)�ַ���g��SRAM ��(sh��)��(j��)�惦����ӳ�䵽��(sh��)��(j��)��ַ���g��

3. 2 ����惦��

3. 2. 1 ����

OTP ����惦�����ڴ惦�Ñ���������оƬָ��λ���� 16 λ��2 ���ֹ�(ji��)������� 2K Words

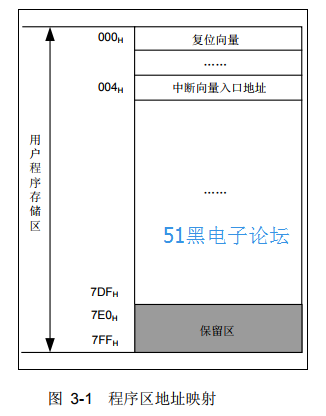

OTP ����惦����ӳ�䵽����?q��)�ַ���g�� 000H~7FFH������ 7E0H~7FFH �鱣��^(q��)��ÿ���L����ַ���� 16 λ����2 ���ֹ�(ji��)���Ĵ惦��Ԫ��ͨ�^ 11 λ����Ӌ��(sh��)�� PC �M�г���?q��)�ַ�L������λ����λ�� 000H���Д�������ڵ�ַλ�� 004H��֧�� 8 ��Ӳ���ї���

3. 2. 3 ����Ӌ��(sh��)����PC��

����Ӌ��(sh��)���д�ŵ���Ҫ��(zh��)�е���һ�lָ��ĵ�ַ��PC ��ÿ��ָ�����ں��ԄӼ� 1������ PC ��ֵ��ָ����Дஐ���Č���11 λ����Ӌ��(sh��)�� PC<10:0>���o���H������ַ�������x�����Ɍ�ַ 2K ����惦���g 000H ~ 7FFH��������ַ���������� PC ѭ�h(hu��n)���֏� 000H �_ʼ�L������

PC<7:0>��ͨ�^ PCRL �Ĵ������x/�������M���x/������ PC<10:8>ͨ�^ PCRH �Ĵ������g�ӣ��� RCALL��CALL��GOTO ��ָ��xֵ��

оƬ��λ�r��PCRL��PCRH �� PC ���������㡣PC Ӳ���ї���������Ӱ� PCRH ��ֵ��

ע�����Nָ� PC ��Ӱ푣�

1. ͨ�^ָ��ֱ���� PC ֵ�r���� PCRL ��Ŀ�˼Ĵ����IJ�����ֱ���� PC<7:0>���� PC<7:0>=PCRL<7:0>��

������ PC<7:0>��ͬ�rҲ����(zh��)�� PC<10:8>=PCRH<2:0>����ˣ��� PC �r�������� PCRH<2:0>������

�� PCRL<7:0>��

2. ��(zh��)�� RCALL ָ��r��PC<7:0>��Ĵ��� R �е�ֵ���� PC<10:8> =PCRH<2:0>��

3. ��(zh��)�� CALL��GOTO ָ��r��PC<10:0>��ָ���� 11 λ������(sh��) I��������(sh��)����

4. ��(zh��)�� LCALL ָ��r��ԓָ����p��ָ��� 16 λ������(sh��) I��������(sh��)����PC<10:0>���Ğ�ԓ 16 λ������(sh��) I

��ֵ�ĵ� 11 λ��ͬ�r PCRH<2:0>���Ğ� I<10:8>��ֵ��

5. ��(zh��)�� AJMP ָ��r��ԓָ����p��ָ��� 16 λ������(sh��) I��������(sh��)����PC<10:0> ���Ğ�ԓ 16 λ������(sh��) I

��ֵ�� 11 λ��ͬ�r PCRH<2:0>�Ğ� I<10:8>��ֵ��

6. ��(zh��)�� PAGE ָ��r��PCRH<7:3>��ֵ����ԓָ���������(sh��) I ��Q������оƬ�ij���惦����С�� 2K Words��

��� PCRH<7:3>���̶���ȫ�㣬��(zh��)�� PAGE ָ��� PC ֵ����Ӱ푣�

7. ��(zh��)������ָ��r��PC ֵ�ԄӼ� 1��

���Ì������� PCRL ��Ŀ�˼Ĵ�����ָ��ó���

����

MOVI pageaddr

MOVA PCRH ���O�ñ�������ַ

MOVI tableaddr ���O��ƫ�����o A �Ĵ���

CALL TABLE ���{(di��o)���ӳ���ʽ���

����

TABLE:

ADD PCRL, F ��PC ����ƫ������ָ���L���ĵ�ַ

RETIA 0X01

RETIA 0X02

RETIA 0X03

����

3. 2. 4 ����ї�

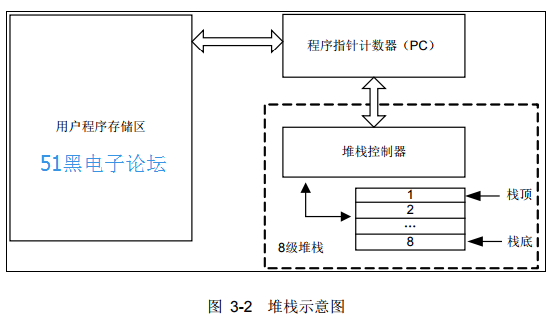

оƬ��(n��i)�� 8 ������ї���Ӳ���ї������ї�λ���c PC λ����ȣ����� PC �ĉ����ͳ�������(zh��)�� CALL��LCALL �� RCALL ָ����Д౻푑���PC �ԄӉ������o������(zh��)�� RET��RETIA �� RETIE ָ��r���ї��������һ�Ή�����ֵ������ PC��

����ї�ֻ֧�� 8 �����_������������ї�ֻ��������� 8 �Ή���ֵ�������B�m(x��)���^ 8 �εĉ����������� 9 �εĉ�����(sh��)��(j��)ʹ�õ� 1 �εĉ�����(sh��)��(j��)�Gʧ��ͬ�ӣ����^ 8 �ε��B�m(x��)�������� 9 �γ�������������ʹ�ó������̲��ɿء�оƬ��λ�ї�ָᘌ�����ָ��ї�픲���

3. 3 IAP�L��OTP����

3. 3. 1 OTP�惦��

OTP �惦����һ�οɾ��̴惦������ VPP ���ö˿�ʩ�Ӹ߉� 8.45V �r����ͨ�^ IAP ��δ

�����^�� OTP ��ַ��Ԫ�M��ܛ�����ƾ��̡�IAP ����������֣�Word�����λ��ͨ�^ FRA

��FRAH��F(xi��n)RAL����ַ���� OTP �惦���M�� IAP ��������r CPU ��(n��i)�˕�ͣ��(zh��)�У����O

�ɰ��A�O��B(t��i)�^�m(x��)�\�У����O���Д�Ո����λ�������Д���־���� IAP ���������ɕr��

CPU ��(n��i)�˻֏͈�(zh��)�С�

3. 3. 2 ���ָ��

HR7P 79 �lָ��а��� 8 �l���ָ�

����xָ�

����xָ�����ڌ� FRA��FRAH��F(xi��n)RAL����ָ��� OTP ��ַ��Ԫ�е�һ���֣�Word��

�x�� ROMD��ROMDH��ROMDL����

TBR

TBR#1

TBR_1

TBR1#

��팑ָ���оƬ��팑ָ���δ�á�

TBW

TBW#1

TBW_1

TBW1#

���ָ��ľ��w�����Ʌ�������� 1 ָ���

3. 3. 3 IAP����

IAP ���̲���ͨ�^ IAPC ���ƼĴ����� ROMD��ROMDH��ROMDL���еă�(n��i)���� FRA��FRAH��F(xi��n)RAL��ָ��� OTP ��ַ��Ԫ��IAP �����L����ַ���g���� 200H~7DFH�����hÿ����ַ������ɣ�����x����C�Ƿ�ɹ���������ɹ��践�ؾ��̲�����ֱ���x����C�ɹ����پ��̺��m(x��)��ַ���g���ε�ַ���̣����̕r�g���ٞ� 2ms��

�������� 1��IAP ����

MOVI 0x02 ���� 55AAH ���� OTP �� 0210H ��ַ��Ԫ

MOVA FRAH

MOVI 0x10

MOVA FRAL

MOVI 0xAA

MOVA ROMDL

MOVI 0x55

MOVA ROMDH

BSS IAPC, IAPEN ��ʹ�� IAP ����

BSS IAPC, IAPGO ���|�l(f��) IAP ����

WAIT:

JBC IAPC, IAPGO

GOTO WAIT

......

�������� 2��IAP ����x

MOVI 0x02 ���xȡ��(sh��)��(j��)�惦�� 0210H ��Ԫ

MOVA FRAH

MOVI 0X10

MOVA FRAL

TBR ������xָ��xȡ��(sh��)��(j��)�� ROMDH/L �Ĵ���

MOV ROMDH, 0

�� ��

MOV ROMDL, 0

�� ��

3. 4. 3 ͨ�Ô�(sh��)��(j��)�惦��

ͨ�Ô�(sh��)��(j��)�惦���������R�r��Ŕ�(sh��)��(j��)�Ϳ�����Ϣ�������ڳ���������M���x����������оƬͨ�Ô�(sh��)��(j��)�惦�����g�� 64 Bytes����ַ������ 0000H~003FH��ͨ�Ô�(sh��)��(j��)�惦���ă�(n��i)������늏�λ���Dz��_���ģ�δ��늵�������λ�������λǰ�ă�(n��i)�ݡ�

3. 4. 4 ����ܼĴ���

����ܼĴ�������оƬ�����O�����Ŀ����O������оƬ֧�� 128 ������Ĵ�������ַ���� FF80H~FFFFH�������(sh��)�Ĵ������ǿ����x���ģ��H���ٔ�(sh��)���ּĴ����������_�š����P������ʹ�õļĴ������քe�ڸ����¹�(ji��)��������

3. 4. 5 ��ַ��ʽ

SRAM ��(sh��)��(j��)�惦���Č�ַ��ʽ֧��ֱ�ӌ�ַ���g�ӌ�ַ��

3. 4. 5. 1 ֱ�ӌ�ַ

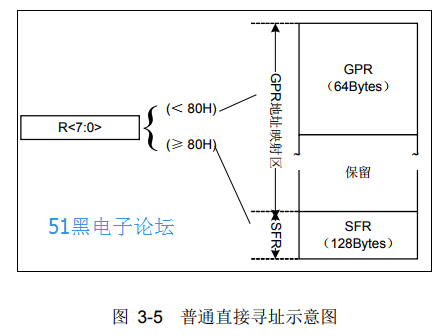

��ֱ�ӌ�ַ�r��ָ���е� 8 λ��ַ��Ϣ���� GPR �� SFR ��ַ����ָ���е� 8 λ��ַ��ϢR<7:0>С�� 80H�r��ֱ�ӌ�ַ GPR ӳ��^(q��)���� R<7:0>���ڻ���� 80H�r��ֱ�ӌ�ַ SFRӳ��^(q��)��

3. 4. 5. 2 �g�ӌ�ַ

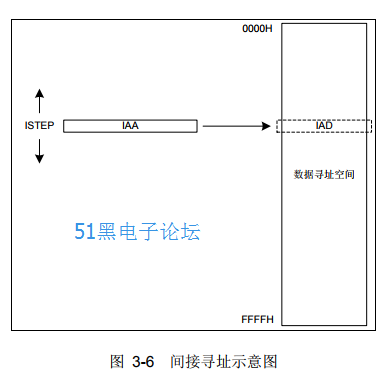

�g�ӌ�ַ��ͨ�^ 16 λ�g�ӵ�ַ�Ĵ��� IAA���� 2 �� 8 λ�Ĵ��� IAAH �� IAAL �M�ɣ��� 8λ̓�M��(sh��)��(j��)�Ĵ��� IAD �g���L����(sh��)��(j��)��ַ���g�еĴ惦��Ԫ����ַ���g�� 0000H~ FFFFH���Ȍ��L��Ŀ�ĵ�ַ������g�ӵ�ַ�Ĵ��� IAA����ͨ�^ָ� IAD �M���x/�����������H���x/����������t�� IAA ָ��Ĕ�(sh��)��(j��)��ַ���g�е�Ŀ�ĵ�ַ��Ԫ��

���� IAD �Ĵ�������Ҳӳ�䵽��(sh��)��(j��)��ַ���g�� FF80H ��ַ����ˣ��� IAA ��ŵĵ�ֵַ�� FF80H �r���x/�� IAD �ஔ�����g�ӌ�ַ��ʽ�L��̓�M�Ĵ��� IAD �������˕r�x������ʼ�K�x���� 00H���������t��һ���ղ���������Ӱ푠�B(t��i)λ����

ISTEP ָ��Á팦 16 λ�g�ӌ�ַ�Ĵ��� IAAH/IAAL �M��ƫ�Ʋ�������(zh��)��ԓָ��r���Ȍ�ָ�����е� 8 λ�з�̖������(sh��)�M�з�̖λ�Uչ�� 16 λ��(sh��)���ٌ� IAA ��ֵ�����@����(sh��)�ĽY����� IAA �Ĵ�����ISTEP �Ɍ��F(xi��n)��ƫ�Ʒ�����-128~127���mȻֻ�� 8 λ������(sh��)������ԓ�lָ�����IAA(IAAL��IAAH)�M��16λӋ�㡣Ӌ��ĽY����Ȼ�����IAAL��IAAH�С�

�������̣������g�ӌ�ַ����020H ~ 02FH���ļĴ������㡣

����

CLR IAAH

MOVI 0X20 ����ָᘳ�ʼ��

MOVA IAAL ��IAA ָ�� RAM

NEXT1:

CLR IAD ������ IAD �Ĵ���

ISTEP 0X01 ��ָ� IAA ��(n��i)�ݼ� 1

JBS IAAL, 4 ��

GOTO NEXT1 ��δ��ɣ�ѭ�h(hu��n)����һ����Ԫ����

CONTINUE: ���ѽ�(j��ng)��ɣ��^�m(x��)��(zh��)�к���ij���

����

�� 4 �� ݔ��/ݔ���˿�

4. 1 ����

ݔ��/ݔ���˿���оƬ��������M�ɲ��֣���оƬ���֧�� 13 �� I/O �˿ں� 1 ��ݔ��˿ڡ�

һ��ݔ��˿� PA3 �� TTL ݔ�룬�������� I/O �˿ڶ��� TTL/SMT ݔ��� CMOS ݔ���(q��)

�ӡ�

PA ݔ��/ݔ���˿ڹ��ܽM��

- 7 λ�p��ݔ��/ݔ���� 1 λݔ��˿�

- TTL/SMT ݔ��� CMOS ݔ���(q��)��

- �˿�ݔ��/ݔ�����ƼĴ�����PAT��

- �˿����������ƼĴ�����N_PAU��

- �˿����������ƼĴ�����N_PAD��

- PA0~PA7 ֧���ⲿ���I�Д��

- PA0~PA2��PA7 I/O �˿ڔ�(sh��)ģ�x��Ĵ�����ANS��

PB ݔ��/ݔ���˿ڹ��ܽM��

- 6 λ�p��ݔ��/ݔ���˿�

- TTL/SMT ݔ��� CMOS ݔ���(q��)��

- �˿�ݔ��/ݔ�����ƼĴ�����PBT��

- �˿����������ƼĴ�����N_PBU��

- �˿����������ƼĴ�����N_PBD��

- PB0~PB5 ֧���ⲿ�˿��Д��

- PB0~PB1 I/O �˿ڔ�(sh��)ģ�x��Ĵ�����ANS��

ע 1�����˿��O�Þ�ݔ�����ⲿ��ʎ���r状˿ڕr����(n��i)������/�����Ԅӽ�ֹ��

4. 3. 3 I/O�˿ڴ�������ƹ���

�Ĵ��� N_PBD<5>��PLCS���ɿ��ƶ˿� PA��PA7-4��PA2-0����PB��PB5-0��������(q��)��������

4. 3. 4 I/O�˿�ģ�M/��(sh��)������x����

����(sh��)����̖��ģ�M��̖���ù��_�r����ʹ�Ì����˿ڵĔ�(sh��)����̖��ģ�M��̖����ǰ������_�O�ö˿ڵ���ͣ���t���ܲ����_���A�ڵĽY������оƬ�� PA0~PA2, PA7, PB0~PB1 �˿ھ����Ъ�����ģ�M/��(sh��)����̖�x���ܣ��� ANS �Ĵ��������x���˿ڱ����Þ�ģ�M�˿ڕr���x���� Px �Ĵ���ʼ�K�x����0����

4. 3. 5 I/O�˿ڏ��ù���

����ʹ�YԴ���������(y��u)������оƬ�ֵ� I/O �˿ڶ����Џ��ù��ܡ����˿����ڏ��ù��ܕr�����_�ƽ�ɏ��ù��ܛQ����

4. 4 �˿��Д�

4. 4. 1 ���I�ДࣨKINT��

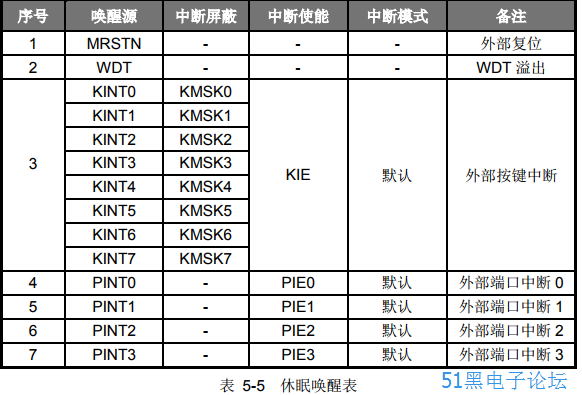

��оƬ�ⲿ�˿�֧�� 1 �M�ⲿ���I�Дࡣ���I�Д�֧����� 8 �����Iݔ��� KIN<7:0>�� 8 �����I����һ�����I�Д�ʹ��λ KIE��INTE0<0>�������I�Д���־λ KIF��INTF0<0>����ÿ��ݔ��˿����������İ��I����λ KMSKx��INTC0<7:0>�����Σ��κ�����һ�����I�Д�a(ch��n)����Ӱ��Д���־ KIF��

�� KINn ���ö˿ڱ����Þ锵(sh��)��ݔ��˿ڣ��� 1 �M���κ�һ���˿�ݔ����̖�l(f��)���ƽ׃���r�����a(ch��n)�����I�Д� KINT��ʹ���ⲿ���I�Д��r������������Ŀ��ƼĴ���������ʹ���ⲿ���I�Д�˿ڵă�(n��i)����������衣�ⲿ���I�ƽ���^���DZ��^���Iݔ��˿��ƽ�c�i�����ϵ����ݔ��ֵ��������I�Д���־λǰ����회��������ö˿��M��һ���x/����������t���I�Д���־λ�o����������ڰ��I�Д�ʹ�ܣ�KMSKn=1��KIE=1��ǰ���Ȍ��˿ڼĴ����M���x���ߌ��IJ���������Д���־λ�������`�a(ch��n)���Дࡣ���Д��܌�оƬ��˯�ߠ�B(t��i)���ѡ�

4. 4. 2 �ⲿ�˿��ДࣨPINT��

��оƬ�ⲿ�˿�֧�� 4 ���ⲿ�˿��Д࣬�ⲿ�Д�Դ���ⲿ�Д��x��λ PINT3S~PINT0S��PINTS<7:0>���x���ⲿ�˿��Д��������� PIE3~PIE0��INTE1<3:0>��ʹ�ܣ�ͨ�^PEG3~PEG0��INTC1<3:0>���x���������|�l(f��)߀���½����|�l(f��)���� PINTn ���ö˿ڱ����Þ锵(sh��)��ݔ��˿ڣ���ݔ����̖׃���M���|�l(f��)�l���r�����a(ch��n)�� PINTn �ⲿ�˿��Д࣬�Д�a(ch��n)����Ӱ��������Д���־ PIFn��INTF1<3:0>�������Д��܌�оƬ��˯�ߠ�B(t��i)���ѡ�

4. 5 I/O�˿ڲ���ע�����

����(zh��)���Զ˿ڼĴ�����Ŀ�˵IJ�������λ����ָ��r��оƬ���H��(zh��)���x-��-���^�̣������xȡԓ�Mȫ�� I/O �˿ڵ��ƽ���ĺ��ٌ��ض˿ڼĴ�����λ����ָ� I/O ���IJ���ֻӰ��x����λ������Ӱ�ͬ�M���� I/O �˿ڡ���˽��h�Ñ� I/O ���IJ���λ����ָ������Ñ��ڌ� I/O �˿ڵď��ù���ʹ�ܺ��P�]�r������ֿ��]��ǰ I/O �˿ڵ�ݔ���Ĵ���ֵ�����Д��Ƿ���Ҫ�����@Щ I/O �˿��M�г�ʼ���xֵ��

4. 6 ����ܼĴ���

ݔ��/ݔ���˿ڵ��O�ð���һϵ�еļĴ������ƣ�PX �Ĵ��������@ʾ PX �˿ڵ��ƽ��B(t��i)��PXT �Ĵ��������O�� PX �˿ڵ�ݔ��ݔ����B(t��i)��N_PXU / N_PXD �����O�� PX �˿ڵ������� / �����������B�Ӡ�r��ANS �����O�� PX �˿ڵĔ�(sh��)��(j��)��͡�

�� 5 �� ����ܼ���������

5. 1 ϵ�y(t��ng)�r��c��ʎ��

5. 1. 1 ����

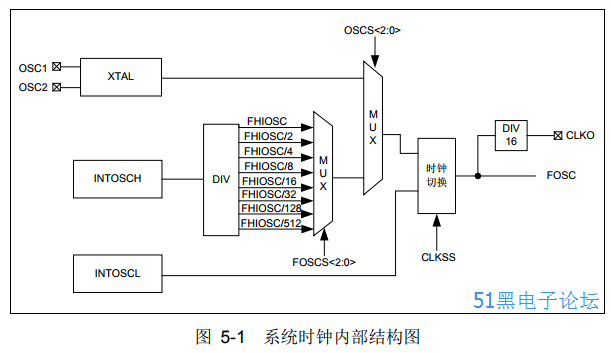

оƬ�\������Ҫ�ĕr�Դ����ʎ���ṩ����ͬ����ʎ���x�����ʹ�����ڲ�ͬ�đ��������Ќ��F(xi��n)�����Ĺ��ܡ�����оƬ���ṩ����ʎ�������N���ⲿ���w/�մ���ʎ��XTAL����(n��i)������RC��ʎ��(16MHz)�̓�(n��i)������RC��ʎ��(32KHz)���`���x����ʎ����ʹ�îa(ch��n)Ʒ���ٶȺ��ķ�������_���(y��u)�����ⲿLP��ʎ���̓�(n��i)������RC��ʎ����������ϵ�y(t��ng)�r�Դ�⣬߀���Ԟ鿴�T�����r�����ṩ����Ҫ�ĕr�Դ��

��ʎ��ģʽ

- �ⲿ��ʎ����HS/XT/LP��

- ��(n��i)�� 16MHz RC ��ʎ���������Þ� INTOSC �� INTOSCO��

- ��(n��i)�� 32KHz RC ��ʎ��

��(n��i)�� 16MHz RC ��ʎ��

- 8 λУ�ʼĴ�����OSCCAL��

- ���Sǰ���ڳ������ѽ�(j��ng)У�ʵ����Ȟ��2%

- ֧�ֶ�N���l�r�

��(n��i)�� 32KHz RC ��ʎ��

- 8 λУ�ʼĴ�����WDTCAL��

ϵ�y(t��ng)�r��ГQ

- HS/XT/INTOSCH 16MHz ��ʎ�r��c��(n��i)������ INTOSCL 32KHz �r��ГQ

- �ⲿ���� LP ��ʎ�r��c��(n��i)������ INTOSCH 16MHz �r��ГQ

��ʎ�͕�ͣ

- �� IDLE0 ģʽ�£���ʎ����ͣ��ʎ

- �� IDLE1 ģʽ�£���ʎ��������ʎ��ϵ�y(t��ng)�r犕�ͣ

5. 1. 2. 1 �ⲿ�r�

�ⲿ�r犰������w/�մ���ʎ��ģʽ��HS/XT/LP�������ھ��w/�մ���ʎ�����ԣ�ֻҪ���ε،����w�B���� OSC1 �� OSC2 ���_�g���͕��a(ch��n)����ʎ��������Ƽ��������鱣�C��ʎ�l�ʸ����ʣ����B�Ӄɂ�С������� C1 �� C2 �� VSS�����w��(sh��)ֵ�c��ʹ�õľ��w/�մ���ʎ�����P����݅���ȡֵ������ 15~33pF������(j��)���x�����ʎ���l�ʣ��ɷ֞����Nģʽ��HS ģʽ��XT ģʽ�� LP ģʽ����оƬ������ OSCS<2:0> = 000 �r���x�� LP ģʽ����OSCS<2:0> = 010 �r���x�� HS ģʽ����оƬ������ OSCS<2:0> = 100 �r���x�� XT ģʽ��оƬ������ OSCS<2:0>�͑�ͨ�^���̽����x��

���w/�մ���ʎ��ģʽ��HS��XT��LP ģʽ��

HS/XT ��������(w��n)���r�g�� 512 ��ϵ�y(t��ng)�r犡�LP �����OӋ�������ʎ������(w��n)���r�g�sһ�����ҡ�

5. 1. 2. 2 ��(n��i)������ 16MHz RC��ʎ��ģʽ(INTOSCH)

оƬ��(n��i)�� 16MHz RC �r���ʎ��������Ҫ������� �ⲿ�������� �������е�OSCS<2:0>=000/110/111�ҼĴ���OSCC�е�CLKSS=1�r���x���(n��i)��16MHz RC����ϵ�y(t��ng)�r�Դ���˕rPA2��PA3���_���Þ�ͨ��I/O�˿ڡ�INTOSCH 16MHz��Ϳɷ��l��32KHz�����Sǰ����(n��i)��16MHz RC�r���ʎ�����ڳ�����У�ʡ�оƬ��늕r�����ԄӼ��dУ��ֵ���͑�����Ҫ��У�ʼĴ���OSCCAL�M���κβ�����

5. 1. 2. 3 ��(n��i)������ 32kHz RC��ʎ��ģʽ(INTOSCL)

оƬ��(n��i)��32KHz RC�r���ʎ��������Ҫ��������ⲿ������������WDTӋ��(sh��)�r�Դ��Ҳ�����Þ���ϵ�y(t��ng)�r�Դ�����������е�OSCS<2:0>=010/100/110/111�ҼĴ���OSCC�е�CLKSS=0�r���x���(n��i)��32KHz RC����ϵ�y(t��ng)�r�Դ���˕rPA��PA3���_���Þ�ͨ��I/O�˿ڡ�оƬ��늕r�����ԄӼ��dУ��ֵ���͑�����Ҫ��У�ʼĴ���WDTCAL�M���κβ�����5. 1. 3 ϵ�y(t��ng)�r��ГQ

���l�r����ṩϵ�y(t��ng)���ߵ����ܣ����l�r��܉��ṩ���͵Ĺ��ġ���ˣ�����(j��)�Ñ���Ҫ���`��ذ��Ÿߵ��l�r��ГQ������ʹϵ�y(t��ng)�ڈ�(zh��)���ٶȺ��ķ����(y��u)����ϵ�y(t��ng)��ܛ���O�üĴ���λ CLKSS��OSCC<7>�����x��ߡ�����ϵ�y(t��ng)�r犡�ϵ�y(t��ng)��늕r���Ĵ��� CLKSS ��ֵĬ�J�� 0�������ڵ���ϵ�y(t��ng)�r�ģʽ�¡�

ϵ�y(t��ng)֧���ķN�r��ГQ��

��(n��i)������ INTOSCL 32KHz �r��ГQ����(n��i)������ INTOSCH/�ⲿ���� HS/XT �r�

- �O��оƬ������ CFG_WD �е� OSCS<2:0>=010/100/110/111��

- �O�� OSCC �Ĵ����е� CLKSS=1��

- �z�y OSCC �Ĵ����е� HSOSCF λ��ֱ���z�y�� HSOSCF=1��

- �ȴ�һ�l NOP ָ�

- �z�y PWEN �Ĵ����� SW_HS λ��ֱ���z�y�� SW_HS=1��

��(n��i)������ INTOSCH/�ⲿ���� HS/XT �r��ГQ����(n��i)������ INTOSCL �r�

- �O��оƬ������ CFG_WD �е� OSCS<2:0>=010/100/110/111��

- �O�� OSCC �Ĵ����е� CLKSS=0��

- �z�y OSCC �Ĵ����е� WDTOSCF λ��ֱ���z�y�� WDTOSCF =1��

- �ȴ�һ�l NOP ָ�

- �z�y PWEN �Ĵ����� SW_WDT λ��ֱ���z�y�� SW_WDT =1��

�ⲿ���� LP �r��ГQ�� INTOSCH �r��

- �O��оƬ������ CFG_WD �е� OSCS<2:0>=000��

- �O�� OSCC �Ĵ����е� CLKSS=1��

- �z�y OSCC �Ĵ����е� HSOSCF λ��ֱ���z�y�� HSOSCF=1��

- �ȴ�һ�l NOP ָ�

- �z�y PWEN �Ĵ����� SW_HS λ��ֱ���z�y�� SW_HS=1��

��(n��i)������ INTOSCH �r��ГQ���ⲿ���� LP �r�

- �O��оƬ������ CFG_WD �е� OSCS<2:0>=000��

- �O�� OSCC �Ĵ����е� CLKSS=0��

- �z�y OSCC �Ĵ����е� LPOSCF λ��ֱ���z�y�� LPOSCF =1��

- �ȴ�һ�l NOP ָ�

- �z�y PWEN �Ĵ����� SW_LP λ��ֱ���z�y�� SW_LP =1��

5. 2 ���T�����r��

5. 2. 1 ����

���T�����r����оƬ��һ���M�ɲ��֣����Ĺ��������ڰl(f��)��ܛ�����ϕr��ͨ�^������λ��

оƬ��λ����ϵ�y(t��ng)�M�����e�`�Ĺ�����B(t��i)�����T�������ں����ĕr�g������(n��i)ʹоƬ��λ��

ʹ�ܿ��T���r�����Ñ�����������T�����r��ʧ�����t���A���ĕr�g������(n��i)�����T����ʹ

ϵ�y(t��ng)��λ��

WDT ���r��

- 8 λ WDT ���rӋ��(sh��)�����o���H������ַ�������x����

- 8 λ�A���l�����o���H������ַ�������x����

- WDT ���ƼĴ�����WDTC��

- WDT Ӌ��(sh��)����ƥ��Ĵ�����WDTP��

- ���ѹ���

- �����

��(n��i)�� WDT RC ��ʎ��

- ���r���r�Դ���(n��i)�� 32KHz RC �r犻��ⲿ LP ��ʎ�r�

- 8 λ WDT �r�У�ʼĴ�����WDTCAL��

- ���Sǰ���ڳ������ѽ�(j��ng)���l��У���ڡ�15%�ԃ�(n��i)����ߵ͜��lƫ�� WDT Ӌ��(sh��)

������ڵ�Ӱ푣�Ҋ��늚����ԡ��¹�(ji��)������

5. 2. 3 WDT���r��

оƬ�ṩ8λWDT���rӋ��(sh��)����ͨ�^оƬ������WDTEN��ʹ��Ӳ�����T��WDT����оƬ������WDTENʹ�ܕr��WDT���r��Ӌ��(sh��)ʹ�ܣ���WDTEN�P�]�r��WDT���r��Ӌ��(sh��)��ֹ���͑�ͨ�^���̽����x��

�������� OSCS<2:0>λ���Þ� LP ģʽ�r��WDT ��Ӌ��(sh��)�r�Դ�ЃɷN�x��(n��i)�� 32KHzRC �r犺��ⲿ LP ��ʎ�r犡���� WDTCKS=0 �r��WDT ��Ӌ��(sh��)�r犞� WDT RC �r犣��� WDTCKS=1 �r��WDT ��Ӌ��(sh��)�r犞� LP ��ʎ�r犡�WDT ֧��һ���A���l������ͨ�^ WDTC �Ĵ����е� WDTPRS<3:0>λ�O�� WDT �r�Դ���A���l�ȣ��ٌ����l��ĕr���̖���� WDT ���r����Ӌ��(sh��)�r犡��� WDTPRE

��WDTC<4>�����㣬��ֹ�A���l����WDT �r犞� 32KHz���� WDTPRE��WDTC<4>���� 1��ʹ���A���l����

WDT ֧��һ�M���x/���Ķ��r���ڼĴ��� WDTP�������T��Ӌ��(sh��)�����r���ڕr�����r������� IDLE ģʽ�£�WDT Ӌ��(sh��)��������� CPU�����⣬WDT Ӌ��(sh��)�������λоƬ�����˱��ⲻ��Ҫ�ď�λ����ʹ�� CWDT ָ���m�r���� WDT Ӌ��(sh��)����

���A���l�����l�Ȟ� 1:2�������ڼĴ��� WDTP �O�Þ� FFH �r��WDT ʹ�Ã�(n��i)�� WDT �r��M��Ӌ��(sh��)�������r��l�ʼs�� 32KHz��Ӌ��(sh��)����r�g�s�� 16ms������ֹ�A���l���r��WDT ��Ӌ��(sh��)����r�g�s�� 8ms�� ���������l���£�WDT ��Ӌ��(sh��)����r�g���Ʌ�������� ����(sh��)���ԈD���¹�(ji��)�����P�Dʾ��

ֵ��ע����ǣ��� WDT ��(n��i)�� RC �r�ʹ��λ RCEN=0 �r��ֻ�� IDLE ģʽ�¿��T����ֹ����������ģʽ�� WDT �� RC �r�һֱ���_������ RCEN ��Ӱ푡�

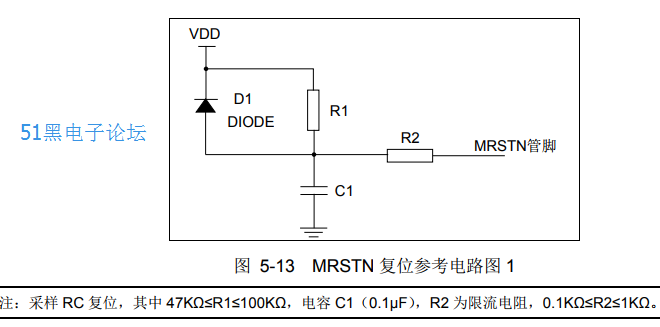

5. 3. 4 �ⲿMRSTN���_��λ

оƬ�ṩ�ⲿ MRSTN ���_���� CFG_WD<5>��MRSTEN���� 1 �r������ϵ�y(t��ng)��λ������λ���_ݔ����ƽ��̖�r��ϵ�y(t��ng)��λ������λ���_̎�ڸ��ƽ�r��ϵ�y(t��ng)�����\�С���Ҫע����ǣ���ϵ�y(t��ng)�����ɺ��ⲿ��λ���_���ݔ����ƽ����tϵ�y(t��ng)��һֱ�����ڏ�λ��B(t��i)�����⣬��Ҫ�eע����ǣ���ֹ�� MRSTN ���_ֱ���B�ӵ� VDD �ϣ���ֹ MRSTN ���_�ϵ�늉����� VDD 늉���

�ⲿ MRSTN ���_��λ�·�ж�N�����½�B�ɷN���^���͵��B���·��

1. RC ��λ

RC ��λ�·���ⲿ MRSTNN �_��λ�·��ε�һ�N�������h(hu��n)���l��Ҫ�ߵ���r�£����Բ��ô˷N�B�ӷ�ʽ��

5. 4. 1 MCU����ģʽ

��оƬ֧�փɷN��������ģʽ��IDLE0 ģʽ�� IDLE1 ģʽ��ͨ�^�O�� PWRC �Ĵ���λ

LPM��PWRC<7>���M���x��

֧�� IDLE0 ģʽ

- �� LPM = 0 �r����(zh��)�� IDLE ָ�оƬ�M�� IDLE0 ģʽ��

- �r�Դͣ��32KHz RC �r�Դ���⣩����ϵ�y(t��ng)�r犕�ͣ

- ����ͣ��ͬ��ģ�K��ͣ������ģ�K�\�У��������Ľ���

- ֧�ֵ��Ć��ѣ����ѕr�g���䣬ͬ�r��Ҫ���] LDO ��(w��n)���r�g

- ���� I/O �˿ڌ������M�� IDLE0 ģʽǰ�Ġ�B(t��i)

- ��ʹ�� WDT���t WDT �������㲢�����\��

- N_PD λ�����㣬N_TO λ���� 1

֧�� IDLE1 ģʽ

- �� LPM = 1 �r����(zh��)�� IDLE ָ�оƬ�M�� IDLE1 ģʽ��

- �r�Դ�����\�У���ϵ�y(t��ng)�r犕�ͣ

- ����ͣ��ͬ��ģ�K��ͣ������ģ�K�\�У��������Ľ���

- ֧�ֵ��Ć��ѣ����ѕr�g���䣬��С 1 ���C������

- ���� I/O �˿ڌ������M�� IDLE1 ǰ�Ġ�B(t��i)

- ��ʹ�� WDT���t WDT �������㲢�����\��

- N_PD λ�����㣬N_TO λ���� 1

5. 4. 2 ����ģʽ����

�ɷN����ģʽ IDLE0 �� IDLE1 ģʽ���x���� PWRC �Ĵ����е� LPM λ���ơ��� LPM

= 0 �r����(zh��)�� IDLE ָ�оƬ�M�� IDLE0 ģʽ���� LPM = 1 �r����(zh��)�� IDLE ָ�оƬ

�M�� IDLE1 ģʽ��

���˽����ģ����� I/O ���_�������֞� VDD �� VSS�����˱���ݔ����_�ҿն������_

�P����������ⲿ������ݔ��� I/O ���_������ƽ����ƽ��MRSTN ���_���̎��߉

���ƽ��

5. 4. 3 IDLE���ѷ�ʽ����

��ϵ�y(t��ng)�M�����ģʽ����̎�ڕ�ͣ��B(t��i)�����N��ʽ�Ɍ�ϵ�y(t��ng)���ѡ�

ע 1�����Ć����cȫ���Д�ʹ�ܟo�P��ֻ�������Д�Դʹ��λ��λ�顰1�����ɡ��ڵ���ģʽ�r�������O�a(ch��n)���Д�

��̖����ʹȫ���Д�ʹ�� GIE �� 0������ģʽ��Ȼ�������ѣ�ֻ�dž��Ѻ���(zh��)���Д����

ע 2���P���ⲿ���I�Д�ʹ�ã����_���Д�ʹ�ܺ��Д�����λʹ��ǰ���Ȍ��˿ڼĴ����M���x���ߌ��IJ�����Ȼ��

����Д���־λ�������`�a(ch��n)���Дࡣ

�������¼��l(f��)����оƬ����(j��)������ OSCS<2:0>�����È�(zh��)������������

�� OSCS<2:0>���Þ� HS/XT/INTOSCO/INTOSC ģʽ�r��

- �� IDLE0 ģʽ��LPM=0���£�оƬ��Ҫ�ȵȴ� VRwkdly �r�g���� VRST��PWRC<6:5>���O�������˕r�g�Q�� LDO ��(w��n)���r�g��֮��оƬ���r��\��һ��Twkdly �r�g��ň�(zh��)�� IDLE ��һ�lָ�Twkdly �Q�醾���ӕr�������ӕr��ͨ�^ WKDC �Ĵ����O�ã�

- �� IDLE1 ģʽ��LPM=1���£�оƬ�H�ȴ� Twkdly �r�g��͈�(zh��)�� IDLE ��һ�lָ��o VRwkdly �r�g��

�� OSCS<2:0>���Þ� LP ģʽ�r��

- �� IDLE0 ģʽ��LPM=0���£�оƬ��Ҫ�ȵȴ� VRwkdly �r�g���� VRST��PWRC<6:5>���O�������˕r�g�Q�� LDO ��(w��n)���r�g������оƬ�ȴ� LPwkdly �r�g��֮��оƬ���r��\��һ�� Twkdly �r�g��ň�(zh��)�� IDLE ��һ�lָ�Twkdly�Q�醾���ӕr�������ӕr��ͨ�^ WKDC �Ĵ����O�ã�

- �� IDLE1 ģʽ��LPM=1���£�оƬ�H�ȴ� Twkdly �r�g��͈�(zh��)�� IDLE ��һ�lָ��o VRwkdly �� LPwkdly �r�g��

�� 6 �� ���O

6. 1 8 λPWM�r�����r����T8P1/T8P2��

6. 1. 1 ����

��оƬ���� 2 �M PWM �r�����r����T8P1/T8P2����֧�փɷN����ģʽ�����r��ģʽ�� PWM

ģʽ�����r��ģʽ����(j��)�Ĵ����ƶ��Ķ��r�r�g�M�ж��r������ʹ���r�����x��خa(ch��n)���Д�Ո

����������������PWM ģʽ���� PWM ݔ����

T8Pn ֧�փɷN����ģʽ���r�Դ��ϵ�y(t��ng)�r� 2 ���l��Fosc/2����

- ���r��ģʽ

- PWM ģʽ��֧����� 11 λ PWM ƽ��ݔ�����ȣ�֧�� PWM �����^(q��)���aݔ����

�����^(q��)�r�gܛ��������

T8Pn ֧�����¹��ܽM��

- 4 λ���A���l���� 8 λ����l�����o���H������ַ��ܛ�������x����

- 8 λӋ��(sh��)����T8Pn��

- 8 λ���ȼĴ�����T8PnR��

- 8 λ���ڼĴ�����T8PnP��

- 8 λ���ھ��_����PRDBUF���o���H������ַ��ܛ�������x����

- 8 λ���Ⱦ��_����RESBUF���o���H������ַ��ܛ�������x����

- 8 λ T8Pn PWM ���^(q��)���ƼĴ�����T8PnPDT��

- ���ƼĴ�����T8PnC��

- T8PnPEX ����l�ȔUչ�Ĵ�����T8P1PEX/T8P2PEX��

- T8Pn ����ƥ����ƼĴ�����T8P1PMC/T8P2PMC��

- T8Pn ݔ�����ƼĴ�����T8P1OC��

- 8 λ T8Pn PWM ���^(q��)���ƼĴ�����T8PnPDT��

�Д�͕�ͣ

- ֧��ƥ���Д���־��T8PnTIF���������Д�(T8PnPIF)

- ֧���Д�̎��

- �� IDLE ģʽ�£�T8Pn ��ͣ����

6. 1. 4 �A���l���ͺ���l��

�A���l���ͺ���l�������ṩһ�����L��������Д����ڡ�T8Pn ģ�KӋ��(sh��)��֧�ֿ����õ�4 λ�A���l���Ϳ����õ� 8 λ����l�����A���l���c����l����Ӌ��(sh��)ֵ���o���x������T8Pn �Ŀ��ƼĴ�����Ӌ��(sh��)���������A���l���ͺ���l�����㣬������׃���l���O�á��A���l���ķ��l�ȿ�ͨ�^ T8PnC �Ĵ����е� T8PnPRS<1:0>λ�M���O�ã��A���l�ȷ�����1:1~1:16������l���ķ��l�ȿ�ͨ�^ T8PnC �Ĵ����е� T8PnPOS<3:0>λ�ͺ���l�ȔUչ�Ĵ��� T8PnPEX �е� T8PnPOSEX<3:0>�M���O�ã�����l�ȷ����� 1:1~1:256��

6. 1. 5 ����ģʽ

T8P1/T8P2 �ЃɷN����ģʽ�����r��ģʽ�� PWM ģʽ��ͨ�^ T8PnM �Ĵ����M��ģʽ�x

�ɷNģʽ��֧���A���l���ͺ���l�����ɷNģʽ�£�T8Pn Ӌ��(sh��)���ĕr�Դ����ϵ�y(t��ng)�r

� 2 ���l��Fosc/2����

6. 1. 6 ���r��ģʽ

�� T8PnM=0 �� T8PnE=1 �r��T8Pn �����ڶ��r��ģʽ��

�ڶ��r��ģʽ�£�T8Pn Ӌ��(sh��)���ĕr�Դ��ϵ�y(t��ng)�r� 2 ���l��Fosc/2�������x���A���l����Ӌ��(sh��)�r��M�з��l��Ӌ��(sh��)����Ӌ��(sh��)�r犞���l��ĕr犡�

�ڶ��r��ģʽ�£��� T8PnPMS=0 �r�����������ھ��_�� PRDBUF��T8Pn ��Ӌ��(sh��)ֵ�c���ڼĴ��� T8PnP �M�б��^ƥ�䣻�� T8PnPMS=1 �r���������ڼĴ��� T8PnP ��ֵ�����ھ��_�� PRDBUF��T8Pn ��Ӌ��(sh��)ֵ�c���ھ��_�� PRDBUF �M�б��^ƥ�䡣�� T8Pn ��Ӌ��(sh��)ֵ�c���ڼĴ��� T8PnP���� T8PnPMS=0�����c���ھ��_�� PRDBUF����T8PnPMS=1��ƥ����ȕr���������Д���־ T8PnPIF �� 1��ԓ�Д���־��Ҫܛ�����㡣ͬ�r T8Pn ���Ԅ����㲢�����_ʼӋ��(sh��)��ͬ�r����l���� 1 Ӌ��(sh��)��������l����Ӌ��(sh��)ֵ�c����l�����l����ͬ�r����λ����l�����������r�Д���־ T8PnTIF �� 1��ԓ�Д���־��Ҫܛ�����㡣

�ڶ��r��ģʽ�£����ھ��_�� PRDBUF �ĸ��£�

�ڶ��r��ģʽ��ʼ���ڣ������܌����ڼĴ��� T8PnP ��ֵ���������ھ��_�� PRDBUF����

�M������������O�� T8PnM=0 �� T8PnPMS=1����ʹ�� T8PnE=1����ʼ���ڽY����ÿ�� T8Pn ��Ӌ��(sh��)ֵ�c���ھ��_�� PRDBUF ƥ����Ⱥ��ԄӸ������ھ��_����

6. 1. 7 PWMݔ��ģʽ

�� T8PnM=1 �� T8PnE=1 �r��T8Pn ������ PWM ģʽ��Ӌ��(sh��)�r�Դ��ϵ�y(t��ng)�r状����l Fosc/2����֧���A���l��������l�����O�ò�Ӱ� PWM ݔ�����ں�ռ�ձȣ�ֻӰ�ƥ���Д� T8PnTIF �Д���־λ�Įa(ch��n)����ԔҊ��T8Pn ����l�����ñ�����

�� PWM ģʽ�£�PWM ݔ���ɼĴ��� T8PnTRN λ���ơ�

�� T8PnTRN=1 �r��PWM ݔ��ʼ�K�� 0���Ҳ������� T8PnP �� T8PnR �Ĵ�����ֵ�����ھ��_�� PRDBUF �;��Ⱦ��_�Ĵ��� RESBUF��

�� T8PnTRN=0 �r��PWM ݔ�����β��܆��ӣ��� PWM ݔ����ʼ�� 1��ͬ�r�քe�� T8PnP�� T8PnR �Ĵ����ă�(n��i)�ݸ��������ھ��_�� PRDBUF �;��Ⱦ��_�Ĵ��� RESBUF�����_��ܛ�������x�������S�� T8Pn �����_ʼ�f��Ӌ��(sh��)���� T8Pn �c RESBUF ��ֵ��ȕr��PWMݔ����׃?y��u)?0�����^�m(x��)�f��Ӌ��(sh��)���� T8Pn ��Ӌ��(sh��)ֵ�c PRDBUF ��ȕr�� PWM ݔ���֏͞� 1��ͬ�r PRDBUF �� RESBUF �ٴηքe�d�� T8PnP �� T8PnR �Ĵ�����ֵ�����a(ch��n)�������Д� T8PnPIF �Д���־��ԓ�Д���־��Ҫܛ�����㡣ͬ�r T8Pn ���Ԅ����㲢�����_ʼӋ��(sh��)������l���� 1 Ӌ��(sh��)������һ�������� PWM ������ɣ��S���^�m(x��)ѭ�h(hu��n)�µ� PWM ���ڡ�������l����Ӌ��(sh��)ֵ�c����l�����l����ͬ�r����λ����l�����������r�Д���־T8PnTIF �� 1��ԓ�Д���־��Ҫܛ�����㡣

�� PWM ģʽ�£����Ⱦ��_�� RESBUF �����ھ��_�� PRDBUF �ĸ��£�

�� PWM ģʽ��ʼ���ڣ������܌� T8PnP �� T8PnR �Ĵ�����ֵ�����ھ��_�� PRDBUF ��

���Ⱦ��_�Ĵ��� RESBUF����M������������O�� T8PnM=1��T8PnPMS=1 �� T8PnE=1�����O�� PWM ݔ��ʹ�� T8PnTRN=0��

��ʼ���ڽY����ÿ�� T8Pn ��Ӌ��(sh��)ֵ�c���ھ��_�� PRDBUF ƥ����Ⱥ��ԄӸ������ھ��_���;��ȼĴ�����

ע 1�������Ⱦ��_�� RESBUF ��ֵ�� 0���t��ǰ PWM ���ڃ�(n��i) PWM ݔ��ʼ�K�� 0�������Ⱦ��_�Ĵ��� RESBUF ��ֵ��С�� PRDBUF���t��ǰ PWM ���ڃ�(n��i) PWM ݔ��ʼ�K�� 1��

ע 2�����xȡ T8PnTRN λ�Ġ�B(t��i)�r���x����λ��ֵ�錑���λֵ�ķ�߉����������λ���� 0 �r���x����ֵ�� 1������λ���� 1 �r���x����ֵ�� 0��

ע 3���� T8PnTRN=1���t PWM ݔ�� 0�������ھ��_�������£�Ҫô���ֳ�ʼֵ 0xFF��Ҫô�� T8PnTRN=0 �r�����һ�θ����^��ֵ����

6. 1. 8 PWMƽ�����ȔUչ

PWM �����ֱ��ʿ��_ 9 λ���Mһ������ PWM ݔ�����ȣ���ͨ�^�O�ÔUչ����λT8PxRE<1:0>��T8PxOC<5:4>���M�� PWM ƽ�����ȔUչ���ˑ���ģʽԭ���Dz��Ì��B�m(x��)ݔ�������}���M���g���ؼ� 1���� 1 �� LSB�����}�������� 1 �� Tosc �� [�A���l����(sh��)]��ҊPWM Ӌ�㹫ʽ���������F(xi��n) PWM ����ռ�ձȵ�ƽ��ֵ������

�Uչ����λ���O�� 0��1/4��2/4��3/4 �� 4 �����ȔUչֵ���ஔ�ڌ� PWM ƽ�����ȔUչ 2λ��

���磬���Uչ�����O�Þ� 2/4���� 4 �� PWM �}������ 2 ���}���Č������� 1 �� LSB�������� 1 �� LSB ���}������ֲ��� 4 ���}���У����D��ʾ�����O�}�����Ȟ� n���t 4 ���_�P���ڣ�PWM ���ڣ���ƽ���}���� n+1/2���Ķ��ڲ���ߕr��l�ʵ���r�£���Ч���F(xi��n)���^�߷ֱ��ʵ� PWM��

6. 1. 9 PWM ����ݔ���˿�

T8Pn ��֧��һ�����a�� PWM ݔ���˿ڣ�PWMn0 �� PWMn1��֧�ֿ��{(di��o)���^(q��)�r�g���ã����^(q��)�r�g���� T8PnPDT �Ĵ����O�á�

PWM ���^(q��)�ӕr�r�gӋ�㹫ʽ��T8PnPDT<7:0> x Tosc��

ͨ�^�O�� T8PnOC �Ĵ����е� T8PnPEN<1:0>�� T8PnNEN<1:0>���x�� T8Pn �� PWMn0�� PWMn1 �c I/O ���õ�ݔ�����_��

PWMn0 ��ݔ���O�Կ�ͨ�^�Ĵ��� ANS<7:6>��PWM20NS��PWM10NS���M���O�á�

ֵ��ע����ǣ���ʹ�� PWM ݔ��ǰ�����Ȍ��c PWM ���õ����� I/O �˿ڵĿ��ƼĴ���λPxT �O�Þ�ݔ����B(t��i)����t���o PWM ����ݔ����

6. 2 ģ/��(sh��)�D(zhu��n)�Q��ģ�K��ADC��

6. 2. 1 ����

ģ�M��(sh��)���D(zhu��n)�Q�����ڌ�ģ�M��̖�D(zhu��n)����һ�M���M�ƴ��a�M�ɵĔ�(sh��)����̖��ģ�M��̖��(j��ng)�ɶ�·

����ݔ���_ݔ�룬ͨ�^һ���ɘ�-�����·�B�����D(zhu��n)�Q����ݔ��ˡ�ԓоƬ֧�� 12-bit 6+2

ͨ���� A/D �D(zhu��n)�Q������(j��ng)�^ A/D �D(zhu��n)�Q���D(zhu��n)�Q�� 12-bit ���M�Ɣ�(sh��)��(j��)���� ADC ��(sh��)��(j��)�Ĵ���

ADCRH��ADCRL ��

ģ/��(sh��)�D(zhu��n)�Q������

- 12 λ ADC �ɘӾ���

- 6 ��ģ�Mݔ��+2 ���Դ늉��z�yͨ�����x

- 12 λ�D(zhu��n)�Q�Y����֧�ָ�λ���R���û��λ���R����

- ֧���ⲿ���(n��i)������늉����x��

- ֧���Դ늉��z�y���Դ�։��ȿ��x

- ֧�ֿ����� A/D �D(zhu��n)�Q�r�

- �r�Դ����ϵ�y(t��ng)�r� Fosc

��Ҫ���ܽM��

- ADC �D(zhu��n)�Qֵ�Ĵ�����ADCRL��ADCRH��

- ADC ���ƼĴ�����ADCCL��ADCCH��

- �˿�����x��Ĵ�����ANS��

- ADC �Ԅ��|�l(f��)�Ĵ�����ADCTR��

�Д�͕�ͣ

- ֧�� A/D �D(zhu��n)�Q�ДࣨADIE/ADIF��

6. 2. 3 ADC����

ADC �·ʹ��ǰ�������(j��)��Ҫ�����ׂ������M�����_�����ã��ſɵõ���Ҫ�����_�D(zhu��n)�Q�Y����

�r��x��

ADC �·����Ҫ�ĕr��� 7 �M���x��F(xi��n)osc~Fosc/64����ͨ�^ ADCCH �Ĵ����x������Ҫ�ĕr犡�

����늉��x��

ADC �·�քeʹ��һ��������늉���һ��ؓ����늉��������ⲿ����늉�ݔ���_�քe��VREFP �� VREFN������ԓ�ɂ��ⲿݔ���_�քe�c PB1/AIN4��PB0/AIN3 ���ã���ʹ���@�ɂ��ⲿ����늉�ݔ��r������ͨ�^ ANS �Ĵ������_�O�Ï��ö˿ڵ���͡�������늉���ͨ�^ ADVREFS <2:0>λ�x�� VDD��4V��3V��2.1V ������ VREFP ���ö˿ڣ�ؓ����늉��������x�� VSS ������ VREFN ���ö˿ڡ������˅���늉��x�� 2.1V �r�����ȸ���(j��) VDD 늉�ͨ�^ AD2VCALS λ��ADCTR<0>�����_�O�� A/D 2.1V ����늉��{(di��o)У��Ϣ���ɘӕr�g�x��

��оƬ֧�� ADC �·�IJɘӕr�g���x����ͨ�^ ADCCH �Ĵ����е� ADST <3:0>λ�x���

�s 1~15 �� Tadclk �� 15 �N�x헡�

���ö˿�����x��

��оƬ�� ADC �·������ģ�Mݔ��ͨ�� AINn������늉��ⲿݔ���_���� PA/PB �˿ڏ��ã���ʹ�� ADC �·�D(zhu��n)�Qǰ����Ȍ���ʹ�õĹ��_ͨ�^ ANS �Ĵ����O�Þ�ģ�M��͡�

ģ�M��̖ݔ��ͨ���x��

ADC �·ʹ��ǰ�������x�� A/D ģ�Mͨ������оƬ ADC �·֧�� 6 ���ⲿͨ���� 2 ���Դ늉��z�yͨ�����x���ⲿͨ���քe�� AIN0~AIN5���ɂ��Դ늉��z�yͨ���քe�� VDD/4�� VDD/8��A/D ģ�Mͨ���x���Ă�ͨ����ͨ�^ ADCCL �Ĵ����е� ADCHS <2:0>λ�x���R��ʽ�x��

��оƬ ADC �·�D(zhu��n)�Q�ĽY��֧�փɷN���R��ʽ����λ���R��λ���R����ͨ�^ ADCCH�Ĵ����е� ADFM λ�M���x��

ADC ģ�K�D(zhu��n)�Q�|�l(f��)��ʽ�x��

��оƬ ADC ģ�K֧�փɷN A/D �D(zhu��n)�Q�|�l(f��)��ʽ��ܛ���|�l(f��)�� PWM �Ԅ��|�l(f��)��

��ADCģ�K�D(zhu��n)�Qʹ��λADEN��ADCCL<0>��ʹ�ܺ�ͨ�^ܛ����ADC�D(zhu��n)�Q��B(t��i)λADTRG��ADCCL<1>���á�1����ADC ģ�K�_ʼ�M���D(zhu��n)�Q���˞�ܛ���|�l(f��) A/D �D(zhu��n)�Q���� ADC ģ�K�D(zhu��n)�Qʹ��λ ADEN��ADCCL<0>���� PWM �Ԅ��|�l(f��) ADC ʹ��λ TRIGEN��ADCTR<4>����ʹ�ܺ��� PWM ߅���|�l(f��)��̖��ʹ ADTRG λ�Ԅ��Þ顰1����ADC ģ�K�_ʼ�M���D(zhu��n)�Q���˷N�� PWM �Ԅ��|�l(f��)��

PWM �Ԅ��|�l(f��)Դ���x����� PWMn1 ��̖��ͨ�^�Ԅ��|�l(f��)Դ�x��λ TRIGS��ADCTR<6>���M���x��PWM �Ԅ��|�l(f��)߅�ؿ�ͨ�^ TRIGPEG λ��ADCTR<5>���x�� PWM �����ػ��½����|�l(f��)��

ֵ��ע����ǣ���ʹ�� PWM �Ԅ��|�l(f��) ADC �r�����h�Ȳ�ԃ ADTRG λ�Į�ǰ��B(t��i)������ԃ�� ADTRG λ�顰1���r���˶Εr�g�� PWM ߅���Ԅ��|�l(f��)��̖���������ԣ�ֱ�� ADTRG

λ�Ġ�B(t��i)�֏͞顰0����ϵ�y(t��ng)�ٴΙz�y�� PWM ߅���Ԅ��|�l(f��)��̖���ŕ�푑� PWM �Ԅ��|�l(f��) ADC ģ�K�M���D(zhu��n)�Q��

6. 2. 4 ADC�D(zhu��n)�Q���E

����������F(xi��n) ADC �D(zhu��n)�Q�^�̵ĸ������E��

Step 1���x�� ADC �D(zhu��n)�Q�r犣�ͨ�^ ADCCH �Ĵ����е� ADCS <2:0>�x�� ADC �D(zhu��n)�Q�r犡�

Step 2���x����ؓ����늉���ͨ�^ ADCCL �Ĵ����е� ADVREFNS λ�M���x��

Step 3��ADC �ɘӕr�g�x��ͨ�^ ADCCH �Ĵ����е� A/D �ɘӕr�g�x��λ ADST <3:0>�O����

Step 4���O�Ï��ö˿��O��ģ�M��ͣ����x����Щ���_���� ADC �D(zhu��n)�Qݔ����_���ɶ˿�����x��Ĵ��� ANS �����x��

Step 5���x��ģ�M��̖ݔ��ͨ�� AINx��ͨ�^ ADCCL �Ĵ����е� ADCHS <2:0>�x�� ADCģ�Mͨ����

Step 6���O���D(zhu��n)�Q�Y�����R��ʽ��ͨ�^ ADCCH �Ĵ����е� ADFM λ�x���λ���R����߀�ǵ�λ���R���á�

Step 7�����Ҫʹ���Д࣬�t�Д���ƼĴ�����Ҫ���_���O�ã��Դ_�� A/D �Д�ܱ����_������Д�ģʽ�r���茢ȫ���Д�ʹ��λ GIE ��λ�顰1���� ADC �Д�ʹ��λ��λ�顰1����

Step 8��ʹ�� ADC �·���� ADCCL �Ĵ����е� ADC ʹ��λ ADEN �O�Þ顰1����

Step 9���x�� ADC ģ�K�D(zhu��n)�Q�|�l(f��)��ʽ��ܛ���|�l(f��)߀�� PWM �Ԅ��|�l(f��)�����x��ܛ���|�l(f��)���� ADCCL �Ĵ����е� ADC �D(zhu��n)�Q����λ ADTRG λ�O�Þ顰1�����_ʼ�M�� ADC �D(zhu��n)�Q�����x�� PWM �Ԅ��|�l(f��)�������O�� TRIGS λ�x���Ԅ��|�l(f��)Դ�� TRIGPEG λ�x�� PWM �Ԅ��|�l(f��)߅�أ��O�� PWM �Ԅ��|�l(f��) ADC ʹ��λ TRIGEN �顰1������ PWM �Ԅ��|�l(f��) ADCģ�K�D(zhu��n)�Q�O����ɺ��Ԅ�߅���|�l(f��)��̖���Ԅӌ� ADTRG λ�Þ顰1�����_ʼ�M�� ADC�D(zhu��n)�Q��

Step 10��݆ԃ ADCCL �Ĵ����е��D(zhu��n)�Q��B(t��i)λ ADTRG λ���_���˴� A/D �D(zhu��n)�Q�Ƿ���ɡ�

Step 11���xȡ ADCRH �� ADCRL �Ĵ����е��D(zhu��n)�Q�Y����

6. 3 ��늉��z�yģ�K��LVD��

6. 3. 1 ����

оƬ��(n��i)��һ�M��늉��z�yģ�K��֧�ֵ�늉��z�y���ܣ��� LVD��ԓ����ʹ�����ڱO(ji��n)�y�Դ늉� VDD���ڹ���Դ����(w��n)������r�£����ⲿ�Դ�����_�� EMS �yԇ�l���£���ʹ�Դ������ʎ����Ŀ��늉�δ��(w��n)���r�����ܾ͕����ڹ���늉���������z�y��늉�����һ��ֵ���ṩһ��������̖����늉��z�yҲ�ɮa(ch��n)���Д���̖��

6. 3. 2 LVD����

LVD ���ܵĽ�ֹʹ���� LVDC �Ĵ����е� LVDEN ����λ�O�á��� LVDEN λ���㣬LVD ���ܽ�ֹ���� LVDEN λ�øߣ�LVD ����ʹ�ܡ�LVD ģ�K���Դ늉� VDD �c�A��늉��M�б��^�����^�Y��ͨ�^ LVDC �Ĵ����� LVDLS λ�M�в�ԃ���A��늉����ֵ�� LVDC �Ĵ����е� LVDV<1:0>���ã��A��늉������� 2.1V~3.6V����Ŀ��늉������A��늉�ֵ�r��LVDLSλ���Þ�ߣ������z�y����늉��a(ch��n)�����a(ch��n)�� LVD �Д���־���� LVD �Д�ʹ���_���r�a(ch��n)�� LVD�Д�Ո��

�� 7 �� �Д�̎��

7. 1 ����

�Д���оƬһ����Ҫ���ܡ����܌�оƬ��˯��ģʽ�І��ѣ�Ҳ����ʹϵ�y(t��ng)�������\���^����푑�ͻ�l(f��)�¼�����ֹ�����殔ǰ�\�г������Ϣ�����D(zhu��n)��Ո���Д����ڵ�ַ����(zh��)�����������Д���ճ���̎��ͻ�l(f��)�¼�����оƬ�H֧��Ĭ�J�Д�ģʽ������֧�� 12 ���Д�Դ��1��ܛ���Д�� 11 ��Ӳ���Дࡣ

7. 3 ��F(xi��n)�����o

�Д�F(xi��n)�����o���Д������һ������Ҫ�ĽM�ɲ��֡�ָ��ϵ�y(t��ng)���� PUSH���������� POP��������ָ������Á팍�F(xi��n)�Д�Ĕ�(sh��)��(j��)���档���Ա���Ĕ�(sh��)��(j��)�������ۼ��� A �Ĵ����������B(t��i)�ּĴ��� PSW��IAA �Ĵ����� PCRH �Ĵ�����������(sh��)��(j��)�Ĵ����ı��o���������ָ��F(xi��n)�������B�m(x��)�M�� 2 �� PUSH���� 3 �� PUSH��ʹ�õ�һ�� PUSH �Ĕ�(sh��)��(j��)�Gʧ��ͬ�ӣ����^ 2 �ε��B�m(x��) POP���� 3 �� POP �֏͵Ĕ�(sh��)��(j��)�����A�ڡ�

7. 4 �����

ÿ��Ӳ���Д�Դ���и��Ե��Д�ʹ�ܺ��Д���־λ����˳�ʼ��������Ӳ���Д��r����Ҫ������Д���־λ����ʹ�ܮ�ǰ�Дࡣ��ʹ��ǰ��������Д���־���t�п��ܰl(f��)���`�M�Д����r������ÿ���Д�֧���Д�ʹ���⣬��оƬ߀�ṩ��һ��ȫ���Дࡣ����ڳ�ʼ��������Ҫ���Д��Ոʹ��ȫ���Дࡣ

���Д��¼��l���a(ch��n)�������P�Д���־�����Þ顰1�����Д���־�a(ch��n)�������Ҫ���D(zhu��n)����������

��ַ��(zh��)����M�����l����

1. �������Д�ʹ��λ�顰1���r���^�m(x��)�Д�ڶ����l���Ƿ�M�㣻�������Д�ʹ��λ�顰0������ʹ�Д���־�顰1�����Д�Ҳ�����l(f��)��������Ҳ�������D(zhu��n)���Д���յ�ַ��(zh��)�С�

2. ��ȫ���Д�ʹ��λ GIE �顰0���������������Д�Ո��ȫ���Д�ʹ��λ GIE �顰1��������?q��)������Д���յ�ַ�?zh��)�С�

��_�����Ĵ��� GIE �� GIEL ��ܛ���������ɹ����谴���²��E�M�У�

1. ��Ĭ�J�Д�ģʽ�������Д�ģʽ�£��� GIE λ��ܛ���� 0 �����������P�]�������O�Д�ʹ�ܣ��ٌ� GIE λ�� 0������ GIE λ�� 0 ������ԃ GIE λ�Ƿ�� 0������ 0�t�^�m(x��)��(zh��)���� 0 ������ֱ���ɹ���ֹ��

�� GIE λ��ܛ���� 1 �������o����Ҫ�����]�ȴ��_��������O�Д�ʹ�ܣ��ٌ� GIEλ�� 1��

2. �������Д�ģʽ�£��� GIEL λ��ܛ���� 0 �����������P�]�������O�Д�ʹ�ܣ��ٌ�

GIEL λ�� 0������ GIEL λ�� 0 ������ԃ GIEL λ�Ƿ�� 0������ 0 �t�^�m(x��)��(zh��)���� 0 ������ֱ���ɹ���ֹ��

�� GIEL λ��ܛ���� 1 ���������c GIE λͬ�r�� 1�����Ȍ� GIEL λ�� 1���ٌ� GIEλ�� 1��

7. 4. 1 �ⲿ�Д�

�� PINTn ���ö˿ڱ����Þ锵(sh��)��ݔ��˿ڣ���ݔ����̖׃���M���|�l(f��)�l���r�����a(ch��n)��PINTn �ⲿ�˿��Д࣬�������Д���־ PIFn ���á�1������ȫ���Д����λ GIE ���ⲿ�˿��Д����λ PIEn �����Þ顰1�����t�� CPU �l(f��)�� PINTn �ⲿ�˿��Д�Ո���Д��l�����S��ϵ�y(t��ng)���M���Д���ճ�����ڵ�ַ���M���Д����̎����ֵ��ע����ǣ������Д���־λ PIFn ���Д�ʹ��λ PIEn ����ͨ�^ܛ�������INTC1 �Ĵ����е� PEGn λ���������|�l(f��)�l�����ɷքe���Þ��������|�l(f��)���½����|�l(f��)��

7. 4. 2 �ⲿ���I�Д�

�� KINn ���ö˿ڱ����Þ锵(sh��)��ݔ��˿ڣ�δ�����εİ��I���κ�һ���˿�ݔ����̖�l(f��)���ƽ׃�������Д���־λ KIF �Þ顰1�������ⲿ���I�Д����λ KIE �顰1������ȫ���Д����λ GIE λʹ�ܺt�� CPU �l(f��)���ⲿ���I�Д�Ո���ⲿ���I�Д��l�����S�r��ϵ�y(t��ng)���M���Д���ճ�����ڵ�ַ���M���Д����̎����ʹ���ⲿ���I�Д��r������������Ŀ��ƼĴ���������ʹ���ⲿ���I�Д�˿ڵă�(n��i)����������衣

�ڰ��I�Д�ʹ�ܣ�KMSKn=1��KIE=1��ǰ���Ȍ��˿ڼĴ����M���x���ߌ��IJ���������Д���־λ�������`�a(ch��n)���Дࡣ

���ԓ�Д���־λ KIF �IJ������E��

1�����˿ڼĴ����M���x���ߌ��������Y���˿��ƽ�c�i����ֵ�IJ�ƥ��l����

2��ܛ������Д���־λ KIF��

�Д�ʹ��λ KIE Ҳ��Ҫͨ�^ܛ���M�������

7. 4. 3 T8Pn(T8P1/T8P2)���r��

8 λ PWM �r�����r�� T8Pn ̎�ڶ��r��ģʽ�� PWM ģʽ�r����Ӌ��(sh��)�r��M���f��Ӌ��(sh��)���� T8Pn ����l����Ӌ��(sh��)ֵ�c����l�����l����ͬ�r�����Д���־ T8PnTIF λ�á�1������

T8Pn ���r�Д�ʹ��λ T8PnTIE �Þ顰1������ȫ���Д����λ GIE ʹ�ܺt�� CPU �l(f��)��

T8Pn ���r�Д�Ո�� T8Pn ���r�Д��l�����S�r��ϵ�y(t��ng)���M���Д���ճ�����ڵ�ַ���M���Д����̎����ֵ��ע����ǣ�T8Pn���r�Д���־λ T8PnTIF ���Д�ʹ��λ T8PnTIE����ͨ�^ܛ�������

7. 4. 4 T8Pn(T8P1/T8P2)������

8 λ PWM �r�����r�� T8Pn ̎�ڶ��r��ģʽ�� PWM ģʽ�r�������Ԯa(ch��n)�������Дࡣ��T8Pn Ӌ��(sh��)���c T8PnP �Ĵ�����ֵ��ȕr��PWM ģʽ�r��T8Pn �����_ʼ�f��Ӌ��(sh��)�������a(ch��n)�� T8Pn �����Д࣬�Д���־ T8PnPIF ���á�1���� ����Д�ʹ��λ T8PnPIE �Þ顰1������ȫ���Д����λ GIE ʹ�ܺt�� CPU �l(f��)�� T8Pn �����Д�Ո�� T8Pn �����Д�

�l�����S�r��ϵ�y(t��ng)���M���Д���ճ�����ڵ�ַ���M���Д����̎����ֵ��ע����ǣ�T8Pn�����Д���־λ T8PnPIF ���Д�ʹ��λ T8PnPIE ����ͨ�^ܛ�������

7. 4. 5 ADC�Д�

ADC �Д��� ADC �D(zhu��n)�Q�������ƣ��� ADC �D(zhu��n)�Q��ɕr�����a(ch��n)�� ADC �Д࣬ADC �Д���־λ ADIF ���á�1������ ADC �Д����λ ADIE �Þ顰1������ȫ���Д����λ GIE ʹ�ܺt�� CPU �l(f��)�� ADC �Д�Ո�� ADC �Д��l�����S�r��ϵ�y(t��ng)���M���Д���ճ�����ڵ�ַ���M���Д����̎����ֵ��ע����ǣ�ADC �Д���־λ ADIF ���Д�ʹ��λ ADIE ����ͨ�^ܛ�������

7. 4. 6 LVD�Д�

�� VDD 늉�С�� LVDC �Ĵ����O���ֵ늉��r����늉��a(ch��n)����LVDLS �����ػ��½����|�l(f��)���Д���־ LVDIF λ���á�1��������Д�ʹ��λ LVDIE �Þ顰1������ȫ���Д����λGIE ʹ�ܺt�� CPU �l(f��)�� LVD �Д�Ո�� LVD �Д��l�����S�r��ϵ�y(t��ng)���M���Д���ճ�����ڵ�ַ���M���Д����̎����ֵ��ע����ǣ�LVD �Д���־λ LVDIF ���Д�ʹ��λ LVDIE ����ͨ�^ܛ�������

7. 4. 7 �Д����ע�����

�Ñ���ʹ���Д�ǰ��������������Д���־�������Д���`�|�l(f��)��

��ֻ�x���Д���־����Ӳ��������⣬������Д���־���ͨ�^ܛ�������

MCU оƬʹ��ע�����

�P��оƬ����/���

MCU оƬ���Ъ����Դ���_���� MCU оƬ�����ڶ��Դ���ϵ�y(t��ng)�r�����Ȍ� MCU оƬ��늣��ٌ�ϵ�y(t��ng)����������늣���֮����늕r���Ȍ�ϵ�y(t��ng)����������늣��ٌ� MCU оƬ��늡�����������෴�t���܌���оƬ��(n��i)��Ԫ���^�����^�����Ķ�����оƬ���ϻ�Ԫ���˻������w�Ʌ���оƬ�Ĕ�(sh��)��(j��)�փ��f����

�P��оƬ�ď�λ

MCU оƬ���Ѓ�(n��i)����늏�λ�����ڲ�ͬ�Ŀ�����/��늻�������/���ϵ�y(t��ng)����(n��i)����늏�λ�·����ʧЧ��

���h�Ñ�ʹ���ⲿ��λ����늏�λ�����T����λ�ȣ��_����λ�·������������ϵ�y(t��ng)�OӋ�r����ʹ���ⲿ��λ�·��

���h�������O��λ�·��RC ��λ�·������ʹ���ⲿ��λ�·�����h���Ï�λ���_����赽�Դ�����ȡ��Ҫ���Դ����̎���·���������o�·�����w�Ʌ���оƬ�Ĕ�(sh��)��(j��)�փ��f����

�P��оƬ�ĕr�

MCU оƬ���Ѓ�(n��i)�����ⲿ�r�Դ����(n��i)���r�Դ���S���ضȡ�늉�׃����ƫ�ƣ����ܕ�Ӱ푕r�Դ���ȣ��ⲿ�r�Դ�����մɡ����w��ʎ���·�r�����hʹ�������ӕr��ʹ�� RC ��ʎ�·�r���迼�]��ݡ����ƥ�䣻�����ⲿ��Դ�����r�ݔ��r���迼�]ݔ���/���ƽ늉������w�Ʌ���оƬ�Ĕ�(sh��)��(j��)�փ��f����

�P��оƬ�ij�ʼ��

MCU оƬ���и��N��(n��i)�����ⲿ��λ�����ڲ�ͬ�đ���ϵ�y(t��ng)���б�Ҫ��оƬ�Ĵ�������(n��i)�桢����ģ�K���M�г�ʼ���������� I/O ���_���ù����M�г�ʼ������������оƬ����Ժ�I/O ���_��B(t��i)�IJ��_����r�l(f��)����

�P��оƬ�Ĺ��_

MCU оƬ���Ќ�������ݔ����_�ƽ�����h�Ñ�ݔ����ƽ���� VIHMIN ֮�ϣ����ƽ���� VILMAX ֮�¡�����ݔ��늉����� VIHMIN �� VILMAX ֮�g�����Ⲩ�����M��оƬ������δʹ�õ�ݔ��/ݔ�����_�����h�O�Þ�ݔ���B(t��i)����ͨ�^�������Դ��أ����O�Þ�ݔ����B(t��i)��ݔ���̶��ƽ����δʹ�õĹ��_̎������ϵ�y(t��ng)���������w��ѭ����ϵ�y(t��ng)�����PҎ(gu��)�����f����

�P��оƬ�� ESD ���o��ʩ

�|ܛ�d��MCUоƬ���НM�㹤�I(y��)��ESD�˜ʱ��o�·�����h�Ñ�����(j��)оƬ�惦/���õĭh(hu��n)����ȡ�m���o늷��o��ʩ����ע�⑪�íh(hu��n)���ĝ�ȣ����h����ʹ�����a(ch��n)���o늵Ľ^���w����ź��\ݔ���ڿ��o����������o����δ���?q��)�늲��������У����������_�ڃ�(n��i)�����Мyԇ�͜y�����߱�횱��C�ӵأ������ߑ�ԓ����o���������h(hu��n)���ף���������ֱ�ӽ��|оƬ�ȡ�

�P��оƬ�� EFT ���o��ʩ

MCU оƬ���НM�㹤�I(y��)�� EFT �˜ʵı��o�·���� MCU оƬ������ PCB ϵ�y(t��ng)�r����Ҫ���� PCB ���P�OӋҪ�����Դ�����߾���������(sh��)��/ģ�M�Դ���x����/���c�ӵصȵȣ�����λ���_���o�·���Դ�͵�֮�g��ȥ����ݡ��ߵ��l�·�Ϊ��քe̎���Լ���/���Ӱ��x��ȡ�

�P��оƬ���_�l(f��)�h(hu��n)��

MCU оƬ����������ܛ/Ӳ���_�l(f��)�h(hu��n)��������֪�R�a(ch��n)�ౣ�o���x���Ϻ��|ܛ�d���������˾����ָ���ĵ�������˾�ąR���������g������������Ӳ���������_�l(f��)�h(hu��n)���������ѭ�cоƬ���P��Ҏ(gu��)�����f����

�����g���汾��iDesigner V4.12.145 HRCC V1.2.0.89����(y��u)���ȼ�O0����

1.�h��HR7P153 timer���̶����else�Z�䡣

2.���̳�ʼ��������RAM����(sh��)��

ȫ���Y��51hei���d��ַ��

Ҏ(gu��)�����

HR7P153.pdf

(1.22 MB, ���d��(sh��): 44)

HR7P153.pdf

(1.22 MB, ���d��(sh��): 44)

2018-8-27 17:21 �ς�

�c���ļ������d����

����Դ�a��

HR7P153 V1.5.zip

(41.42 KB, ���d��(sh��): 62)

HR7P153 V1.5.zip

(41.42 KB, ���d��(sh��): 62)

2018-8-27 17:21 �ς�

�c���ļ������d����

|

�u��

-

�鿴ȫ���u��

|

����TQQ:125739409;���g����QQȺ281945664

����TQQ:125739409;���g����QQȺ281945664