《EDA技術及應用》實訓報告

實訓題目:交通燈控制電路的設計

1 系統設計1.1 設計要求

1.1.1 設計任務

設計并制作一個交通燈電路,使它能符合實際交通道路控制的要求。

1.1.2 性能指標要求 ① 用EDA實訓儀上的4只八段數碼管分別顯示道路東西和南北通行和禁止的倒計時時間。

② 能設置道路東西和南北兩側通行和禁止的倒計時時間,最大設置時間為99秒,最小設置時間為1秒。

③ 交通燈用紅、綠、黃三種發光二極管(LED)顯示控制的結果。

④ 紅、綠、黃燈顯示的次序應符合實際交通道路控制的要求。

1.2 設計思路及設計框圖

1.2.1設計思路

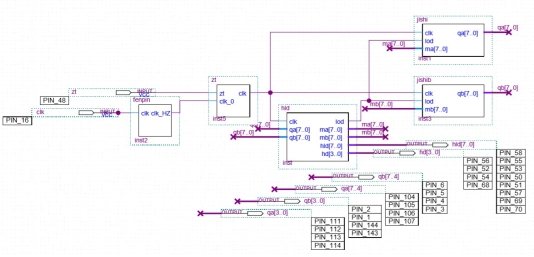

此方案需要設計一個分頻器和兩個計時模塊一個紅綠燈模塊,分頻器模塊用于將20MHz轉換為1Hz的時鐘,兩個計時器分別進行東西紅綠燈的倒計時。燈的模塊只需要設計一個模塊,將黃燈和紅綠燈分開,定義一個8位的reg型變量來控制紅綠兩色LED燈和一個4位reg型變量黃色LED燈,黃燈實現倒計時外,加上了閃爍的功能。

此外,為此方案加入了一個暫停模塊。

1.2.2總體設計框圖

fenpin:分頻模塊;

zt:暫停模塊;

jishi,jishib:倒計時模塊;

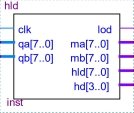

hld:紅綠燈模塊;

2 各個模塊程序的設計

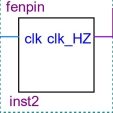

即fenpin 模塊。這個模塊是把EDA實訓儀主板提供的20MHZ的主頻經兩千萬分頻后,得到電路所需的1秒脈沖。其中clk是時鐘輸入端,clk_HZ是輸出端。

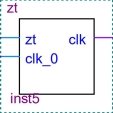

“zt”輸入端高電平時使計數暫停(clk_0與clk斷開),低電平時使計數繼續(clk_0與clk連接)。

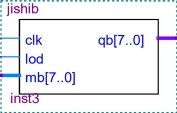

以“jihshi”模塊為例:clk是經過分頻器輸出的1HZ時鐘信號;lod是控制交通燈模式轉換的標志位;ma[7..0]輸入的是從qa[7..0]拿到的數值;qa[7..0]是輸出端既輸出給紅綠燈模塊和黃燈模塊,又將數值顯示在數碼管上。

clk是分頻器輸出的時鐘信號; qa,qb是計時器輸出的時間信號,用于判斷并改變lod的狀態;ma,mb是從預先定義紅黃綠LED燈的時間中拿到的數值,再輸出給計時模塊;hld是顯示輸出端,接LED的紅綠兩種燈;hd 是顯示輸出端,接LED的黃燈。其中lod是控制交通燈模式轉換的標志位,qm表示紅綠燈的四種狀態。 flag是控制黃燈的三種狀態。

在設計前根據要求做一個交通燈的這個設計流程圖,注意紅綠黃三種燈的變換。對各個小模塊的程序進行編寫和調試,各個小模塊程序調試完畢之后,接著就要從整個交通燈系統的一些細節進行修改。

東西和南北方向分別亮紅燈和綠燈,同時兩組的數碼管從開始設的26秒和30秒開始倒計時,等倒計時完東西組燈先從綠燈轉到黃燈,南北組從紅燈轉綠燈,但是在這模塊的時候設置的時間沒設好,黃燈亮了以后綠燈還沒滅,經過審查問題最終被解決了

對程序編譯成功后下載到EDA試驗箱,LED開始亮,開始自動倒計時,紅黃綠燈跳變。

4 功能測試4.1 測試儀器與設備

電腦 :一臺

EDA實驗箱 :一臺

4.2 性能指標測試

1.東西南北的紅綠燈可以通過倒計時來禁止和發亮。

2.實現在1秒到99秒內可調。

3.能在數碼管上分別顯示兩個方向的交通燈倒計時,。

4.紅黃綠燈的變化基本符合實際交通燈。

5方向紅燈倒計時30s,綠燈26s,倒計時至0s,黃燈亮倒計時3,紅綠燈轉換黃燈閃爍。

4.3 誤差分析

本題目沒有誤差分析。

5 實訓心得體會從一開始完全沒有頭緒到畫出設計流程圖,在接下來熟悉Verilog HDL,下載Quartus9.0并熟練操作。

通過本次實訓,使我對EDA這門課有了更深的了解,課堂上所學到的知識要融會貫通,要自己親手去操作、學習,而且盡可能多的去拓展知識,去揣摩我們學到的東西。遇到難題別慌張,確定預想結果及方案,分模塊解決,問題就會變得簡單。另外一個模塊做好最好先編譯一下,成功后再做接下來的。

通過這次EDA實訓,使我對EDA更加的充滿興趣,同時對QuartusⅡ這個軟件有了進一步的了解,我學會了如何設計一個交通燈控制電路并且成功驗收。在進行實訓的的過程中,不僅提高了我的編程能力,同時還讓我對交通燈控制系統也進一步認識并加深了學習。當然實訓當中,我遇到許多問題,通過上網查找資料,詢問老師同學后使問題得到了解決。在此,非常感謝老師和同學的幫助。我認真的學習了每一條程序的作用,在驗收的時候也能基本回答出老師問的每一個問題。我深刻的明白了知識在于一點一點的積累,這一次的實訓涉及了方方面面的知識,有分頻器,有減法計數器等等模塊的設計,可以說這是對我們能力的一次大檢驗。

所以,這讓我懂得了很多知識都是要平時積累的,知識積累得多了那我們學習的時候就會有更多的依據,會有更多新的想法。所以今后一定要積累更多的知識,為以后對各個科目的深入學習做鋪墊。同時也要懂得把學到的知識運用到實際當中去。

6 參考文獻[1] 謝自美.電子線路設計·實驗·測試(第二版).武漢:華中科技大學出版社,2000.

[2] 江國強.EDA技術與應用(第五版).北京:電子工業出版社,2017.

[3] 潘松,黃繼業,潘明.EDA技術實用教程——VerilogHDL版(第五版).北京:科學出版社,2013.

[4] 閻石.數字電子技術基礎(第五版).北京:高等教育出版社,2006.

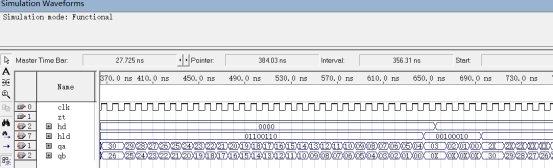

附錄1:仿真波形圖(部分模塊)

①

總模塊仿真(需要去掉分頻器):

②暫停模塊:

③計時模塊:

附錄2:程序清單