fpga播放一首歌

1 實驗目的

(1)理解并掌握脈寬調制(PWM )技術的控制方法及基本工作原理。

(2)學習并掌握脈寬調制(PWM )驅動蜂鳴器的實現方法。

2 實驗原理

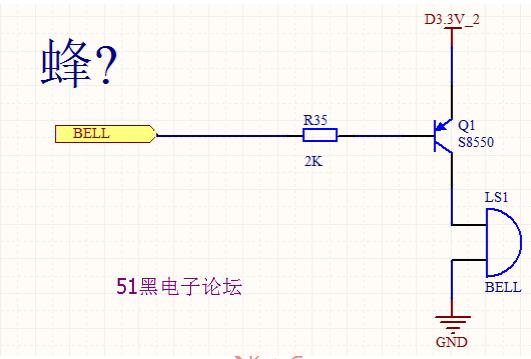

2.1 基本概念

脈沖寬度調制(PWM)是一種對模擬信號電平進行數字編碼的方法。通過高分辨率計數器的使用,方波的占空比被調制用來對一個具體模擬信號的電平進行編碼。PWM 信號仍然是數字的,因為在給定的任何時刻,滿幅值的直流供電要么完全有(ON),要么完全無(OFF)。電壓或電流源是以一種通(ON)或斷(OFF)的重復脈沖序列被加到模擬負載上去的。通的時候即是直流供電被加到負載上的時候,斷的時候即是供電被斷開的時候。只要帶寬足夠,任何模擬值都可以使用PWM進行編碼。 有源蜂鳴器和無源蜂鳴器的差別: 這里的“源”不是指電源。而是指震蕩源。也就是說,有源蜂鳴器內部帶震蕩源,所以只要一通電就會叫。而無源內部不帶震蕩源,所以如果用直流信號無法令其鳴叫。必須用 2K~5K 的方波去驅動它。 有源蜂鳴器往往比無源的貴,就是因為里面多個震蕩電路。 無源蜂鳴器的優點是:1。便宜,2。聲音頻率可控,可以做出“多來米發索拉西(1234567)”的效果。3。在一些特例中,可以和 LED 復用一個控制口 有源蜂鳴器的優點是:程序控制方便 。

開發板上的蜂鳴器是有源蜂鳴器。FPGA 輸出低電平,即可讓蜂鳴

器鳴響。

Quartus 工程 qsf 文件管腳約束命令,把以下命令拷貝到新建 quartus

工程的 qsf 文件即可完成管腳約束(注意信號名必須相同) :

set_location_assignment PIN_23 -to i_50m_clk

set_location_assignment PIN_28 -to i_rst_n

set_location_assignment PIN_187 -to o_pwm

3 實驗步驟

3.1 綜合

(1)運行綜合工具。

(2)打開項目工程,項目工程存放于以軟件開發工具命名的文件夾

中。

(3)編譯運行或直接點擊下載,下載 FPGA 軟件到目標板。

(4)查看軟件運行效果

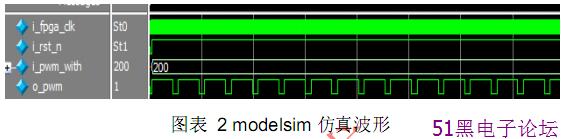

3.2 仿真

請參考視頻講解。

主要命令:

切換仿真路徑 cd { 仿真庫路徑 } ,如: cd

{F:\Verilog_demo\M01_buzzer_pwm\sim};

run 100us:仿真運行時間長度 100us ;

do wave.do:運行波形文件;

vlog ../src/*.v:編譯 scr路徑下的所有 v文件

vsim:開始仿真命令

quit –sim:退出仿真

4 實驗結果

4.1 結果演示

4.1.1 MODELSIM 仿真演示

4.1.2 M ATLAB 數據分析

略。

4.1.3 開發板演示

略。

4.2 特別說明

PWM 的一個優點是從處理器到被控系統信號都是數字形式的,無需進行數模轉換。讓信號保持為數字形式可將噪聲影響降到最小。噪聲只有在強到足以將邏輯1改變為邏輯0或將邏輯0改變為邏輯1時,也才能對數字信號產生影響。

對噪聲抵抗能力的增強是PWM相對于模擬控制的另外一個優點,而且這也是在某些時候將 PWM 用于通信的主要原因。從模擬信號轉向PWM 可以極大地延長通信距離。在接收端,通過適當的 RC 或LC網絡可以濾除調制高頻方波并將信號還原為模擬形式。

PWM既經濟、節約空間、抗噪性能強,是一種值得廣大工程師在許多設計應用中使用的有效技術。

源程序如下:

- //==========================================================================

- //Filename :PWM_gen.v

- //modulename:PWM_gen

- //Author :a fei

- //Date :2012-5-16

- //Function :PWM產生器,輸出的pwm驅動蜂鳴器

- //Uesedfor :

- //Taobao :

- //E-mail :2352517093@qq.com

- //==========================================================================

- module PWM_gen(

-

- i_fpga_clk ,

- i_rst_n ,

-

- i_pwm_with ,

-

- o_pwm

-

- );

- input i_fpga_clk ;//50MHz

- input i_rst_n ;

-

- input [19:0] i_pwm_with ;//改變數值可控制PWM的高電平寬度

- output reg o_pwm ;

-

-

- //=======================================

- //分頻計數器

- //=======================================

- reg[19:0] pwm_cnt ;

- always @ (posedge i_fpga_clk or negedge i_rst_n)//時鐘沿加1

- if(!i_rst_n)

- pwm_cnt <= 20'b0 ;

- else if( pwm_cnt==20'hfffff)

- pwm_cnt <= 20'b0 ;

- else

- pwm_cnt <= pwm_cnt+1'b1 ;

-

- always @ (posedge i_fpga_clk or negedge i_rst_n)

- if(!i_rst_n)

- o_pwm <= 1'b0 ;

- else if(pwm_cnt<=i_pwm_with)

- o_pwm <= 1'b1 ;

- else

- o_pwm <= 1'b0 ;

-

-

- endmodule

所有資料51hei提供下載(包含完整的設計報告):

M01_buzzer_pwm.zip

(2.38 MB, 下載次數: 97)

M01_buzzer_pwm.zip

(2.38 MB, 下載次數: 97)

2018-4-17 16:11 上傳

點擊文件名下載附件

|