|

ֱ��늙C(j��)�C�Ϝy��ϵ�y(t��ng)���O(sh��)Ӌ - ֱ��늙C(j��)�(q��)�ӿ����·�Ĺ���

����PWM���Ʒ�ʽ��ֱ��늙C(j��)�M(j��n)���ٶȿ��ơ����D(zhu��n)����Ŀ��ƺ�׃�ٿ��ơ� - �O(sh��)ӋҪ��

- Ԕ��(x��)�f��ϵ�y(t��ng)����ԭ���c�O(sh��)Ӌ������

- ��VHDL�����O(sh��)Ӌ����

- �o��ϵ�y(t��ng)����Y(ji��)����

- �M(j��n)��Ӳ����C��

Ŀ �

1 ����1

1.1 �n�}�����3

1.2 �n�}�о��ĬF(xi��n)��4

1.3 ������Ҫ�о���(n��i)�ݼ����x

2 PWMԭ�����n�}ԭ��6

2.1 PWMԭ��6

2.2�n�}ԭ��7

3�n���O(sh��)Ӌԭ����ģ�K��B

3.1 ϵ�y(t��ng)���w�M�ɼ���D

3.2 늙C(j��)�D(zhu��n)�ٿ���ģ�K

3.2.1 �O(sh��)Ӌ˼�뼰ģ�Kԭ��D

3.2.2 �D(zhu��n)��ģ�KVHDL�O(sh��)Ӌ�Z��

3.2.3 �D(zhu��n)��ģ�K����Y(ji��)��

3.3 �����D(zhu��n)�����ģ�K

3.3.1 �O(sh��)Ӌ˼�뼰ģ�Kԭ��D

3.3.2 �����D(zhu��n)��ģ�KVHDL�O(sh��)Ӌ�Z��

3.3.3 �����D(zhu��n)��ģ�K����Y(ji��)��

3.4 �D(zhu��n)�ٜy�����@ʾģ�K

3.4.1 �O(sh��)Ӌ˼�뼰ģ�K�D

3.4.2 �D(zhu��n)�ٜy��ģ�KCHDL�O(sh��)Ӌ�Z��

3.4.3 �D(zhu��n)�ٜy������Y(ji��)��

3.5 ����ģ�K

3.5.1 �O(sh��)Ӌ˼�뼰ԭ��D

3.5.2 ����ģ�KVHDL�O(sh��)Ӌ�Z��

3.5.3 ����ģ�K����Y(ji��)��

4 Ӳ���·���yԇ�Y(ji��)��

4.1 ֱ��늙C(j��)�Ľ�B

4.2 �t��y��ģ�K

4.3 ���_����

4.4 �yԇ

5 �Y(ji��)Փ34

�����īI(xi��n) 35

��� 36

һ ���� 1.1 �n�}�о����� 늙C(j��)����C(j��)����D(zhu��n)�Q�b�ã��䷶���ѱ鼰����(j��ng)��(j��)�ĸ����I(l��ng)��Щ������S���F(xi��n)�������Ӽ��g(sh��)�����Ƽ��g(sh��)��Ӌ��C(j��)���g(sh��)�İl(f��)չ��늙C(j��)�Ŀ��Ƽ��g(sh��)Ҳ�õ����M(j��n)һ���İl(f��)չ��늙C(j��)��(y��ng)�������^ȥ���ε���ͣ���ơ��ṩ������Ŀ�ĵđ�(y��ng)�ã������������ٶȡ�λ�á��D(zhu��n)�ص��M(j��n)�о��_�Ŀ��ƣ�ʹ���(q��)�ӵęC(j��)е�����A(y��)���Ҫ���ù������M(j��n)�п��ƣ����A(y��)���Ŀ��Ʒ�����Ҏ(gu��)��ָ���D(zhu��n)׃�������ęC(j��)е�\�ӣ��@�N���Ϳ��Ƽ��g(sh��)�ѽ�(j��ng)���ǂ��y(t��ng)�ġ�늙C(j��)���ơ�����늚���ӡ����ǡ��\�ӿ��ơ����\�ӿ���ʹ�����ƙC(j��)е�\�ӌ��F(xi��n)���_��λ�ÿ��ơ��ٶȿ��ơ����ٿ��ơ��D(zhu��n)�ػ����Ŀ��ƣ��Լ��@Щ�����ƃ����ľC�Ͽ��ơ� 1.2 �n�}�о��ĬF(xi��n)�� �������,������Ӽ��g(sh��)�cӋ��C(j��)���g(sh��)���w�ٰl(f��)չ����Ƭ�C(j��)���ռ�,���{(di��o)���b�����ܼ�����С�ͻ������ܻ�����l(f��)չ�����⽻ֱ��ϵ�y(t��ng)��(sh��)�ֻ��ѽ�(j��ng)�_(d��)�������A�Ρ���̎�����鼼�g(sh��)���ĵĔ�(sh��)�ֿ���ϵ�y(t��ng)Ӳ���·�Ę�(bi��o)��(zh��n)���̶ȸߣ���Ҫ�ɱ��ͣ������������Ĝض�Ư���������Ӱ푡���(sh��)�ֿ���ϵ�y(t��ng)�܉���Ч���M(j��n)��߉ �Д�͏�(f��)�s���\�㣬��������ͬ��һ�㾀���{(di��o)��(ji��)���(y��u)�����m��(y��ng)�ԡ��Ǿ��ԡ����ܻ��ȿ���Ҏ(gu��)�ɡ�������C(j��)���Ʈa(ch��n)��PWM��̖�����C(j��)���Ƭ�C(j��)�a(ch��n)��PWM��̖���Σ���Ҫͨ�^D/A�D(zhu��n)�Q���a(ch��n)����X��늉����O(sh��)�Å���늉���ͨ�^���ģ�M���^��ݔ��PWM���Σ��������·���^��(f��)�s����Ƭ�C(j��)���mȻD S P �� ���� ��PWM��̖�����@늙C(j��)���a����̖�����������䌦IC���� PWM�� ̖ ��ͨ ����(sh��)Ŀ��늙C(j��)���a�����@ͨ����(sh��)Ŀ���ޡ�������ֱ��늙C(j��)�Ŀ��ƺ��y�M��Ҫ�� ���ڬF(xi��n)���ɾ����T���FPGA��ֱ��늙C(j��)�Ŀ��Ʋ���, �錍�F(xi��n)늄әC(j��)��(sh��)�ֿ����ṩ��һ�N��Ч�ķ�����FPGA�� �����м��ɶȸߡ��w�eС���\���ٶȿ졢�����ĵ����c����FPGA�팍�F(xi��n)�� ·PWM�{(di��o)�أ���(n��i)���Ԏ���(sh��)ģ׃�Q���ܣ�������Ҫ��Ӕ�(sh��)ģ�D(zhu��n)�Q�O(sh��)�䣬��ʽ���Σ��`��С����������(qi��ng)���Æ�Ƭ�C(j��)��DSP�Ŀ��ƶ��y���_(d��)��ͬ�ӵĿ���Ч�� 1.3 �n�̵���Ҫ�о���(n��i)�ݼ����x FPGA���_�l(f��)�Z�ԣ�VHDL�Z�ԣ���һ�N���ڔ�(sh��)��ϵ�y(t��ng)�O(sh��)Ӌ�͜yԇ��Ӳ�������Z�ԣ�Ҳ���҂����ҘO���ƏV��һ�N��(bi��o)��(zh��n)�Z�ԡ����n�}����FPGA����ƺ��ģ��W(xu��)��(x��)ֱ��늙C(j��)PWM��FPGA���ƣ�ͨ�^PWM�Ŀ��ƣ����F(xi��n)��ֱ��늙C(j��)���D(zhu��n)�ٜy�����D(zhu��n)���{(di��o)��(ji��)���D(zhu��n)����ơ� �O(sh��)Ӌֱ��늙C(j��)����ϵ�y(t��ng)�܉��ְl(f��)�]늙C(j��)�����ԣ�ͨ�^���n�}��һ����Ӗ(x��n)�����ڲ���Y�ϵĻ��A(ch��)�ϣ��˽�FPGA���Ƶ�һЩ�������g(sh��)�����������ϵ�y(t��ng)�ķ��������c���F(xi��n)����һ����ͨ�^�����O(sh��)Ӌ���O(sh��)Ӌ������(y��ng)�Ŀ���ϵ�y(t��ng)���Ԍ��F(xi��n)��ֱ��늙C(j��)�D(zhu��n)�ٵĜy�����D(zhu��n)�ٵ��{(di��o)��(ji��)���D(zhu��n)��Ŀ��ƣ����Դ����B(y��ng)�Լ����ԌW(xu��)�̈́����������Ķ����ӹ������M(j��n)һ������������õĻ��A(ch��)�� 2.1 PWMԭ�� �}�_�����{(di��o)�ƣ�PWM����Ӣ�ġ�Pulse Width Modulation���Ŀs�������Q�}���{(di��o)�ơ���������̎�����Ĕ�(sh��)��ݔ���팦ģ�M�·�M(j��n)�п��Ƶ�һ�N�dz���Ч�ļ��g(sh��)���V����(y��ng)���ڜy����ͨ�ţ����ʿ����c׃�Q���S���I(l��ng)�� �}�_�����{(di��o)�ƣ�PWM����һ�N��ģ�M��̖�ƽ�M(j��n)�Д�(sh��)�־��a�ķ�����ͨ�^�߷ֱ���Ӌ��(sh��)����ʹ�ã�������ռ�ձȱ��{(di��o)���Á팦һ�����wģ�M��̖���ƽ�M(j��n)�о��a��PWM��̖��Ȼ�ǔ�(sh��)�ֵģ�����ڽo�����κΕr�̣��M��ֵ��ֱ�����Ҫô��ȫ��(ON)��Ҫô��ȫ�o(OFF)��늉������Դ����һ�Nͨ(ON)���(OFF)���؏�(f��)�}�_���б��ӵ�ģ�Mؓ(f��)�d��ȥ�ġ�ͨ�ĕr����ֱ����늱��ӵ�ؓ(f��)�d�ϵĕr��ĕr���ǹ�늱����_�ĕr��ֻҪ��������κ�ģ�Mֵ������ʹ��PWM�M(j��n)�о��a�� PWM��һ����(y��u)�c�Ǐ�̎����������ϵ�y(t��ng)��̖���ǔ�(sh��)����ʽ�ģ��o���M(j��n)�Д�(sh��)ģ�D(zhu��n)�Q����̖���֞锵(sh��)����ʽ�Ɍ���Ӱ푽�����С����ֻ���ڏ�(qi��ng)�����Ԍ�߉1��׃?y��u)�߉�?��?q��)�߉�?��׃?y��u)�߉�?�r��Ҳ���܌���(sh��)����̖�a(ch��n)��Ӱ푡�

�����ֿ�����������(qi��ng)��PWM������ģ�M���Ƶ�����һ����(y��u)�c�������@Ҳ����ijЩ�r��?q��)�PWM����ͨ�ŵ���Ҫԭ��ģ�M��̖�D(zhu��n)��PWM���ԘO������Lͨ�ž��x���ڽ��նˣ�ͨ�^�m��(d��ng)?sh��)�RC��LC�W(w��ng)�j(lu��)���ԞV���{(di��o)�Ƹ��l����������̖߀ԭ��ģ�M��ʽ��

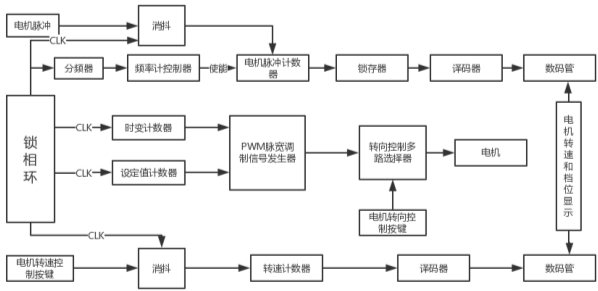

��֮��PWM�Ƚ�(j��ng)��(j��)����(ji��)�s���g����������(qi��ng)����һ�Nֵ�ÏV�̎����S���O(sh��)Ӌ��(y��ng)����ʹ�õ���Ч���g(sh��)�� 2.2 �n�}ԭ�� һ����}���{(di��o)��PWM��̖��ͨ�^ģ�M���^���a(ch��n)���ģ����^����һ�˽ӽo���ą���늉�����һ�˽������Ծ������ӵ���X��늉�����(d��ng)��X��늉�С�څ���늉��rݔ�����ƽ����(d��ng)��X��늉����څ���늉��rݔ�����ƽ����׃����늉��Ϳ��Ը�׃PWM�����и��ƽ�Č��ȡ����Æ�Ƭ�C(j��)�a(ch��n)��PWM��̖���Σ���Ҫͨ�^DA�b�Q���a(ch��n)����X��늉����O(sh��)�Å���늉���ͨ�^���ģ�M���^��ݔ��PWM���Σ��������·���^��(f��)�s�� FPGA�еĔ�(sh��)��PWM�����cһ���ģ�MPWM���Ʋ�ͬ����FPGA�a(ch��n)��PWM���Σ�ֻ��FPGA��(n��i)���YԴ�Ϳ��Ԍ��F(xi��n)���Ô�(sh��)�ֱ��^��������^������һ�˽��O(sh��)��ֵӋ��(sh��)��ݔ������һ�˽Ӿ����f��Ӌ��(sh��)��ݔ������(d��ng)����Ӌ��(sh��)����Ӌ��(sh��)ֵС���O(sh��)��ֵ�O(sh��)��ֵ�rݔ�����ƽ����(d��ng)Ӌ��(sh��)ֵ�����O(sh��)��ֵ�rݔ�����ƽ�� 3.1 ϵ�y(t��ng)���w�M�ɼ���D ֱ��늙C(j��)�����·��(g��u)˼��D1��ʾ�������O(sh��)Ӌ������4��ģ�K�M�ɡ�

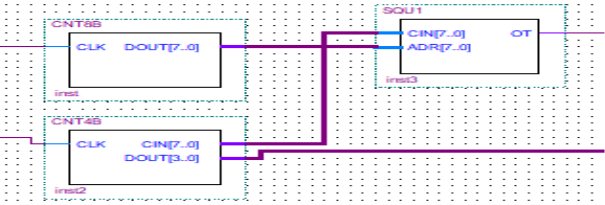

�D1 ֱ��늙C(j��)���ƿ�ϵ�y(t��ng)�D ��һ��ģ�K��PWM�}���{(di��o)����̖�l(f��)��ģ�K���@��ģ�KҲ���Á������D(zhu��n)�ٵ�ģ�K��ͨ�^�O(sh��)Ӌ�ɂ�Ӌ��(sh��)����ֵ��һ��Ӌ��(sh��)����ֵ�Ǹ���(j��)�r犕r�̸�׃�ģ���׃�ĕr��l�ʁ����i��h(hu��n)���@����@��Ӌ��(sh��)���������r׃Ӌ��(sh��)�������@�ǂ�8��Ӌ��(sh��)����ݔ���Ĕ�(sh��)��(j��)�ஔ(d��ng)����X����̖����һ��Ӌ��(sh��)����ֵ��ͨ�^�nλ���I��Q���ģ����I����һ�Σ�Ӌ��(sh��)��������(y��ng)�ļ�һ���ߜpһ���@����@��Ӌ��(sh��)���������O(sh��)��ֵӋ��(sh��)�������@�Ԟ��ǂ�8��Ӌ��(sh��)�������е�4λ�O(sh��)����㶨1111����4���ɰ��I���ơ��@�ɂ�Ӌ��(sh��)ģ�K��ֵͨ�^���^������ݔ��һ��һ��ռ�ձȵ�PWM����ͨ�^�O(sh��)��Ӌ��(sh��)����ֵ���ܸ�׃PWM����ռ�ձȣ��@�ӾͿ�����늙C(j��)���D(zhu��n)�٣�����Ҳ��ͨ�^�քӰ��I����늙C(j��)���D(zhu��n)�١� �ڶ���ģ�K��늙C(j��)�����D(zhu��n)ģ�K���@��ģ�K��ͨ�^���I�����Ƶģ���(d��ng)����һ�ΰ��I��늙C(j��)���D(zhu��n)���׃һ�Ρ��@��ģ�K����ͨ�^�à�B(t��i)�C(j��)�팍�F(xi��n)�����D(zhu��n)��B(t��i)�ĸ�׃��늙C(j��)���D(zhu��n)��һ����B(t��i)�����D(zhu��n)��һ����B(t��i)���à�B(t��i)�C(j��)�����@��ģ�K��ʹ늙C(j��)�����D(zhu��n)ģ�K���ӷ�(w��n)���� ������ģ�K��늙C(j��)�D(zhu��n)�ٜy���@ʾģ�K�����n����ͨ�^�t���늜y���D(zhu��n)�ٵģ��@��ģ�K���P(gu��n)�I���}�Ǯa(ch��n)��һ��1s���l�T�r�g��ͨ�^ӛ��1sݔ����}�_��(sh��)�����棬Ȼ���g�aͨ�^��(sh��)�a���@ʾ��Ӳ���·�ϡ���D3.1��ʾ���ⲿ�}�_ͨ�^������ֱ���M(j��n)��1sݔ���}�_Ӌ��(sh��)����1s�Y(ji��)����ӛ�µ��}�_��(sh��)�������������g�a���@ʾ������ ���Ă�ģ�K������ģ�K������ģ�K�ǂ��ز����ٵ�ģ�K���ڱ��n���У����I��Ҫ�������������͕����F(xi��n)����(w��n)���ĬF(xi��n)��ݔ���}�_Ҳ��Ҫ�������������ͳ��F(xi��n)���g(sh��)����(zh��n)��������ԭ���ǣ�һ����Ҫ��������̖����һ�����l�ʵ��}�_��̖����(d��ng)������̖̎�ڸ��ƽ�r�����l����̖ͬ�r�_ʼӋ��(sh��)����(d��ng)Ӌ��(sh��)�_(d��)���A(y��)�O(sh��)��Ӌ��(sh��)ֵ�r�����ƽ�Ԟ���ƽ���t�@�����ƽ��̖��Ч����֮������_(d��)Ӌ��(sh��)ֵ�r������̖׃?y��u)���ƽ���t�@�����ƽ�oЧ��ͬ�����ƽһ�ӡ� ��ô�����@4��ģ�K�͘�(g��u)�����ψD��ֱ��늙C(j��)�����·�� 3.2 늙C(j��)�D(zhu��n)�ٿ���ģ�K 3.2.1 �O(sh��)Ӌ˼�뼰ģ�Kԭ��D ����FPGA����ֱ��늙C(j��)�D(zhu��n)�ٕr��������Ǹ�׃ÿ��PWM���ڵ�ռ�ձȡ����@����Ҫ�a(ch��n)��һ���O(sh��)��ֵӋ��(sh��)����һ���r׃Ӌ��(sh��)����һ����(sh��)�ֱ��^����ԭ��D��D2��ʾ�� ���w���f���O(sh��)��ֵӋ��(sh��)�����Ǹ���(j��)���I���r�xȡ�IJ�ͬ�nλ��ݔ��һ����ͬ�Ĕ�(sh��)ֵ�������O(sh��)Ӌ�ٶȷ֞�ʮ���n��ÿ����һ�n���D(zhu��n)������(y��ng)���ӣ�ʮ���n�r�D(zhu��n)���_(d��)�����(j��)�ˣ�����Ҫ�O(sh��)Ӌһ���nλ�{(di��o)��(ji��)ģ�K����(d��ng)ݔ�벻ͬ�ęnλ��(sh��)ֵ�r��Ҫݔ��һ��Ӌ��(sh��)ֵ���@����(sh��)ֵҎ(gu��)�����O(sh��)��ֵӋ��(sh��)����ݔ����(sh��)ֵ����(d��ng)�nλ���ӕr���O(sh��)��ֵӋ��(sh��)����ֵ����(y��ng)���ӣ��Ķ���׃PWM��̖ռ�ձȣ�ʹ��ռ�ձ�����늙C(j��)�D(zhu��n)�ټӿ졣�O(sh��)��ֵӋ��(sh��)����ݔ���ӵ����^����һ�ˣ��͕r׃Ӌ��(sh��)���Ĕ�(sh��)ֵ�M(j��n)�б��^���r׃Ӌ��(sh��)���ĕr犔�(sh��)ֵ���Ԍ��i��h(hu��n)�ķ��l���r犔�(sh��)ֵ�ܛQ��늙C(j��)����(y��ng)�r�g�Ŀ����� ����ҵ�늙C(j��)һ�㶼���_(d��)��100�D(zhu��n)���ң�����Ӌ��(sh��)����λ��(sh��)����(y��ng)����7λ�������͵�Ԓ��ÿ��׃һλ��(sh��)������(y��ng)���D(zhu��n)��(sh��)߀�_(d��)����һ�D(zhu��n)���@�ӾͲ��܌�ÿһ�D(zhu��n)�M(j��n)�м�(x��)�֣�Ҳ�͟o�����_����늙C(j��)���D(zhu��n)�١����O(sh��)Ӌ��Ӌ��(sh��)��λ��(sh��)�O(sh��)����8λ�� ��ôPWM��̖��ռ�ձȾ��w������S���nλ�IJ�ͬ����׃���أ���ǰ���ѽ�(j��ng)�O(sh��)Ӌ����һ���O(sh��)��ֵӋ��(sh��)����һ���r׃Ӌ��(sh��)�����@�ɂ���(sh��)ֵ���ڔ�(sh��)�ֱ��^��ݔ����M(j��n)�б��^����(d��ng)�O(sh��)��ֵӋ��(sh��)����ֵ���ڕr׃Ӌ��(sh��)����ֵ�r�����^��ݔ�����ƽ����(d��ng)�O(sh��)��ֵӋ��(sh��)����ֵС�ڕr׃Ӌ��(sh��)����ֵ�r�����^��ݔ�����ƽ�� ����O(sh��)��ֵӋ��(sh��)���ĵ���λ���1������λ�ɰ��I�Q������(d��ng)���I����ȥһ�Σ�����λ�ͼ�1������@����λ�����Խ���˞�ʲô����ʮ�����nλ��  �D 2 늙C(j��)�D(zhu��n)��ģ�Kԭ��D �D 2 늙C(j��)�D(zhu��n)��ģ�Kԭ��D

�˿ڽ�B�� DOUT[7..0]����8λ�r׃Ӌ��(sh��)����ݔ�� CIN[7..0]����8λ�O(sh��)��ֵӋ��(sh��)��ݔ�� DOUT[3..0]���Ǚnλ��4λݔ�� ���Ì���(y��ng)ʮ�����nλ OT�����^�Y(ji��)�� 3.2.2���D(zhu��n)��ģ�KVHDL�O(sh��)Ӌ�Z�� PWM�}���{(di��o)����̖���l(f��)��ģ�K��(d��ng)�r׃Ӌ��(sh��)ֵС���O(sh��)��ֵ�rݔ�����ƽ����(d��ng)�r׃Ӌ��(sh��)ֵ�����O(sh��)��ֵ�rݔ�����ƽ�� ����Y(ji��)����D3 - USE IEEE.STD_LOGIC_1164.ALL;

- USE IEEE.STD_LOGIC_UNSIGNED.ALL;

- ENTITY SQU1 IS

- PORT ( CIN,ADR : IN STD_LOGIC_VECTOR(7 DOWNTO 0);

- OT : OUT STD_LOGIC );

- END SQU1;

- ARCHITECTURE BHV OF SQU1 IS

- BEGIN

- PROCESS(CIN) BEGIN

- IF (ADR<CIN) THEN OT<='0';

- ELSE OT<='1'; END IF;

- END PROCESS;

- END BHV;

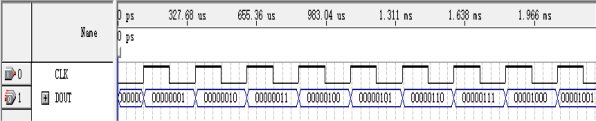

- 8��r׃Ӌ��(sh��)�����@��8��Ӌ��(sh��)���Ǹ���(j��)�r�0Ӌ��(sh��)�� ����Y(ji��)����D4

- LIBRARY IEEE;

- USE IEEE.STD_LOGIC_1164.ALL;

- USE IEEE.STD_LOGIC_UNSIGNED.ALL;

- ENTITY CNT8B IS

- PORT (CLK : IN STD_LOGIC;

- DOUT: OUT STD_LOGIC_VECTOR(7 DOWNTO 0) );

- END CNT8B;

- ARCHITECTURE BHV OF CNT8B IS

- BEGIN

- PROCESS(CLK)

- VARIABLE CQ : STD_LOGIC_VECTOR(7 DOWNTO 0);

- BEGIN

- IF CLK'EVENT AND CLK = '1' THEN

- IF CQ<255 THEN --���Ӌ��(sh��)��255

- CQ := CQ + 1 ;

- ELSE CQ := (OTHERS=>'0') ;

- END IF;

- END IF;

- DOUT <= CQ;

- END PROCESS;

- END BHV;

- 8���O(sh��)��ֵӋ��(sh��)�� ����Y(ji��)����D5

- LIBRARY IEEE;

- USE IEEE.STD_LOGIC_1164.ALL;

- USE IEEE.STD_LOGIC_UNSIGNED.ALL;

- ENTITY CNT4B IS

- PORT (CLK : IN STD_LOGIC;

- CIN: OUT STD_LOGIC_VECTOR(7 DOWNTO 0); --8���O(sh��)��ֵ

- DOUT: OUT STD_LOGIC_VECTOR(3 DOWNTO 0) ); --4λ�nλ��̖

- END CNT4B;

- ARCHITECTURE BHV OF CNT4B IS

- SIGNAL CQ1 : STD_LOGIC_VECTOR(3 DOWNTO 0);

- BEGIN

- PROCESS(CLK)

- VARIABLE CQ : STD_LOGIC_VECTOR(3 DOWNTO 0);

- BEGIN

- CQ1 <="1111"; --����λ�A(y��)�O(sh��)��1111

- IF CLK'EVENT AND CLK = '1' THEN --CLK�����ص���r

- IF CQ<15 THEN

- CQ := CQ + 1 ;

- ELSE CQ := (OTHERS=>'0') ;

- END IF;

- END IF;

- DOUT <=CQ(3 DOWNTO 0);

- CIN <=CQ&CQ1;

- END PROCESS;

- END BHV;

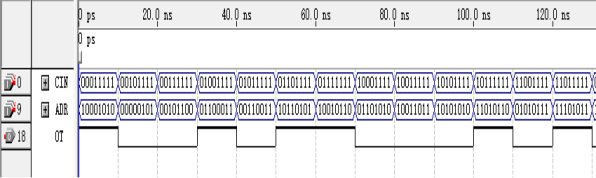

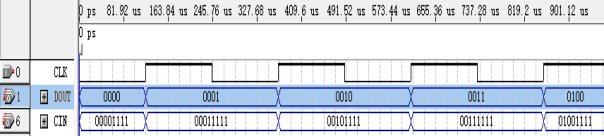

3.2.3���D(zhu��n)��ģ�K����Y(ji��)�� �ɷ���Y(ji��)�����Կ������_���M�㮔(d��ng)�r׃Ӌ��(sh��)ֵС���O(sh��)��ֵ�rݔ�����ƽ����(d��ng)�r׃Ӌ��(sh��)ֵ�����O(sh��)��ֵݔ�����ƽ��

�D3 ���^������D

�D4 �r׃Ӌ��(sh��)������D

�D5 �O(sh��)��Ӌ��(sh��)������D 3.3 �����D(zhu��n)�����ģ�K 3.3.1 �O(sh��)Ӌ˼�뼰ԭ��D �@��ģ�K���ǰ��I������늙C(j��)���D(zhu��n)��������?q��)��?y��ng)��2�Р�B(t��i)����˿���ͨ�^���I�팍�F(xi��n)��B(t��i)�ĸ�׃��ÿ��һ�Π�B(t��i)��׃һ�Ρ���(d��ng)Ȼ�@�(y��ng)ԓ߀��һ��ʹ�ܿ��ƣ����ԁ톢�Ӻ͕�ͣ늙C(j��)�D(zhu��n)�ӡ� ����ԭ�� ��(d��ng)���IK1��һ�ΰ��µĕr�ٶ���M�xֵ�oM0���tM1��(y��ng)�xֵ����ƽ����(d��ng)���I�ڶ��ΰ��µĕr�t��M�xֵ�oM1���tM0��(y��ng)�xֵ����ƽ����˷���(f��)�ľ͌��F(xi��n)��늙C(j��)�����D(zhu��n)�����D(zhu��n)����(d��ng)���IK3�����r���t늙C(j��)�_ʼ�D(zhu��n)�ӣ���(d��ng)K3�ٴα����r���t늙C(j��)ֹͣ�D(zhu��n)�ӡ��O(sh��)Ӌԭ��D��D6 �D6 �����D(zhu��n)ģ�Kԭ��D �˿ڽ�B M ������^��ݔ�����ƽֵ SL �����IK1��ݔ��ˣ��Á����������D(zhu��n)�� M0��M1 ����늙C(j��)�ăɂ�ݔ��ˡ� K �� �鰴�IK3��ݔ��ˣ��Á�����늙C(j��)�Ć��Ӻ͕�ͣ

3.3.2 �����D(zhu��n)��ģ�KVHDL�O(sh��)Ӌ�Z�� ����Y(ji��)����D7��ʾ - LIBRARY IEEE;

- USE IEEE.STD_LOGIC_1164.ALL;

- USE IEEE.STD_LOGIC_UNSIGNED.ALL;

- use ieee.std_logic_arith.all;

- ENTITY SLT IS --M����^ֵ

- PORT (SL, M, K : IN STD_LOGIC; --SL�������D(zhu��n)���I

- m0, m1: OUT STD_LOGIC ); --K�醢��ֹͣ���I

- END SLT;

- ARCHITECTURE BHV OF SLT IS

- TYPE FSM_ST IS (S0,S1); --�����ɷN��B(t��i)

- SIGNAL c_st, next_state: FSM_ST :=S0;

- BEGIN

- REG : PROCESS (SL)

- BEGIN

- IF SL='1'AND SL'EVENT THEN c_st <= next_state;--���I���£��ΑB(t��i)׃?y��u)�F(xi��n)�B(t��i)

- END IF;

- END PROCESS REG ;

- COM : PROCESS (c_st, M) BEGIN

- IF K='1' THEN m0 <='0'; m1 <='0'; --����и��ƽ����ôm0,m1����0���t늙C(j��)���D(zhu��n)

- ELSE

- CASE c_st IS

- WHEN S0 => m0 <= M; m1 <='0'; next_state <= S1;

- WHEN S1 => m1 <= M; m0 <='0'; next_state <= S0;

- END CASE;

- END IF;

- END PROCESS;

- END BHV;

�����������ģ�Kʹ�à�B(t��i)�C(j��)�팍�F(xi��n)�ƽ���D(zhu��n)�Q��K����ƽ�r��ݔ����0늙C(j��)���ӣ����ƽ�r����ʼ��B(t��i)��S0,��(d��ng)SL��������׃���ĕr���B(t��i)���D(zhu��n)��ΑB(t��i)�� 3.3.3 �����D(zhu��n)��ģ�K����Y(ji��)�� ����(j��)�D7 ��֪����(d��ng)�z�ySL��һ��������׃���ĕr��M1�ľͺ�M��ͬ��ͬ�rMO�͞���ƽ����(d��ng)�z�ySL�ڶ���������׃���ĕr��M0�ľͺ�M��ͬ��ͬ�rM1�͞���ƽ�������^�����@�ɷN��B(t��i)�ͽ����M(j��n)�С���(d��ng)�z�y��K����ƽ�r��M1��M2������ƽ�� �D7 �����D(zhu��n)��ģ�K����D

3.4���D(zhu��n)�ٜy�����@ʾģ�K 3.4.1 �O(sh��)Ӌ˼�뼰ģ�K�D �O(sh��)Ӌ�@��ģ�K���P(gu��n)�I���}�Ǯa(ch��n)��һ��1s���l�T��̖��ӛ��1s�ݔ����}�_��(sh��)���i�棬Ȼ���g�aݔ����Ӳ���·�ϡ��O(sh��)Ӌԭ��D��D8��ʾ�� �D8 �D(zhu��n)�ٜy��ģ�Kԭ��D �˿ڽ�B�� C1�� ���i��h(hu��n)ݔ��5MHz C0: ���i��h(hu��n)ݔ��4096Hz KIN�� ����y�l�� LEDA LEDB����������̖ݔ��

3.4.2�D(zhu��n)�ٜy��ģ�KCHDL�O(sh��)Ӌ�Z�� ��1�����lģ�K��ͨ�^���i��h(hu��n)ݔ����4096Hz�r��M(j��n)�з��l�ԫ@��1 Hz�r犣����l��Ӌ����ģ�KTF_CTRL�ṩ1 S���l�T�r�g���������£� - LIBRARY IEEE ;

- USE IEEE.STD_LOGIC_1164.ALL;

- USE IEEE.STD_LOGIC_UNSIGNED.ALL;

- ENTITY CNT IS

- PORT(CLOCK : IN STD_LOGIC ;COUT : OUT STD_LOGIC);

- END ;

- ARCHITECTURE bhv OF CNT IS

- SIGNAL C1,C2 : STD_LOGIC_VECTOR(8 DOWNTO 0) ;

- SIGNAL M1,M2 : STD_LOGIC ;

- BEGIN

- PROCESS(CLOCK,C1) BEGIN

- IF RISING_EDGE(CLOCK) THEN

- IF (C1="111111111") THEN C1<="000000000"; ELSE C1<=C1+1; END IF;

- IF (C1="000000001") THEN M1<=NOT M1; ELSIF (C1="100000000") THEN M1<=NOT M1;

- END IF;END IF;

- END PROCESS;

- PROCESS (CLOCK,C2) BEGIN

- IF FALLING_EDGE(CLOCK) THEN

- IF(C2="111111111") THEN C2<="000000000"; ELSE C2<=C2+1;END IF;

- IF(C2="000000001") THEN M2<=NOT M2 ; ELSIF (C2="100000000") THEN M2<=NOT M2;

- END IF; END IF;

- END PROCESS;

- COUT<=M1 OR M2;

- END bhv;

- �l��Ӌ����ģ�K:�@��ģ�K�r�a(ch��n)���y�l������̖�ģ�TF_CTRLӋ��(sh��)ʹ����̖CNT_EN�ܮa(ch��n)��һ��1s�}����������̖�������l��Ӌ�е�8λ���M(j��n)��늙C(j��)�}�_Ӌ��(sh��)��CNT10D��ENABLʹ�ܶ��M(j��n)��ͬ�����ƣ�ͬ�r�a(ch��n)��Ӌ��(sh��)������̖LOCK���������£�

- LIBRARY IEEE;

- USE IEEE.STD_LOGIC_1164.ALL;

- USE IEEE.STD_LOGIC_UNSIGNED.ALL;

- ENTITY TF_CTRL IS

- PORT (CLK1 : IN STD_LOGIC; -- 1Hz

- CNT_EN : OUT STD_LOGIC; -- Ӌ��(sh��)���r�ʹ��

- CLR : OUT STD_LOGIC; -- Ӌ��(sh��)������

- LOCK : OUT STD_LOGIC ); -- ݔ���i����̖

- END TF_CTRL;

- ARCHITECTURE behav OF TF_CTRL IS

- SIGNAL Div2CLK : STD_LOGIC;

- BEGIN

- PROCESS( CLK1 )

- BEGIN

- IF CLK1'EVENT AND CLK1 = '1' THEN

- Div2CLK <= NOT Div2CLK;

- END IF;

- END PROCESS;

- PROCESS (CLK1, Div2CLK)

- BEGIN

- IF CLK1='0' AND Div2CLK='0' THEN CLR<='1';-- �a(ch��n)��Ӌ��(sh��)��������̖

- ELSE CLR <= '0'; END IF;

- END PROCESS;

- LOCK <= NOT Div2CLK; CNT_EN <= Div2CLK;

- END behav;

��3��늙C(j��)�}�_Ӌ��(sh��)������(d��ng)ENABL���ƽ�r���SӋ��(sh��)�����ƽ�rֹͣӋ��(sh��)������������Ӌ���}�_��(sh��)�� - LIBRARY IEEE; --8λӋ��(sh��)��

- USE IEEE.STD_LOGIC_1164.ALL;

- USE IEEE.STD_LOGIC_UNSIGNED.ALL;

- ENTITY CNT10D IS

- PORT (CLK : IN STD_LOGIC; -- �r���̖

- CLR : IN STD_LOGIC; -- ������̖

- ENABL : IN STD_LOGIC; -- Ӌ��(sh��)ʹ����̖

- COUT : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);

- DOUT1 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

- DOUT2 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0)); -- Ӌ��(sh��)�Y(ji��)��

- END CNT10D;

- ARCHITECTURE behav OF CNT10D IS

- SIGNAL CQ2 : STD_LOGIC_VECTOR(3 DOWNTO 0);

- SIGNAL CQ3 : STD_LOGIC_VECTOR(3 DOWNTO 0);

- BEGIN

- PROCESS(CLK, CLR, ENABL)

- BEGIN

- IF CLR = '1'

- THEN CQ2 <= (OTHERS=>'0'); CQ3 <= (OTHERS=>'0'); -- ����

- ELSIF CLK'EVENT AND CLK = '1' THEN

- IF ENABL = '1' THEN

- IF CQ2>8 THEN CQ3<=CQ3+1; CQ2(3 DOWNTO 0)<="0000";

- ELSE CQ2 <=CQ2+1;

- END IF;

- END IF;

- END IF;

- END PROCESS;

- COUT <= CQ3&CQ2;

- DOUT1 <=CQ2;

- DOUT2 <=CQ3;

- END behav;

��4���i��ģ�K���i����̖LOAD�������،�Ӌ��(sh��)����ǰ1��犵�Ӌ��(sh��) ֵ�i���M(j��n)�i����LOCK8�У��O(sh��)���i�����ĺ�̎�ǔ�(sh��)��(j��)�@ʾ��(w��n)�����������������Ե���0��̖�������W�q���������£� - LIBRARY IEEE; --8λ�i����

- USE IEEE.STD_LOGIC_1164.ALL;

- ENTITY LOCK8 IS

- PORT ( LK : IN STD_LOGIC;

- D : IN STD_LOGIC_VECTOR(7 DOWNTO 0);

- LEDA: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

- LEDB: OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

- END LOCK8;

- ARCHITECTURE behav OF LOCK8 IS

- BEGIN

- PROCESS(LK, D)

- BEGIN

- IF LK'EVENT AND LK = '1' THEN LEDA <= D(7 DOWNTO 4); LEDB <= D(3 DOWNTO 0);

- END IF;

- END PROCESS;

- END behav;

3.4.3�� �D(zhu��n)�ٜy������Y(ji��)�� �D9 ���lģ�K����Y(ji��)�� �D10 �l��Ӌ����ģ�K����Y(ji��)�� �D11 늙C(j��)�}�_Ӌ��(sh��)ģ�K�½Y(ji��)��

�D12Ӌ��(sh��)����ģ�K����Y(ji��)�� 3.5�� ����ģ�K 3.5.1���O(sh��)Ӌ˼�뼰ԭ��D ����ⰴ�I���Ӻ���ģ�K�a(ch��n)���ɔ_��̖�����Iģ�K���}�_ǰ��(y��ng)��������ģ�KERZP��������ģ�K���õ��Ƕ��r��ʽȥë�̡��ڱ��O(sh��)Ӌ�У�����CLK����̖�l�ʞ�5MHZ,���ƽ���m(x��)�ĕr�g��(d��ng)CLK��Ӌ��(sh��)��12�ĕr������Ч���ƽ�����ƽ���m(x��)�ĕr�g��(d��ng)CLK��Ӌ��(sh��)��7�ĕr������Ч���ƽ��ԭ��D��D13��ʾ �D13 ����ģ�Kԭ��D �˿ڽ�B�� CLK: ����ģ�K�ĕr� KIN: ݔ�����̖ KOUT: ���������̖ 3.5.2������ģ�KVHDL�O(sh��)Ӌ�Z�� - LIBRARY IEEE;

- USE IEEE.STD_LOGIC_1164.ALL;

- USE IEEE.STD_LOGIC_UNSIGNED.ALL;

- ENTITY ERZP IS

- PORT(CLK,KIN : IN STD_LOGIC;

- KOUT : OUT STD_LOGIC );

- END;

- ARCHITECTURE BHV OF ERZP IS

- SIGNAL KL,KH : STD_LOGIC_VECTOR(3 DOWNTO 0);

- BEGIN

- PROCESS(CLK,KIN,KL,KH ) BEGIN

- IF CLK'EVENT AND CLK = '1' THEN

- IF(KIN='0') THEN KL<=KL+1;

- ELSE KL<="0000"; END IF;

- IF(KIN='1') THEN KH<=KH+1;

- ELSE KH<="0000"; END IF;

- IF(KH>"0101") THEN KOUT<='1';

- ELSIF (KL>"0101") THEN KOUT<='0';

- END IF; END IF;

- END PROCESS;

- END;

3.5.3 ����ģ�K����Y(ji��)�� �D14 ����ģ�K����Y(ji��)��

word��ʽ�������O(sh��)Ӌ���51�����d��ַ��

����VHDL��ֱ��늙C(j��)����ϵ�y(t��ng).7z

(113.49 KB, ���d��(sh��): 80)

����VHDL��ֱ��늙C(j��)����ϵ�y(t��ng).7z

(113.49 KB, ���d��(sh��): 80)

|

����TQQ:125739409;���g(sh��)����QQȺ281945664

����TQQ:125739409;���g(sh��)����QQȺ281945664