|

STM32最小系統(tǒng)布線注意事項 本文總結自各種網絡資料,版權歸原作者所有,此總結僅供學習交流之用

- 1、 VSSA,VDDA

- VSSA,VDDA = 2.0~3.6V:為ADC、復位模塊、RC振蕩器和PLL的模擬部分提供供電。使用ADC時,VDD不得小于2.4V。VDDA和VSSA必須分別連接到VDD和VSS,VDDA管腳必須連接到2個外部的去藕電容器(10nF瓷介電容+1μF的鉭電容或瓷介電容),VDDA管腳必須連接到2個外部的去藕電容器(10nF瓷介電容+1μF的鉭電容或瓷介電容)。每一對VDD和VSS管腳都需要使用單獨的去藕電容。每對VDD與VSS都必須在盡可能靠近芯片處分別放置一個10nF~100nF的高頻瓷介電容。在靠近VDD3和VSS3的地方放置一個4.7μF~10μF的鉭電容或瓷介電容。VDD與VDDA之間的電壓差不能超過300mV。典型連接:

盡管所有VDD和所有VSS在內部相連,在芯片外部仍然需要連接上所有的VDD和VSS因為導線較細,內部連接負載能力較差,抗干擾的能力也較差,如果漏接VDD或VSS,容易造成內部線路損壞,同時抗干擾能力下降。 電源線和地線之間連接具有良好高頻特性的電容,即在靠近電源一端應放置一個0.1μF(104電容)和一個1~10μF的電容。 采用LM1117-3.3V(AMS1117)供電 2、I/O引腳間的串擾:模擬信號線的周圍布置地線產生屏蔽,能有效地減小串擾干擾噪聲 - 復位信號低脈沖至少保持300ns

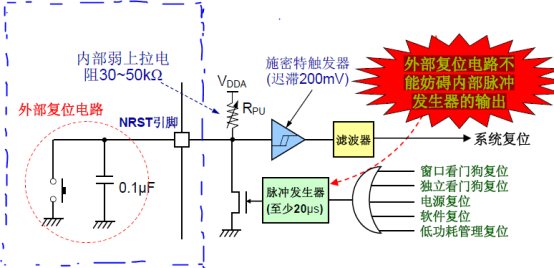

- 在產生內部復位信號時,NRST引腳會輸出一個低電平

- 外部復位電路不能妨礙內部脈沖 發(fā)生器的輸出

復位電路如下圖所示: 3、BOOT0,BOOT1管腳 兩個管腳在芯片復位時的電平狀態(tài)決定了芯片復位后從哪個區(qū)域開始執(zhí)行程序。 | | | | | | | | 從系統(tǒng)存儲器啟,此模式啟動的程序功能由廠家設置。 | | | |

一般BOOT0和BOOT1跳線都跳到0(地)。只是在ISP下載的情況下,BOOT0=1,BOOT1=0 ,下載完成后,把BOOT0的跳線接回0,也即BOOT0=0,BOOT1=0 。 ISP下載電路: - nJTRST、JTDI、JTMS/SWDIO和JTDO引腳推薦使用10K電阻上拉至VDD,JTCK/SWCLK引腳推薦使用10K電阻下拉至VSS。

- 仿真工具(STLink,JLink)通過20個腳插座的1號腳判斷目標板是否供電,通過19號腳可以向目標板供電(3.3V,<100mA)。

- 第1和第2管腳接VDD,其實是對應74HC244的芯片電壓,如果74244采用的3.3V的低壓芯片的話,這個JTAG-VDD就接3.3V。如果采用的是5V電壓的74244的話,這個JTAG-VDD就是5V。

5、RTC時鐘電路 RTC時鐘要求使用的32.768振蕩器的寄生電容是6pF,這個電容區(qū)別于振蕩器外部接的負載電容;

6、FSMC

對應100pin或144pin,FSMC的功能與I2C是存在沖突的,如果FSMC時鐘打開,I2C 1的硬件模式無法工作。這在STM32F10xxx的勘誤表中是有描述的。

|