|

|

�l(f��)�F(xi��n)һ���ܺõ�FPGA�_�l(f��)ȫ������ӕ������o��ҌW(xu��)��(x��)�������Ƿ��棺

Ŀ�

ǰ�� 2

��һ�¡���ʲô���̎�Ҫ����FPGA�_�l(f��)֪�R(sh��)�� 5

�ڶ��¡�FPGA����֪�R(sh��)�c�l(f��)չڅ��(sh��) 7

2.1 FPGA�Y(ji��)��(g��u)����ԭ�� 7

2.1.1 ��(m��ng)��ɾ͂��I(y��) 7

2.1.2 FPGA�Y(ji��)��(g��u) 8

2.1.3 ܛ�ˡ�Ӳ���Լ��̺˵ĸ��� 15

2.1.4 �Ŀɾ��������l(f��)չ��FPGAδ��څ��(sh��) 15

�����¡�FPGA��Ҫ����(y��ng)���c�a(ch��n)Ʒ 17

3.1.1 ِ�`˼��Ҫ�a(ch��n)Ʒ��B 17

�����¡�FPGA�_�l(f��)�������� 29

4.1 ����FPGA�_�l(f��)�����cע�����(xi��ng) 29

4.2 ����FPGA��SOC�O(sh��)Ӌ(j��)���� 32

����FPGA�ĵ���SOC�_�l(f��)���̞� 32

�����¡�FPGA��(sh��)��(zh��n)�_�l(f��)���� 33

5.1 FPGA�����x�ͳ��R(sh��) 33

5.1.1�����Ĺ�؛�������_�l(f��)���ߵ�֧�� 33

5.1.2 ������Ӳ���YԴ 33

5.1.3 늚�ӿژ�(bi��o)��(zh��n) 34

5.1.4 �������ٶȵȼ�(j��) 35

5.1.5 �����Ĝضȵȼ�(j��) 35

5.1.6 �����ķ��b 35

5.1.7 �����ăr(ji��)�� 35

5.2 ����M(j��n)��FPGA�O(sh��)Ӌ(j��)����ϵ�y(t��ng)Ҏ(gu��)�� 36

5.3���C�Ϻͷ��漼�� 37

5.3.1 �C�Ϲ���XST��ʹ�� 37

5.3.2 ����ISE�ķ��� 42

5.3.3 ��FPGA�ӿ����P(gu��n)���O(sh��)���Լ��r(sh��)����� 45

5.3.4 �C�ϸ��ֽ���XST��11��(g��)���� 51

5.4 ��Ҏ(gu��)ģ�O(sh��)Ӌ(j��)�����ľC�ϺͲ������} 52

5.5 FPGA���P(gu��n)�·�O(sh��)Ӌ(j��)֪�R(sh��) 54FPGA�_�l(f��)ȫ���ԡ����̎���(chu��ng)���O(sh��)Ӌ(j��)���� �σ�(c��) ���A(ch��)ƪ

5.5.1 �����· 54

5.5.2 ����ģʽ������õ�FPGA����ģʽ 56

5.5.3 SPI����Flash����ģʽ 58

5.5.4 �Ĵ�����ģʽ 62

5.5.5 JTAG����ģʽ 63

5.5.6 System ACE���÷��� 64

5.6 ��Ҏ(gu��)ģ�O(sh��)Ӌ(j��)���{(di��o)ԇ��(j��ng)�(y��n) 68

5.6.1 ChipScope Pro�M����(y��ng)��(sh��)�� 68

5.7 FPGA�O(sh��)Ӌ(j��)��IP���㷨��(y��ng)�� 74

5.7.1 IP�˾C�� 74

5.7.2 FFT IP�ˑ�(y��ng)��ʾ�� 75

5.8 ِ�`˼ FPGA�Č���HDL�_�l(f��)���� 79

5.8.1 ِ�`˼ FPGA���wϵ�Y(ji��)��(g��u)���c(di��n) 79

5.8.2 ِ�`˼ FPGA оƬ���ô��a�L(f��ng)�� 79

ISE�cEDK�_�l(f��)����֮�r(sh��)��ƪ 83

5.10 ��һ���_�l(f��)����ISE Design Suit10.1��B 85

5.10.1 ISE Design Suit10.1�C�� 85

5.10.2 ISE Design Suit 10.1�Ą�(chu��ng)������ 85

5.11 ISE�c������ܛ�������ʹ�ü��� 92

5.11.1 Synplify Proܛ����ʹ�� 92

5.11.2 ModelSimܛ����ʹ�� 99

5.11.3 Synplify Pro��ModelSim��ISE��(li��n)���_�l(f��)���� 104

5.11.4 ISE�cMATLAB��(li��n)��ʹ�� 105

5.12 ����FPGA�����O(sh��)Ӌ(j��)������(g��)����(zh��n) 108

5.13 ����֮·����FPGA�O(sh��)Ӌ(j��)�_�l(f��)�е��M(j��n)�A·�� 111

���һ��FPGA�_�l(f��)�YԴ���R 112

��䛶�����ί��Ϣ�c��ӛ 113

����������(qu��n)�� 114

��һ�¡���ʲô���̎�Ҫ����FPGA�_�l(f��)֪�R(sh��)��

���ߣ�����(gu��)������

2008 �������ij����Ƕ��ʽϵ�y(t��ng) IT ��˾���ˎ�����a(ch��n)Ʒ�ۺ̎����ھ����g(sh��)֧�ֹ��̎����õ������� �a(ch��n)Ʒ���e���� ASIC/FPGA ���A(ch��)����(ch��ng)��Ӗ(x��n)�����ں�����?y��n)鱣���ƶȶ�ֻ�ܽ��|���弉(j��)�·�D�� LAYOUT��ͬ�r(sh��) �� ASIC/FPGA ���ǵ��͵� SoC ��(y��ng)�ã�ͨ��ֻ�nj� ASIC/FPGA ��(d��ng)���ںЁ����⣬��y(c��)���x�D��ɹ�˾�c�ⲿ ����˾��(n��i)�������ğoЧ��ͨ����Ӗ(x��n)�Y(ji��)���� , ���c������ʾ ASIC/FPGA �İ�ʽ�����O������ˌ�(du��)�a(ch��n)Ʒ�����⣬ ��Ч��Q�˺������Ϳ͑�������ƫ���Ԇ��}��������Ӗ(x��n)�Ĺ��̎�С L ��ʾ ����FPGA ͬ�r(sh��)���Џ�(qi��ng)���̎������ ����ȫ���O(sh��)Ӌ(j��)���ɶȣ������������ИI(y��)��(du��)�� ASIC ���O(sh��)Ӌ(j��)������ wafer fabrication ֮ǰ , Ҳ����ʹ�� FPGA ���� ����(g��)ϵ�y(t��ng)�İ弉(j��)���棬�W(xu��)��(x��) FPGA �_�l(f��)֪�R(sh��)�����������҂��ķ���(w��)�|(zh��)���Ă�(g��)�˽Ƕ��vҲ�������Լ��ăr(ji��)ֵ����

��(sh��)�H�ϣ�С L ֻ���Ї�(gu��)��(sh��)ʮ�f FPGA �_�l(f��)���̎���һ��(g��)�sӰ��Ŀǰ���S�� FPGA �Ŀɾ���߉оƬ����(j��)�� �ɾ���ϵ�y(t��ng)��(j��)оƬ�������·�еĽ�ɫ�ѽ�(j��ng)�������߉�z�����쵽��(sh��)����̖(h��o)̎�����ӿڡ����ܶ��\(y��n)��ȸ��V 韵ķ�������(y��ng)���I(l��ng)��Ҳ��ͨ�����쵽���M(f��i)��ӡ���܇��ӡ����I(y��)���ơ��t(y��)����ӵȸ����I(l��ng)�F(xi��n)�ڣ��������� �I(l��ng)��Ĺ��̎�Ҳ��С L һ�Ӽ��뵽 FPGA �W(xu��)��(x��)��(y��ng)�ô�܊�С�δ�����S�� FPGA �Ѹ����Ӳ���� PowerPC™ ̎ �����ȼ����M(j��n)�����Լ������µĹ�ˇ���惦(ch��)��Ԫ���ɣ�F(xi��n)PGA Խ��Խ�ɞ�һ�N�ں�̎�����惦(ch��)���ӿ���һ�w�� ����(j��)оƬ����FPGA ��(hu��)�ɞ�һ�N�弉(j��)оƬ��δ������Ӯa(ch��n)Ʒ����ͨ�^���� FPGA �팍(sh��)�F(xi��n)���ܵ�����(j��)����(sh��)�H�ϣ�ij Щͨ���O(sh��)��S���ѽ�(j��ng)�ڇLԇ�@�����ˡ���ِ�`˼��˾ȫ���Y����Ü������@��ָ������������δ����F(xi��n)PGA �_�l(f��)������(du��)���̎����Ԍ��ɞ���� C �Z�ԵĻ��A(ch��)����֮һ���挦(du��)�@�ӵİl(f��)չڅ��(sh��)����߀�ܺ�(ji��n)�ε،� FPGA ��(d��ng)�� һ�N߉�����߀�܌�(du��) FPGA �İl(f��)չ�o��(d��ng)���Ԇ

��Ӯa(ch��n)Ʒ�O(sh��)Ӌ(j��)څ��(sh��)��׃��

����Ӯa(ch��n)Ʒ�Q��֮������Ӯa(ch��n)Ʒ�_�l(f��)���̺ͷ������S�����Ԫ�����IJ������M(j��n)��׃�������������ӹ� ���������w���ٵ������·�����̎����O(sh��)Ӌ(j��)�a(ch��n)Ʒ�r(sh��)�������õĹ��ߺͷ�����������ͬ�����ǿ��ā��f؞����� �O(sh��)Ӌ(j��)�Ľy(t��ng)һ˼·�� ��ʹ��ӡˢ�·���ϵķ������F(xi��n)��Ԫ�����B������ IC ��(chu��ng)������ƽ�_(t��i)��(sh��)�F(xi��n)����Ҫ�Ĺ��ܡ����磬 �� 60 ��������Ҫ�O(sh��)Ӌ(j��)һ��(g��)�����C(j��)�����̎����ͨ�^�� PCB ����ͨ�^���w�ܡ���衢��ݡ�늸С�늾����V ���������O�ܵ��·���һ��(g��)����ƽ�_(t��i)����(sh��)�F(xi��n)��(du��) RF ��̖(h��o)���{(di��o)�C���V�����Ŵ�ȣ����(sh��)�F(xi��n)�����C(j��)�Ĺ��ܡ��� ���·���F(xi��n)�Ժ�һЩ�������������ɵ�һ�wоƬ�ϣ����ǿ����O(sh��)Ӌ(j��)˼·�]��׃����߀��Ҫ��һ��(g��) PCB ����ͨ �^�oԴ������ IC ���һ��(g��)����ƽ�_(t��i)����(sh��)�F(xi��n)��̖(h��o)�Ľ��ա�̎����ݔ�������ǣ��S�� FPGA �ȿɾ����������Q���� �O(sh��)Ӌ(j��)˼·���l(f��)�������׃�������S������ķ��������Ƶ��ɾ����I(l��ng)���N��ͬ���O(sh��)Ӌ(j��)���̽��R����һ �𡣬F(xi��n)�ڣ���Ч������O(sh��)Ӌ(j��)�nj��忨�O(sh��)Ӌ(j��)���ɾ���߉�O(sh��)Ӌ(j��)��ܛ���_�l(f��)�ں���һ��δ�����S�� FPGA �ں�̎ �����惦(ch��)��һ�w���忨�O(sh��)Ӌ(j��)���ں��M(j��n)�ɾ���߉�O(sh��)Ӌ(j��)�У���Ӯa(ch��n)Ʒ�O(sh��)Ӌ(j��)����׃?y��u)�ɾ���߉�O(sh��)Ӌ(j��)��Ƕ��ʽܛ�� �O(sh��)Ӌ(j��)���Ǖr(sh��)������O(sh��)Ӌ(j��)�����w�F(xi��n)һ�N��ܛ���O(sh��)Ӌ(j��)��һ�Nͨ�^�_�l(f��)�Z�Ժ��ߌ�(sh��)�F(xi��n)���O(sh��)Ӌ(j��)���� FPGA ���ɞ��@�N

��ܛ���O(sh��)Ӌ(j��)���d�w���� FPGA ��ʽ���ڵĵͳɱ�����Ҏ(gu��)ģ�ɾ������������S�r(sh��)�S�ث@�ã��@ʹ�O(sh��)Ӌ(j��)���п��܌���

��ϵ�y(t��ng)���Ĺ��ܶ��D(zhu��n)�Ƶ�ܛ�O(sh��)Ӌ(j��)�У��������@�N�O(sh��)Ӌ(j��)�ă�(y��u)��(sh��)�� �@Щ��ܛ���O(sh��)Ӌ(j��)��(y��u)��(sh��)�����������ױ��o(h��)ϵ�y(t��ng)����ʹ�䲻�����ƻ����̣����̵��O(sh��)Ӌ(j��)�еġ�ܛ��Ԫ�������£�

ʹ�O(sh��)Ӌ(j��)�^�̸����B�m(x��)�ԡ��õĹ������O(sh��)Ӌ(j��)��ܛ�O(sh��)Ӌ(j��)����ه������ָ����Ӳ��ƽ�_(t��i)�����ң��O(sh��)Ӌ(j��)��������KӲ�� ƽ�_(t��i)��(n��i)�^�m(x��)�M(j��n)�У���ʹ�a(ch��n)Ʒ�ѽ�(j��ng)�ƽ��͑�Ҳ��Ȼ���С�����ܛ���O(sh��)Ӌ(j��)���ɞ�����O(sh��)Ӌ(j��)�İl(f��)չ����

��һ�c(di��n)���F(xi��n)��δ������Ӯa(ch��n)Ʒ���������ܻ��͂�(g��)�Ի������ܻ�ֻ��ͨ�^ܛ���팍(sh��)�F(xi��n)����(g��)�Ի��أ���Ҫ ���̎���(ji��n)�ε��ľͿ��w�F(xi��n)��ͬ����ɫ������Ҳ��Ҫ���o(h��)�Լ����O(sh��)Ӌ(j��)�������ƣ�Ҫ�����@�c(di��n)��Ҳ��Ҫ�ɾ���������

ÿ��(g��)���̎���ϣ���ԵĮa(ch��n)Ʒ���h(yu��n)�c����ͬ���c����ͬ����Ҫ�a(ch��n)Ʒ�c��(j��ng)��(zh��ng)�a(ch��n)Ʒ��һ�ӣ�ُ(g��u)�I���x����� �a(ch��n)Ʒ�����x��(j��ng)��(zh��ng)��(du��)�ֵĮa(ch��n)Ʒ�����ǣ���ô�Ӳ���������ȫ���Ј�(ch��ng)�б����c����ͬ�أ�

��Ҫ��ָ����Ӳ�������_(d��)��Ŀ�ģ���?y��n)�F(xi��n)�ڎ�ÿ��(g��)�˶��ܫ@��ͬ�ӵ�оƬ����(d��ng)�F(xi��n)������Ӳ���Ќ�(sh��)�F(xi��n)���� �ι����ܵ��Ј�(ch��ng)�Ěgӭ��ͬ�r(sh��)�������ķ��ƾͳ��F(xi��n)�ˡ�

����Ҫ���a(ch��n)Ʒ�ą^(q��)�e�����ھ������������ϣ����o(h��)�Ѓr(ji��)ֵ�� IP������ʹ��(j��ng)��(zh��ng)��(du��)�ֺ��y��(du��)���M(j��n)�����̡� ���ң���ʹӲ���ѽ�(j��ng)����������a(ch��n)Ʒ�Կ���ͨ�^��ܛ���O(sh��)Ӌ(j��)�M(j��n)�Є�(chu��ng)�²���a(ch��n)Ʒ��ֵ���a(ch��n)Ʒ�ijɹ������˱��ϡ� ���@Щ�����x���_�ɾ����������ɾ��������nj�(sh��)�F(xi��n)��ܛ���O(sh��)Ӌ(j��)�ı��Ϻ��d�w��

����O(sh��)Ӌ(j��)���̎��O(sh��)Ӌ(j��)�������O(sh��)Ӌ(j��)��(n��i)���ڲ���׃��

����O(sh��)Ӌ(j��)���̎����O(sh��)Ӌ(j��)�����̓�(n��i)���䌍(sh��)Ҳ��һֱ׃������ӹܕr(sh��)�����O(sh��)Ӌ(j��)���̎�Ҫ������ӹܵ����ܺ��O(sh��) Ӌ(j��)Ҫ�c(di��n)�����w�ܕr(sh��)�����O(sh��)Ӌ(j��)���̎�Ҫ��Ϥ�����·�����úʹ�������·�Q���Ժ��O(sh��)Ӌ(j��)���̎�Ҫ��Ϥ IC �� �_�����ú��ܣ����O(sh��)Ӌ(j��)���ߏ�����IJݸ�D��ܛ���o���O(sh��)Ӌ(j��)Ҳ�l(f��)չ������O(sh��)Ӌ(j��)�Ԅ�(d��ng)������ (EDA ܛ�� )���� FPGA ������Ŀɾ��������Q�����O(sh��)Ӌ(j��)���̎�����Ҫ�O(sh��)Ӌ(j��)Ӳ���·��Ҫ��Ϥ HDL��Verilog �� IC �O(sh��)Ӌ(j��)�Z�ԣ����⣬ ߀Ҫ��Ϥ�ӿڡ���(sh��)����̖(h��o)̎�����㷨��EDA �O(sh��)Ӌ(j��)�����W(xu��)�ȵȣ���ӹ��̎�Ҫ�W(xu��)��(x��)��֪�R(sh��)�������ࡣ

δ����Ӳ�����̎���ʲô�ӵģ�

��ô��δ���ĵ�Ӳ���O(sh��)Ӌ(j��)���̎���ʲô�ӵģ������fδ����Ӳ���O(sh��)Ӌ(j��)���������ӵģ������@���f ���� VHDL ���� Verilog �Z�ԁ����_(d��)�O(sh��)Ӌ(j��)��D���� FPGA ����Ӳ���d�w����Ӌ(j��)��C(j��)���O(sh��)Ӌ(j��)�_�l(f��)���ߣ��� EDA ܛ���� �_�l(f��)�h(hu��n)������ SoC��IP �Ȟ�C���O(sh��)Ӌ(j��)�ķ������ѽ�(j��ng)�ɞ�Ӳ���O(sh��)Ӌ(j��)���̵���Ҫ�����������A(y��)Ҋ��F(xi��n)PGA ���ɞ�δ ����Ӳ�����̎����õ��O(sh��)Ӌ(j��)Ԫ��֮һ��

���⣬F(xi��n)PGA �ڑ�(y��ng)���е������@����(y��u)��(sh��)�ǿ��Ԝp�� BOM ���϶���(g��)�����Ĕ�(sh��)������ ( ����һ��(g��)��С�ܱ��˵� CPLD ������Q�Îׂ�(g��) 74 ϵ��оƬ )������ PCB �����y�� (MGT/GTP �ȴ����հl(f��)����ԭ���c��Ҫ����ʮ�l���� �Д�(sh��)��(j��)����Q�������Ĵ��о�· )���ɶ����� ( �����Լ������a��֧�ַǘ�(bi��o)��(zh��n)�Ľӿ� )���ɔU(ku��)չ�� ( �ɾ������� �ķ�������(j��) )���������Еr(sh��)�g ( ֻ���P(gu��n)�Ĺ��܌�(sh��)�F(xi��n)������Ҫ�ٻ��r(sh��)�g�ƳɌ��� IC) �ȣ��@�� FPGA ���o�O(sh��)Ӌ(j��)�Ĺ� ˾�ĺ�̎�ѽ�(j��ng)���Ǐijɱ��w�F(xi��n)�ˣ������Դ���������_�l(f��)��Ч�ʣ�

�C���������҂������מ�ʲô���̎�Ҫ���� FPGA �_�l(f��)֪�R(sh��)�ˣ�ϣ�����������ڴ���˽������ FPGA �_�l(f��)��

�ڶ��¡�FPGA����֪�R(sh��)�c�l(f��)չڅ��(sh��)

FPGA ��Ӣ�� Field Programmable Gate Array �Ŀs�������F(xi��n)��(ch��ng)�ɾ����T��У������� PAL��GAL��CPLD �ȿɾ��������Ļ��A(ch��)���M(j��n)һ���l(f��)չ�Įa(ch��n)��������錣�ü����· (ASIC) �I(l��ng)���е�һ�N�붨���·�����F(xi��n)�ģ� �Ƚ�Q�˶����·�IJ��㣬�ֿ˷���ԭ�пɾ��������T�·��(sh��)����ȱ�c(di��n)�����Ǯ�(d��ng)��(sh��)��ϵ�y(t��ng)�O(sh��)Ӌ(j��)����ҪӲ�� ƽ�_(t��i)������Ҫ���c(di��n)������ȫ���Ñ�ͨ�^ܛ���M(j��n)�����ú;��̣��Ķ����ij�N�ض��Ĺ��ܣ��ҿ��Է���(f��)�������� �ĺ�����(j��)�r(sh��)�������~��ظ�׃ PCB �·�壬ֻ����Ӌ(j��)��C(j��)���ĺ��³���ʹӲ���O(sh��)Ӌ(j��)�����ɞ�ܛ���_�l(f��) �������s����ϵ�y(t��ng)�O(sh��)Ӌ(j��)�����ڣ�����ˌ�(sh��)�F(xi��n)���`���Բ������˳ɱ�����˫@���ˏV��Ӳ�����̎�����A��

2.1 FPGA �Y(ji��)��(g��u)����ԭ��

2.1.1 ��(m��ng)��ɾ͂��I(y��)

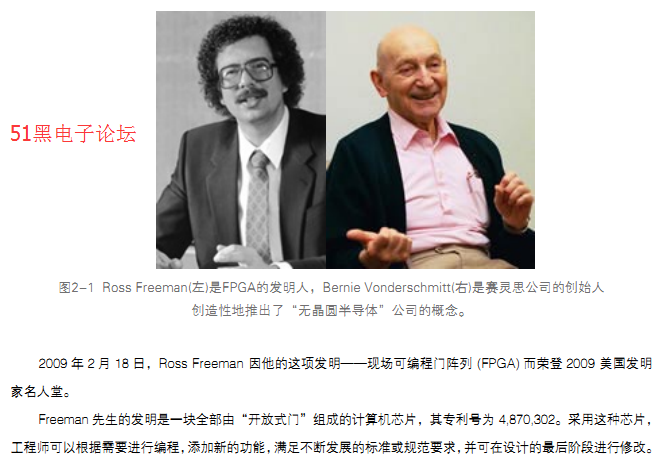

1984 �꣬�ڹ�ȹ����� Bernie Vonderschmitt��Ross Freeman �� Jim Barnett ��ͬ��(g��u)����һ��(g��)�O(sh��)�룬���� ��(m��ng)�넓(chu��ng)��һ�Ҳ�ͬ��һ��Ĺ�˾������ϣ����(chu��ng)��һ��������(g��)���I(l��ng)���(n��i)�_�l(f��)���Ƴ����M(j��n)���g(sh��)�Ĺ�˾�����ң����� ߀ϣ�����@�N��ʽ�I(l��ng)��(d��o)�� �����@�﹤�����˂���������Ĺ��������ܹ����Ę�Ȥ������(du��)���������µĹ������ԡ�

������pdf��ʽ�ęn51�����d��ַ����114퓣���

FPGA�_�l(f��)ȫ����.pdf

(4.84 MB, ���d��(sh��): 108)

FPGA�_�l(f��)ȫ����.pdf

(4.84 MB, ���d��(sh��): 108)

2018-9-9 21:12 �ς�

�c(di��n)���ļ������d����

|

|

����TQQ:125739409;���g(sh��)����QQȺ281945664

����TQQ:125739409;���g(sh��)����QQȺ281945664