HW3000射頻芯片資料

目錄

內容目錄

第 1 章 原理圖參考設計4

11 兩種結構電路的原理圖 4

12 兩種結構電路外圍元件 BOM5

13 不同頻率下的射頻元件 BOM6

第 2 章 PCB 參考設計 7

第 3 章 制版工藝9

第 4 章 性能測試10

41 功率測試10

42 靈敏度測試 10

圖目錄

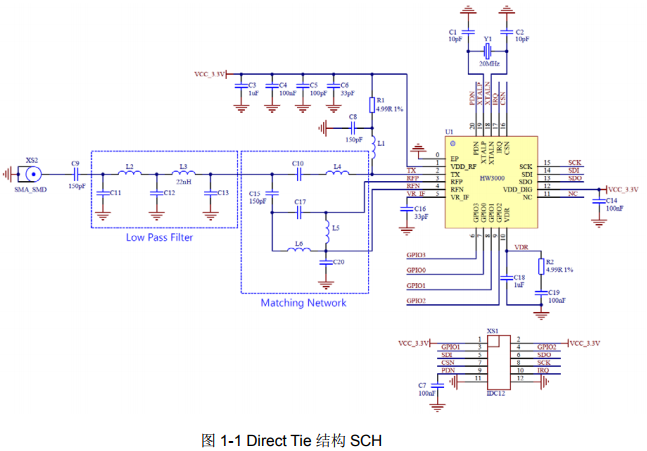

圖 1-1 Direct Tie 結構 SCH 4

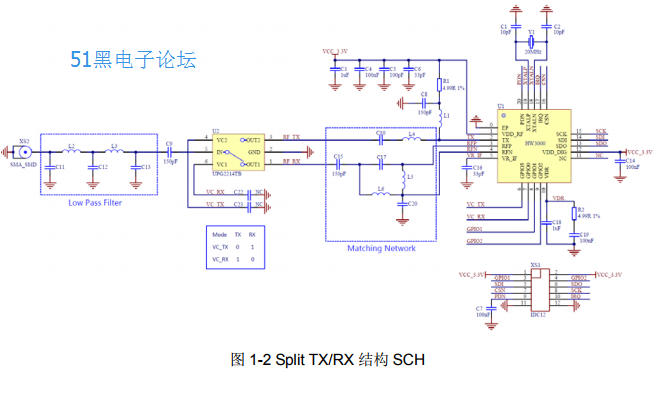

圖 1-2 Split TX/RX 結構 SCH 4

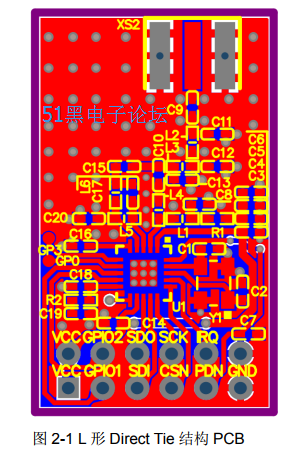

圖 2-1 L 形 Direct Tie 結構 PCB 7

圖 2-2 一字形 Direct Tie 結構 PCB8

圖 2-3 一字形 Split TX/RX 結構 PCB8

表目錄

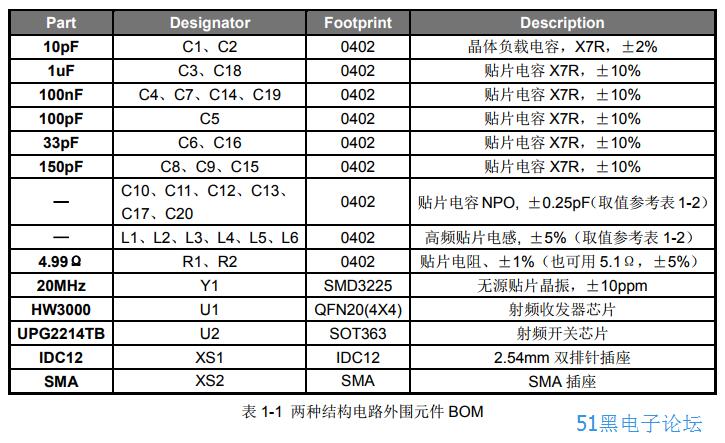

表 1-1 兩種結構電路外圍元件 BOM 5

表 1-2 不同頻率下的射頻元件 BOM 6

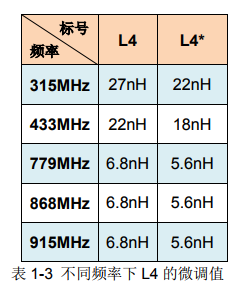

表 1-3 不同頻率下 L4 的微調值6

表 3-1 PCB 制版工藝參數 9

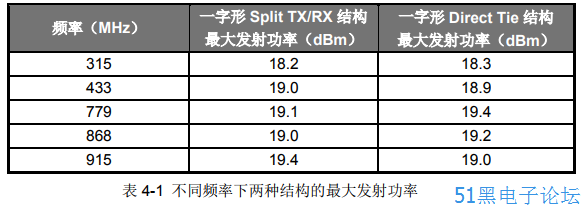

表 4-1 不同頻率下兩種結構的最大發射功率10

表 4-2 不同頻率下 Direct Tie 結構的接收靈敏度 10

表 4-3 不同頻率下 Split TX/RX 結構的接收靈敏度 11

第 1 章 原理圖參考設計

1.1 兩種結構電路的原理圖

HW3000 EVB 原理圖參考設計有兩個方案,圖 1-1 采用的是 Direct Tie 結構,收發射頻匹配網絡之間直連,其優點是電路簡單。圖 1-2 采用的是 Split TX/RX 結構,收發射頻匹配網絡和射頻開關芯片連接,通過開關來切換收發模式,其優點是性能較好,但增加了元器件,成本稍高。

這兩種結構的共同電路包括:晶體振蕩電路、TX/RX 匹配網絡、低通濾波器和電源濾波電路。

Direct Tie 結構與 Split TX/RX 結構的最大不同之處在于,去除了射頻開關電路,減少了電路的復雜度。

振蕩電路支持 20MHz、26MHz 無源晶體,C1、C2 是晶體負載電容,其參數將影響晶體振蕩頻率,請參考晶體具體規格來選擇。根據應用需求的不同,推薦用戶選擇頻率穩定度≥±10ppm 的晶振。選取原則如下:無源晶體精度越高,無線設備之間載波頻偏將越小,遠距離通信成功率將顯著提高。因此遠距離應用請盡量選用高精度無源晶體。

射頻網絡包括阻抗匹配網絡(Matching Network)和低通濾波器(Low Pass Filter)兩部分。

其中低通濾波器是發射(TX)和接收(RX)共用,阻抗匹配網絡則分成 TX 和 RX 兩部分。對于Direct Tie 結構,TX 和 RX 阻抗匹配網絡直接通過 C15 電容連接。而對于 Split TX/RX 結構,TX 和RX 阻抗匹配網絡與射頻開關芯片的兩個端子連接,第三端和低通濾波器網絡相連。阻抗匹配網絡實現射頻收發器芯片內部阻抗到外圍 50 歐姆阻抗的變換。低通濾波器采用 LC 低通濾波電路,用于濾除有用信號以外的高頻干擾雜波。射頻網絡的元件選型對通信將產生很大影響,推薦選用高頻器件。需要注意的是,不同收發頻率下的射頻網絡元件的取值是不同的(具體參考表 1-2)。外圍電源濾波電路均為 HW3000 射頻收發器芯片電源的濾波,不同大小值的電容用于濾除電源上不同頻率的干擾雜波,以保證芯片能夠穩定的工作。

1.2 兩種結構電路外圍元件BOM

兩種結構 EVB 板的外圍元件基本相同,下面給出外圍元件的 BOM。

1.3 不同頻率下的射頻元件BOM

由于 HW3000 支持多個頻率,不同頻率下的射頻元件(包括低通濾波網絡元件和匹配網絡元件)的值是不相同的。下面給出不同頻率下的射頻元件 BOM。

注:L4 的取值,會因為 PCB 布局布線的影響,其最佳值會發生變化,可以根據情況細微調整,推薦的 L4 調整值列表如下:

一般情況下,對于射頻元件比較緊湊的 L 形布局(如圖 2-1 的布局方式),建議按照 L4 取值(第一列)。相對比較分散的一字形布局(如圖 2-2 和圖 2-3 的布局方式),建議取值為 L4*(第二列)。

第 2 章 PCB參考設計

PCB 設計采用低成本雙面板即可滿足設計要求,下面給出兩類不同類型的 PCB 布局參考設計。對于 PCB 空間比較緊張的情況,射頻元件可以采用 L 形布局,如圖 2-1 的 L 形 Direct Tie 結構。對于 PCB 空間比較充足的應用,射頻元件可以采用一字形布局,如圖 2-2 的一字形 Direct Tie 結構和

2-3 的一字形 Split TX/RX 結構。PCB 設計的注意事項如下:

所有元器件均布局在雙面板正面,背面盡量提供完整的參考地平面;射頻走線應盡可能短;

兩個電感互連推薦采用 L 形布局,減小互感;其它的射頻元件,最優采用一字形布局,次優采用 L 形布局,不推薦 U 形或者 Z 形布局。

L5 連接芯片管腳 RFP、RFN 的走線是差分線,請盡量平行、等長布線,以保證差分性能;

所有射頻電路應該“包地”,接地鋪銅要通過盡量多的過孔與底層參考地平面連接,以降低接地阻抗;

數字電路和晶振電路請盡量遠離射頻前端電路;

若電源與數字部分需走背面,需盡量減小分割地平面,并且盡量遠離射頻前端;

去耦電容需要盡可能靠近芯片電源管腳,以獲得更好的濾波效果。

射頻走線寬度和鋪銅間距,可參考第 3 章《制版工藝》。

下面給出三種 PCB 參考設計,一種 L 形布局,兩種一字形布局。

第 3 章 制版工藝

由于高頻信號的存在,在 RF PCB 制版過程中需要考慮 PCB 工廠的阻抗控制參數。下面給出

的是本參考設計的制版工藝參數。

注:為保證射頻走線為 50 歐姆,可以根據不同板厚,按照如下參數進行調整。以下結果為 Si9000仿真值,僅供參考。仿真假設 FR4 的介電常數為 4.3、綠油介電常數為 4.2,這些參數對仿真結果影響較大,具體參數請與 PCB 廠家確認后自行仿真。如果需要更加準確的結果,則需要 PCB 廠家進行阻抗控制。(1)若射頻走線采用 20mil 線寬:板厚為 1.0mm 時,接地鋪銅與走線間距為 5.3mil板厚為 1.2mm 時,接地鋪銅與走線間距為 5.1mil板厚為 1.6mm 時,接地鋪銅與走線間距為 5mil(3)若射頻走線采用 25mil 線寬:板厚為 1.0mm 時,接地鋪銅與走線間距為 6.3mil板厚為 1.2mm 時,接地鋪銅與走線間距為 6mil板厚為 1.6mm 時,接地鋪銅與走線間距為 5.7mil(3)若射頻走線采用 30mil 線寬:板厚為 1.0mm 時,接地鋪銅與走線間距為 7.6mil板厚為 1.2mm 時,接地鋪銅與走線間距為 7.1mil板厚為 1.6mm 時,接地鋪銅與走線間距為 6.6mil

第 4 章 性能測試下面以一字形布局的 HW3000 EVB 模塊為例,給出實際性能測試結果。

4.1 功率測試測試儀器:信號分析儀 EXA Signal Analyzer N9010A (10Hz-7GHz)測試條件:SPAN=10MHz、RBW=1MHz、VBW=10MHz下表是兩種結

構在不同頻率下的最大發射功率(典型值)。

4.2 靈敏度測試

測試儀器:矢量信號發生器 MXG Vector Signal Generator N5182A(100KHz-3GHz)

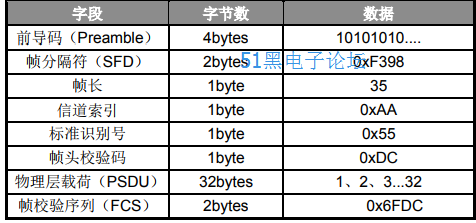

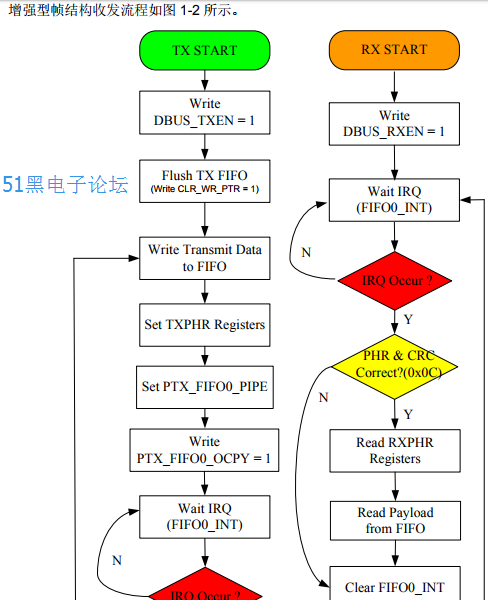

測試數據包格式:數據包的幀格式為增強型幀結構,具體格式如表 4-3 所示。

測試方法:通過調節信號發生器的輸出功率。控制板通過外部觸發接口,控制每次發送 100 個數據包。接收板能接收到的數據包(>90 個包)時,記錄信號發生器的輸出功率最小值,即為接收靈敏度。下面兩個表格,分別是兩種結構,在不同頻率、不同速率下的接收靈敏度。

目 錄

內容目錄

第 1 章 編程說明4

11 工作模式4

12 初始化4

13 數據包收發 4

131 增強型幀結構模式 4

132 直接 FIFO 幀結構模式8

14 ACK 功能應用12

15 單載波發送 CW 模式 14

16 直接收發 DIRECT 模式 14

第 2 章 寄存器初始化15

21 12kbps 速率配置 15

22 10kbps 速率配置 16

23 50kbps 速率配置 17

24 100kbps 速率配置 18

25 頻段設置說明19

26 26MHz 晶振使用說明 20

第 3 章 RF 測試說明 21

31 PA 功率21

32 RSSI 22

第 4 章 芯片故障分析23

第 5 章 常見問題24

第 1 章 編程說明

1.1 工作模式

HW3000 芯片主要有 POWER DOWN、DEEP SLEEP、SLEEP、IDLE、TX、RX 六個工作模式,各個工作模式之間的切換見芯片數據手冊的“芯片狀態控制”章節內容。

1.2 初始化

芯片上電等待時間約 2ms

全芯片復位(0x61)

寄存器初始化配置(以下配置不分先后)

射頻前端寄存器初始化,詳見本文“寄存器初始化設置”章節

速率 SYMBOL_RATE 設置(0x32、0x33),默認 10Kbps

外部晶振參考頻率 CFG_XTCS(0x25)設置,默認為選擇 26MHz 晶振

頻點 RF_FREQ_BASE、CH_SPACE 設置(0x2F)

幀結構配置 PACK_LENGTH_EN(0x02)

Preamble 長度、Syncword 長度、編碼方式、是否支持 FEC、是否支持白化功能等設置(0x02、0x03)

若選擇直接 FIFO 幀結構模式,配置發送完成 LEN0_TXMODE 與接收完成模式LEN0_RXMODE(0x02)

使能通訊使用的 PIPE、設置 PIPE 地址、以及該 PIPE 是否支持 ACK 功能(0x13、0x15~0x1A)

若支持 ACK 模式,設置重發次數 RE_TX_TIMES(0x45,設置值需大于‘0’ )注:直接 FIFO 幀結構模式不支持 ACK、FEC 功能,可忽略相應寄存器配置步驟。

1.3 數據包收發

HW3000 收發支持增強型與直接 FIFO 兩種幀結構模式,可通過寄存器 PACK_LENGTH_EN

配置。

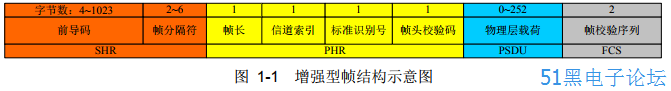

1.3.1 增強型幀結構模式

增強型幀結構模式需設置 PACK_LENGTH_EN 為‘1’,該模式幀結構如圖 1-1 所示。

幀長配置

發送端可通過 AUTO_LEN_CALC(0x09)寄存器配置發送幀長信息由硬件自動生成或由軟件填寫。若設置 AUTO_LEN_CALC 為‘1’,硬件自動依據發送 FIFO 內所填寫的 PSDU 字節數加上 3(即加上信道索引、標準識別號、幀頭校驗碼所占的 3 個字節)作為發送幀的幀長信息。若設置 AUTO_LEN_CALC 為‘0’,芯片在發送之前需由軟件將 PSDU 的長度信息填寫至TXPSDU_LEN(0x09)寄存器,硬件依據 TXPSDU_LEN 寄存器的值加上 3(即加上信道索引、標準識別號、幀頭校驗碼所占的 3 個字節)作為發送幀的幀長信息。接收端將成功接收的數據幀幀長信息存放于 RX_PHR_PSDU_LEN(0x0A)寄存器。

信道索引發送端需在發送之前將信道索引填寫至 TX_PHR_CHANNEL_INDEX(0x08)寄存器。接收端將成功接收的數據幀信道索引存放于 RX_PHR_CHANNEL_INDEX(0x0A)寄存器。

標準識別號發送端需在發送之前將標準識別號填寫至 TX_PHR_STD_IDEF(0x08)寄存器。接收端將成功接收的數據幀標準識別號存放于 RX_PHR_STD_IDEF(0x0B)寄存器。

幀頭校驗發送端可通過 AUTO_PHR_VERIFY(0x07)寄存器配置幀頭校驗信息由硬件自動生成或由軟件生成。若設置 AUTO_PHR_VERIFY 為‘1’,硬件依據發送幀長、信道索引、標準識別號 3 個字節自動生成校驗碼作為發送幀的幀頭校驗信息。若設置 AUTO_PHR_VERIFY 為‘0’,芯片在發送之前需由軟件填寫 TX_PHR_VERIFY(0x07)寄存器,硬件依據 TX_PHR_VERIFY 寄存器的填寫值作為發送幀的幀頭校驗。接收端將成功接收的數據幀幀頭校驗信息存放于 RX_PHR_VERIFY(0x0B)寄存器。

物理層載荷(PSDU)PSDU 部分存放于 FIFO 中,增強型幀結構模式下最大長度支持 252bytes。

幀校驗序列(FCS)發送端可通過 LEN1_CRCSEL(0x02)寄存器配置幀校驗序列由硬件自動生成或由軟件生成。若設置 LEN1_CRCSEL 為‘0’,硬件自動生成幀校驗序列。若設置 LEN1_CRCSEL 為‘1’,芯片在發送之前需由軟件填寫 CRCVAL(0x12)寄存器,硬件依據 CRCVAL 寄存器的填寫值作為發送幀的幀校驗序列。接收端將成功接收的數據幀幀校驗序列存放于 CRCVAL 寄存器。

注:ACK 功能使能時不支持幀頭校驗軟件生成模式與幀校驗序列軟件生成模式。

芯片支持 FIFO 數據包重復發送功能,以滿足某些數據包重復發送或快速跳頻等應用場合,可以有效減少主控 MCU 的軟件開銷(如圖 1-3 所示)。用戶可在再次使能發送之前插入延時控制重發時間間隔或更改發送頻點。

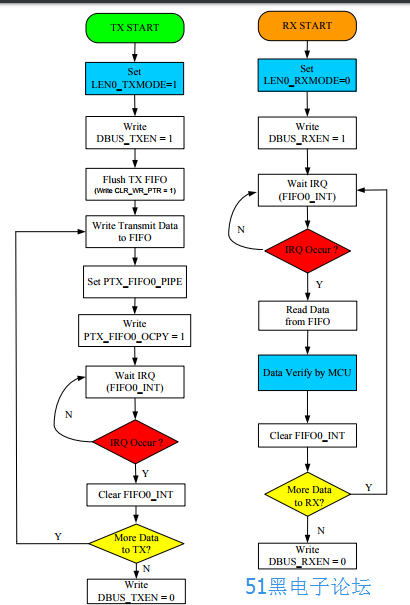

1.3.2 直接FIFO幀結構模式

直接 FIFO 幀結構模式需設置 PACK_LENGTH_EN 為‘0’,該模式幀結構如圖 1-4 所示。此模式不支持 ACK、硬件 CRC 校驗與 FEC 功能。發送除 PREAMBLE 與 SFD 部分都需軟件填寫至 FIFO 內,填寫內容與順序可依據收發雙方的約定靈活設置。直接 FIFO 模式下發送可依據 LEN0_TXMODE 控制位配置發送完成模式,接收可依據LEN0_RXMODE 控制位配置接收完成模式,詳見 0x02 寄存器相關說明。

直接 FIFO 幀結構模式下芯片提供接收長度自動識別功能,設置詳見《HW3000_Datasheet_C》

8.2 章節描述。

若收發長度小于等于 256bytes,且設置 LEN0_TXMODE 及 LEN0_RXMODE 為芯片自動識別接發長度,其收發流程如圖 1-5 所示。

若收發長度小于等于 256bytes,且 LEN0_RXMODE 設置為軟件設置接收長度,假設收發約定FIFO 內第一個 byte 代表包長度信息,其接收流程如圖 1-6 所示。接收使能之前,先設定一較小的半滿閾值,確保半滿中斷置起時可從 FIFO 內指定位置讀取接收長度,軟件獲取接收長度后需配置 LEN0_PKLEN 寄存器,硬件依據 LEN0_PKLEN 寄存器的設定值自動完成接收。

建議在接收使能之前配置 LEN0_PKLEN 為一較大值,防止軟件處理過慢出現 FIFO0_INT 誤中斷。

圖 1-6 直接 FIFO 幀結構軟件設置包長接收流程示意圖

若收發長度大于 256bytes 時,軟件需依據 FIFO 的半空或半滿中斷標志,完成對 FIFO 的寫入與讀取操作,配合物理層硬件完成對 FIFO 內數據的發送與接收。假設收發約定 FIFO 內第一個 byte 代表包長度信息,LEN0_RXMODE 設置為接收自動識別包長信息,其收發流程如圖 1-7 所示。

PRX 在接收使能之前可設定一較小的半滿閾值 FULL_THRES,保證響應 HALF_FULL_INT 中斷時軟件可從 FIFO 內即時獲取接收包長信息,根據接收包長信息再由軟件調整半滿閾值FULL_THRES 以簡化接收操作流程。

注:可通過 EMPTY_THRES,FULL_THRES 寄存器設置半空半滿閾值,設置值需考慮 SPI 接口的訪問速度與芯片配置的數據速率。

1.4 ACK功能應用

ACK 應用僅針對增強型幀結構模式,功能介紹詳見《HW3000_Datasheet_C》第 5 章說明,

ACK 使能情況下收發流程如圖 1-8 所示。

若使能 PIPE0 ACK 功能(P0_ACKEN = ‘1’),PTX 在接收 ACK 等待時間 AUTO_RXACK_TIME(0x45)內沒有成功接收到 PRX 發送的 ACK 幀,PTX 將自動重傳上一幀數據包。PTX 讀取中斷 FIFO0_INT 之后需檢查 FIFO0_MAX_RETX(0x0F)標志位,以判斷中斷源為 PTX 接收ACK 成功或是重傳超時。

PRX 在 ACK 使能情況下接收 PHR 校驗出錯或 CRC 出錯將進入自動重收流程,FIFO0_INT 中斷標志位置起后軟件無需再檢測 PRX_PHR_ERR 與 PRX_CRC_ERR 標志位。

第 4 章 芯片故障分析

如果兩顆芯片不能進行正常收發通訊,首先應該將這兩顆芯片分別與已測試過的正常芯片進行收發通訊,確定發射芯片還是接收芯片出現問題。在此前提下,可參照以下內容分析芯片發送或接收故障的原因。

檢查芯片供電是否正常

上電后芯片默認進入 IDLE 模式,芯片 VDR 引腳輸出電壓 1.8V 左右。

檢查晶振是否正常工作

上電后測試晶振 XTALP 或 XTALN 引腳,觀察是否有信號,信號頻率是否正確,若有異常可能

是晶振損壞或使用的起振電容不合適。

檢查 SPI 讀寫是否正常

對寄存器進行讀寫操作檢查 SPI 驅動程序是否正確。如果寄存器寫入與讀取值不一致,利用示波器抓取 SPI 讀寫波形,檢查 SPI 四根線的電平是否正確,波形時序是否和產品手冊一致;檢查 SPI 通訊速率是否小于給定的最大通訊速率。

軟件檢查

檢查軟件對 HW3000 芯片的寄存器初始化配置是否與參考代碼有差異,軟件收發流程是否與操

作例程有差異。

檢查通訊頻段有無干擾

將 Sub-1GHz 天線連接到頻譜儀,直接測空間輻射的信號,如在通訊頻點有較大空間干擾,建議避開此頻點通訊。

單載波發送模式

使能單載波發送模式,觀察發射頻點是否鎖定,與設置值是否一致。

檢查收發頻偏

檢查兩顆芯片的收發頻偏值是否小于 30kHz(測量值頻率與理論值頻率之間的偏差),頻偏補償方法詳見 HW3000 芯片數據手冊的“AFC 及晶振校準功能”章節。

檢查接收本振是否鎖定

判斷接收本振是否鎖定需要使用頻譜儀觀察,設置頻譜儀 Span=250kHz,Ref

Amplitude=-50dBm。使能接收,如果接收頻點一直停留在接收設定頻點*8 位置不跳動,就說

明已鎖定。

晶振頻偏調整

調整晶振外接的兩個電容,如果調整以后的晶振頻率值一致性仍很差,則需要更換晶振,提高

晶振精度 ppm。

第 5 章 常見問題

芯片發送或接收頻點為什么與設置值不一致?

頻點設置需在芯片發送或接收狀態有效之前完成,否則芯片內部 PLL 將無法正確鎖定。

寫指針在什么時候需要軟件清‘0’?

芯片內狀態機寫 FIFO(只出現在 PRX 端)的指針與 SPI 寫 FIFO(只出現在 PTX 端)的指針復用同一個指針。PTX 與 PRX 在正常收發不切換時,硬件在合適情況下自動清零寫指針,無需軟件參與,但在收發角色切換(PRX 切換為 PTX)寫指針主控權發生變化時,需要軟件參與在 SPI 寫 FIFO 前將寫指針清‘0’。

收發 ACK 使能時為什么 PTX 發送中斷正常置起而 PRX 接收無正常中斷?

ACK 使能時,PTX 發送方中斷置起分兩種情況:

1. PTX 正常收到 ACK 幀,通訊成功。

2. PTX 重傳超時,通訊不成功。

PTX 中斷置起后可以通過 FIFO0_MAX_RETX 標志位區分兩種情況。

ACK 使能時,PRX 在接收 PID 與 CRC 較上一次相同時將自動棄包而不置起中斷。若 PTX 出現重傳超時,PTX 在下一次發送幀時 PID 不累加。

為什么 PRX 接收 CRC 正確,但接收 FIFO 的讀取值與 PTX 發送 FIFO 內填寫值不一致?

1. PTX 在寫 FIFO 時有可能 SPI 受到干擾而誤寫,按寫入 FIFO 的值硬件自動生成 CRC,PRX

收到誤寫的值將出現上述現象。

2. PRX 在讀 FIFO 時 SPI 受到干擾而可能造成誤讀。

為什么收發雙方 PIPE Address 配置一致時,會出現 PRX 的 PIPE 指示位(PRX_FIFO0_PIPE)所指示的 PIPE 與發送使用的 PIPE 不一致的現象?

各 PIPE Address(0x14~0x1A)設置值之間的碼間距需大于接收同步字允許錯誤個數閾值SYNC_THRES,否則接收各 PIPE 容易出現誤同步。

目 錄

內容目錄

第 1 章 SPI 接口4

11 SPI 幀格式和通訊時序4

12 SPI 讀寫函數原型4

13 HR7P 系列 MCU SPI 匯編驅動5

第 2 章 程序設計示例14

21 HW3000 復位功能區別14

22 HW3000 默認寄存器初始化 14

23 數據載荷說明18

24 HW3000 TX 測試波形 18

25 HW3000 TX 數據20

26 HW3000 RX 數據 23

27 HW3000 RSSI 說明26

28 HW3000 狀態查詢模式特別說明26

29 HW3000 FIFO 數據在發射完成后將駐留26

210 HW3000 AFC 及晶振的校準功能 26

第 2 章 程序設計示例

以下為 HW3000 芯片常用收發程序示例。

2.1 HW3000 復位功能區別

芯片從 POWER DOWN 狀態恢復至 IDLE 狀態過程中內部 POR 將復位全芯片(通過設置 PDN輸入引腳為高電平進入 POWER DOWN 狀態)。

芯片從 DEEP SLEEP/SLEEP 恢復至 IDLE 狀態,芯片除配置寄存器外將全部被復位(注意寄存器中的狀態指示位將被復位)。

芯片共提供兩種軟復位方式,分別為 SFT_RST0(0x60)和 SFT_RST1(0x61),其中:

1) SFT_RST0 復位硬件電路與 FIFO 而保留原有的寄存器設置值

2) SFT_RST1 進行全芯片復位,寄存器同時也會被復位成默認值

2.2 HW3000 默認寄存器初始化

HW3000 內部寄存器分為 Bank0 和 Bank1 兩部分,其中 Bank0 是面向用戶開放功能寄存器,Bank0 寄存器由用戶根據功能進行設置;Bank1 是內部校準寄存器,Bank1 寄存器僅需用戶在寄存器復位后按照建議值初始化即可。Bank0 和 Bank1 切換方式詳見如下 HW3000 初始化流程,帶宏定義寄存器均為 Bank0 寄存器,hw3000_mode_t 結構體用于演示各種用戶功能模式設置過程。

typedef struct {

osc_mode_t osc; //osc selection

frequency_band_t band; //freq band setting

symbol_rate_t rate; //data rate setting

frequency_mode_t freq_mode; //0 only for 433MHz 1 direct mode for all

int8_t power; //tx power set

frame_mode_t frame_mode; //0 fifo mode, 1 frame mode

uint8_t ack_mode; //0 disable, 1 enable

uint8_t tx_mode; //0 tx length by LEN0_PKLEN, 1 by fifo pointer

uint8_t rx_mode; //0 automatic 1 by LEN0_PKLEN

uint8_t lp_enable; //0 low power mode disable, 1 enable

} hw3000_mode_t;

2.3 數據載荷說明

HW3000 收發數據 FIFO 深度為 256,若用戶采用增強型幀結構,用戶可用 FIFO 深度為 252字節,若用戶采用直接 FIFO 模式,通過半空半滿中斷可支持用戶超過 256 字節數據傳輸。

2.4 HW3000 TX測試波形

HW3000 提供單載波、PN9、0101 等數據發送模式,以方便頻點測試與發送功率測試。

2.5 HW3000 TX 數據

Hw3000 支持增強型幀結構發射數據和直接 FIFO 模式發射數據,其中直接 FIFO 模式需要用戶自行完成數據校驗工作,直接 FIFO 模式可實現與市面同類無線芯片的互聯互通。

2.6 HW3000 RX 數據

Hw3000 支持增強型幀結構發射數據和直接 FIFO 模式接收數據,其中直接 FIFO 模式需要用戶自行完成數據校驗工作,直接 FIFO 模式可實現與市面同類無線芯片的互聯互通。

2.7 HW3000 RSSI說明

在接收模式時,芯片會評估天線端接收信號能量的大小,該數值會保存在寄存器 RSSI(0x23)中。RSSI 的讀數單位為 dBm,數據的格式為二進制補碼形式的符號數。在 RSSI 寄存器里提供兩個 RSSI 讀數值,其中 RSSI1 保存的是上一個有效數據包(SFD 正確同步)的 RSSI 計算值,而RSSI2 中保存的是實時的 RSSI 計算值,可用于 CSMA/CA 工作。若需檢測環境能量 RSSI2,建議在 RX 接收使能后至少延時 350us,再進行讀取。另外如果用戶系統 SPI 速率較快,大于 1Mbps 以上,在讀取環境能量前,如有接收使能的關閉、打開操作,在接收使能切換中間必須有一定的延時操作,否則讀取的 RSSI2 值會有跳變現象;同理,如果在讀取 RSSI2 操作前,有發射、接收使能的切換操作,在狀態切換中間必須加一定的延時操作。直接 FIFO 模式下,若讀取上一個有效數據包的 RSSI1 值,必須在 SFD_INT 與 FIFO_INT 之間讀取,即在同步之后,數據接收完成之前讀取,數據接收完成之后, RSSI1 被復位成 0x81。增強型模式下,RSSI1 值會被鎖定,直到下一個有效數據包之后才會被更新,且只有在芯片復位之后,RSSI1 值才會被復位成 0x81。

2.8 HW3000 狀態查詢模式特別說明

當通過 SPI 輪詢方式檢測 HW3000 收發狀態是否完成時,在輪詢相關狀態寄存器時請加入適

當延時,以避免 SPI 通信所產生的高次諧波可能對收發過程產生影響。

采用 IRQ 中斷方式實現收發狀態檢測則無此問題產生。

2.9 HW3000 FIFO數據在發射完成后將駐留

若發射相同數據,可僅寫入 FIFO 一次數據通過清除 INT 中斷方式實現循環發送。

利用該方式可更好實現有源 RFID 功能。

若存在接收數據,發射端 FIFO 將不再保留。

2.10 HW3000 AFC及晶振的校準功能

HW3000 在接收端提供載波頻偏自動補償功能(AFC),可通過 AFC_EN(0x25)寄存器使能

晶振校準寄存器為 XOSC_CAL(0x37),設置值支持 0x00 至 0xFF,步長約 15Hz。

全部資料51hei下載地址:

AN1015_應用筆記_HW3000_Programming_Guide V1.0.pdf

(323.26 KB, 下載次數: 115)

AN1015_應用筆記_HW3000_Programming_Guide V1.0.pdf

(323.26 KB, 下載次數: 115)

|